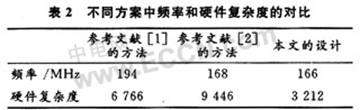

密碼學是保障信息安全的核心技術,應用涉及軍事、國防、商貿及人們日常生活的各個方面。2001 年美國標準技術研究所決定用AES 算法逐漸取代日益不安全的56 bit 密鑰長度的 數(shù)據加密標準(DES)算法。AES算法是迭代分組密碼算法,分組長度為128 bit,而密鑰長度可為128 bit、192 bit、256 bit,其對應不同的密鑰長度相應的迭代循環(huán)次數(shù)為10輪、12輪、14 輪。現(xiàn)實現(xiàn)的是128 bit 的AES算法[1-2]。

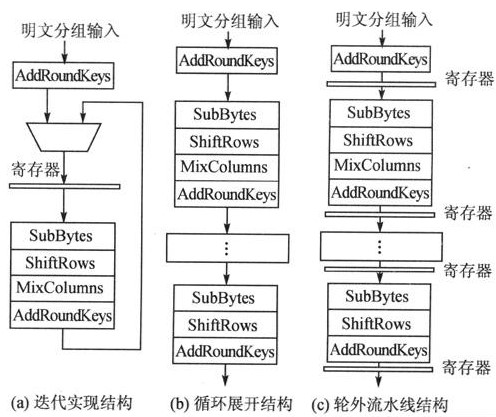

一種AES 算法實現(xiàn)是采用輪展開的流水線結構[3],吞吐量很大可達到10 Gb/s 量級,但消耗大量的邏輯面積。考慮在資源少的FPGA 上實現(xiàn)AES 算法,能滿足低端應用的加、解密速度一般不超過100 Mb/s 的需求。現(xiàn)設計采用順序結構[3],多輪加密共用一個輪運算結構,加密模塊和解密模塊共用一個密鑰擴展模塊,能保持較高加解密速率,同時節(jié)省了邏輯面積,在50 MHz 時鐘下加解密速率可達530 Mb/s。

1 AES 算法描述

AES 算法中的字節(jié)表示為有限域上的元素,并在有限域上定義加法和乘法兩種運算,運算的基本單位是字節(jié)和雙字(4 個字節(jié))。AES 算法將128 位的中間結果和密鑰都分成16 個字節(jié),構成4×4 以字節(jié)為元素的狀態(tài)矩陣,AES在加解密過程中就是以狀態(tài)矩陣為操作對象的。加密算法中每一次輪操作都由字節(jié)替換、行移位、列混淆和輪密鑰加這四個函數(shù)組成,最后一次輪操作不含列混淆操作。

2 在FPGA 上實現(xiàn)AES 算法

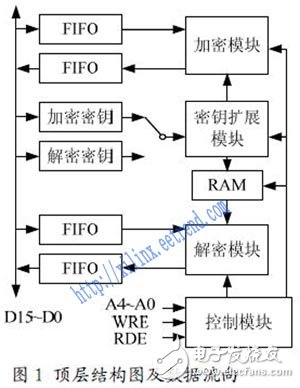

2.1 頂層結構圖

該設計的頂層結構圖如圖1 所示,由控制模塊、加密模塊、解密模塊、密鑰擴展模塊、隨機存儲器(RAM)和FIFO組成。接口采用16 位并行數(shù)據總線結構。加密數(shù)據流向為:明文數(shù)據通過數(shù)據總線寫入16 位入128 位出的FIFO 緩存;由控制模塊啟動AES 加密模塊進行一次加密運算;運算完成輸出128bit 密文存入128 位入16 位出的FIFO 中。解密過程與之相同。加密模塊和解密模塊完全獨立,保證模塊能同時進行加密和解密運算,以滿足快速雙向保密通信的需求。

?

2.2 加解密部分設計

2.2.1 加密模塊

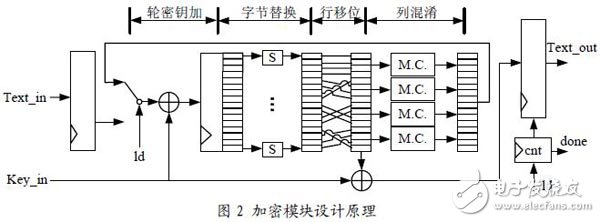

由于輸入8 次16 位數(shù)據才能提供一個128 bit 明文,這一過程至少需要8 個時鐘,因此采用邏輯面積較大的多輪展開流水線結構方式意義不大。該設計采用多輪運算復用一個輪操作結構的順序方式,設計原理圖如圖2 所示。

輪運算包括輪密鑰加、字節(jié)替換、行移位和列混淆4 個部分。其中,輪密鑰加只是輪數(shù)據與輪密鑰進行異或運算,結構比較簡單;行移位也只是簡單的邏輯連線,幾乎不產生時延并且?guī)缀醪缓倪壿嬞Y源。

字節(jié)替換如果采用模乘求逆運算[4]實現(xiàn),則邏輯延時較長,速度較慢。為加快速度,采用時延小的基于只讀存儲器(ROM)查找方式的S 盒結構,即輸入8bit 數(shù)據作為地址而相應數(shù)據輸出則為字節(jié)替換后的8 bit 數(shù)據。S 盒結構若采用基于塊存儲的查找表(LUT)來實現(xiàn),一個輪運算中16 個S 盒將占用16×128 個LUT,占用邏輯資源較大。可采用FPGA 內部集成的塊 RAM 來實現(xiàn)S 盒。

列混淆是系數(shù)在有限域上的四次多項式矩陣乘法,輸入列向量(X0, X1, X2, X3),輸出列向量(Y0, Y1, Y2, Y3),加密過程是在上乘以01、02、03、01,解密過程是乘以09、0E、0B、0D。為了優(yōu)化用FPGA 邏輯實現(xiàn),采用一個xtime 函數(shù)來實現(xiàn)上的乘02 運算,對輸入的一個字節(jié)b 做以下變換[5]:xtime = { b[6:0], 1'b0 } ^ ( 8'h1b &{ 8{ b[7]} } )。則列混淆在上所有矩陣乘法就可以通過分解成有限個xtime 運算和異或運算來實現(xiàn)。

輪密鑰加、行移位和列混淆三步運算實現(xiàn)的邏輯資源較少并且邏輯時延較小,可以合并在一個寄存器傳輸層間實現(xiàn)。

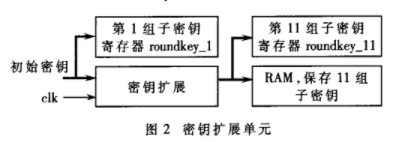

2.2.2 密鑰擴展模塊

密鑰擴展模塊設計比較簡單,只需要4 個S 盒和一個輪常數(shù)字計算模塊,外加一些異或運算和邏輯連線即可完成。密鑰擴展模塊也是一個迭代運算的結構,與加密模塊的輪運算同步,即每個時鐘計算出一輪加密的密鑰。

當解密密鑰更新時,密鑰擴展模塊計算出的各輪密鑰作為解密的輪密鑰,需要按每個時鐘存儲在RAM 中,解密運算時從RAM 中讀取。

2.3 接口設計

模塊的外部接口采用了16 位數(shù)據總線的接口。由于輸入的加密密鑰和解密密鑰各128 位, 占用地址為128×2/16=16 個。另外,加密需要一個輸入明文寄存器和一個輸出密文寄存器,解密需要一個輸入密文寄存器和一個輸出明文寄存器。因此芯片地址數(shù)總共20,即需要5 位地址線。接口讀寫時序的設計以TMS320C5509 型號數(shù)字信號處理器(DSP)總線讀寫時序作為標準。16 位數(shù)據線采用雙向三態(tài)設計。16 位三態(tài)口由片選信號CS 和讀使能信號RDE 控制,當CS 和RDE 均有效時三態(tài)口數(shù)值為輸出數(shù)據寄存器的值以輸出數(shù)據,否則三態(tài)口數(shù)值為高阻將數(shù)據輸入。

3 測試與分析

3.1 加密模塊和解密模塊功能仿真

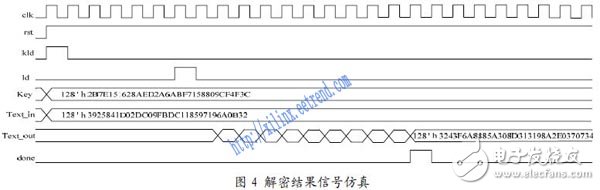

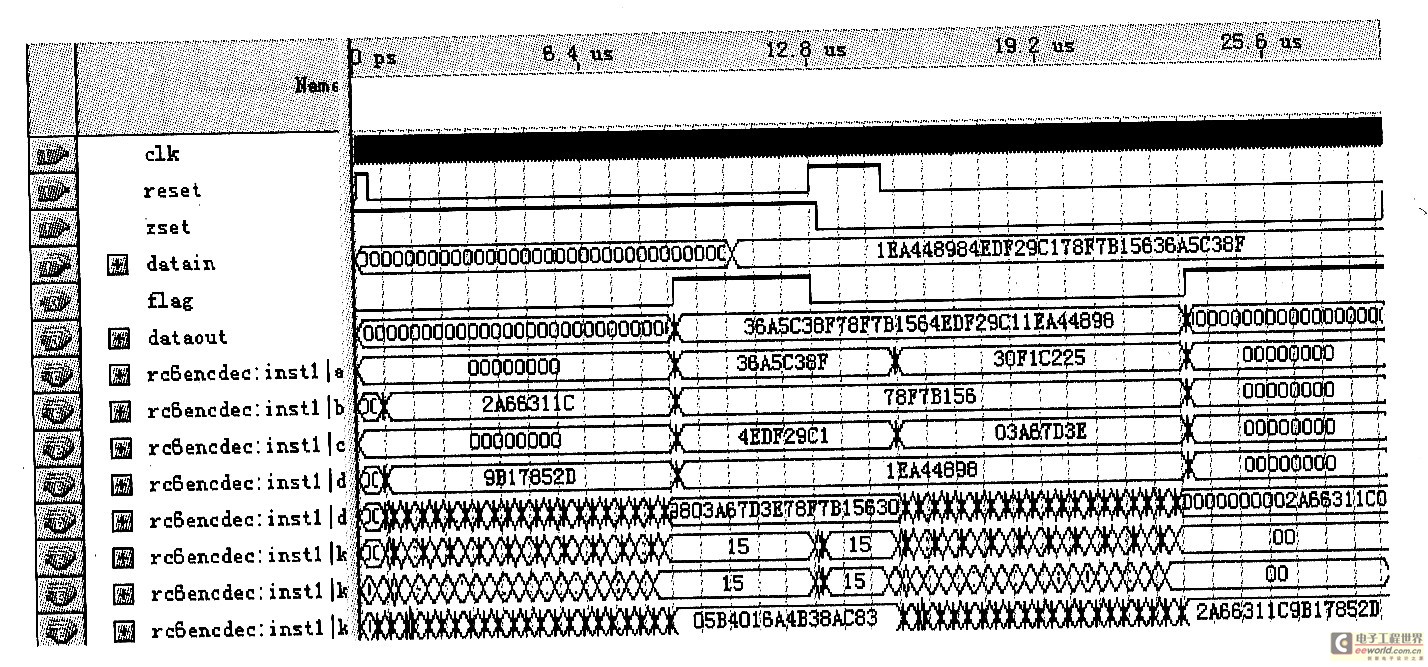

用Xilinx ISE Simulator 分別對加密模塊和解密模塊進行信號仿真,仿真圖如圖3 和圖4 所示。

?

兩圖中text_in[127:0]為輸入數(shù)據,key[127:0]為密鑰,text_in[127:0]為輸出數(shù)據。在圖4 和圖5 中,明文均為(3243,

F6A8, 885A, 308D, 3131, 98A2, E037, 0734 H),密鑰均為(2B7E, 1516, 28AE, D2A6, ABF7, 1588, 09CF, 4F3C H),密文均為(3925, 841D, 02DC, 09FB, DC11, 8597, 196A, 0B32H),證明其加密和解密正確。

3.2 功能測試

將設計的FPGA 模塊連接到TI 的5509 的DSP 開發(fā)板的總線擴展口,F(xiàn)PGA 模塊通過JTAG 線與計算機連接,DSP開發(fā)板通過仿真器與計算機連接。 通過C 程序將明文和密鑰寫入FPGA 模塊,加密后讀出密文,解密過程與之類似。通過DSP 測試,結果與3.1 仿真結果完全一致,證明AES算法在FPGA 上準確實現(xiàn)。

使用在線調試邏輯分析軟件通過JTAG 口對FPGA 總線接口的信號波形進行采樣并顯示,地址、數(shù)據和控制信號正確。通過加密或解密時連續(xù)輸出128 bit 結果間隔的時鐘數(shù)可以計算出,在50 MHz 時,數(shù)據處理能力可達530 Mb/s。

4 結語

所采用的AES 算法設計采用16 位并行總線接口,能方便的與上層處理器擴展。在算法實現(xiàn)上,采用多輪運算共用一個輪結構的迭代結構,適用于在較少邏輯資源的FPGA 芯片上實現(xiàn),滿足了較高吞吐率和較小的芯片面積的應用需求,能滿足當前各種數(shù)據流的加密。算法的實現(xiàn)采用ROM 來實現(xiàn)字節(jié)替換,同時優(yōu)化實現(xiàn)列混淆運算。該設計在賽靈思(Xilinx)公司的xc3s500e 芯片上實現(xiàn),僅占用4230 個Slice,其中7222 個LUT 和1758 個觸發(fā)器,消耗的邏輯資源較少。

電子發(fā)燒友App

電子發(fā)燒友App

評論