1.實例的主要內容

本節旨在通過給定的工程實例——“按鍵開關控制LED”來熟悉Xilinx ISE軟件的基本操作、設計、編譯及仿真流程。同時使用基于Xilinx FPGA的開發板將該實例進行下載、驗證及調試,完成工程設計的硬件實現,熟悉Xilinx FPGA開發板的使用及配置方式。

在本訓練中設計軟件采用ISE 7.1i,實現功能是利用4個按鍵開關來控制8個LED燈。具體的顯示方案是由4個按鍵開關控制8個LED燈,根據按鍵開關按下的不同,會有不同的燈點亮。

在本訓練中,將主要講解下面一些知識點。

·Xilinx ISE工程創建及屬性設置。

·Xilinx ISE源文件設計輸入方式。

·Xilinx ISE綜合。

·Xilinx ISE行為仿真。

·Xilinx ISE約束設計。

·Xilinx ISE布局布線。

·Xilinx ISE時序仿真。

·Xilinx ISE硬件下載。

通過這些知識點,按照下面提供的訓練流程,讀者可以迅速地掌握使用Xilinx ISE軟件進行FPGA開發的方法。

2.實例目標

通過詳細的流程講解,讀者應達到下面的目標。

·熟悉Xilinx ISE軟件的操作環境。

·熟悉Xilinx ISE軟件開發FPGA的基本流程。

·可獨立使用Xilinx ISE軟件開發新工程。

2.6.2 平臺簡介

本實例基于紅色颶風II代Xilinx板,此開發板集成了Xilinx的Spartan3 40萬門FPGA及相關的豐富外設資源。

此開發板更加詳細的信息、擴展附件及使用方法,可以到紅色颶風的官方網站:獲取更多的信息。

本實例將通過一個簡單的實例在這個開發板上對Xilinx的FPGA設計流程做一個全面的介紹,依照此例程的流程便可在該開發板上運行一個FPGA程序。

如圖2.65所示為此開發板的一個外觀圖。

圖2.65 紅色颶風II代Xilinx板外觀圖

2.6.3 實例詳解

本節同樣將使用圖解的方式將整個流程一步一步展現給讀者,使讀者能夠輕松掌握ISE的開發流程。

1.工程創建及屬性設置

(1)啟動Project Navigator。

安裝好ISE7.1套件后,可以按照以下的方法打開Project Navigator。

① 在桌面上面雙擊Xilinx ISE 7.1i的快捷方式圖標,如圖2.66左圖所示。

② 選擇“開始”→“所有程序”→“Xilinx ISE 7.1i”→“Project Navigator”,打開Project Navigator,如圖2.66右圖所示。

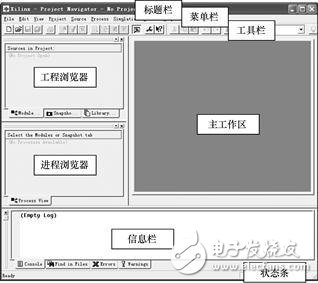

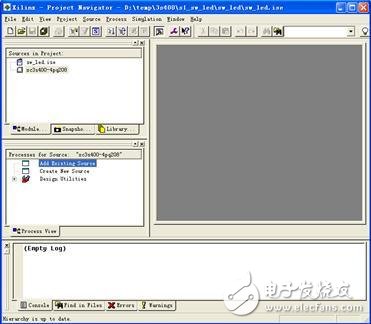

打開后的Project Navigator界面如圖2.67所示。可以看到,Project Navigator的界面是一個標準的Windows軟件視窗。分別包括標題欄、菜單欄、工具欄、工程瀏覽器、進度瀏覽器、主工作區、信息欄、狀態欄。

圖2.66 ISE的啟動

圖2.67 Project Navigator主界面

(2)創建一個新的工程。

單擊“File”→“New Project…”,彈出如圖2.68所示對話框。

圖2.68 新建工程對話框

在這里填寫將要創建的工程的名稱(Project Name)、路徑(Project Location)和工程的頂層模塊類型(Top-Level Module Type)。 頂層模塊類型我們主要使用前面兩種:HDL(Hardware Design Language)硬件設計語言模式和Schematic原理圖模式,這里選擇HDL。

(3)設置工程屬性。

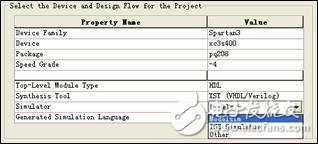

填寫好后,單擊“Next”按鈕,在如圖2.69所示的對話框中設置工程的屬性。

圖2.69 工程屬性對話框

在這個對話框可設置的屬性定義,如表2.4所示。

表2.4 屬性定義Device Family

使用的FPGA的種類 Device 使用的FPGA的型號 Package 使用的FPGA的封裝 Speed Grade 使用的FPGA的速度級別 Top-Level Module Type 頂層模塊類型 Synthesis Tool 綜合工具 Simulator 仿真工具 Generated Simulation Language 仿真模塊語言類型

本實例選用的都是ISE自己帶的綜合工具和仿真工具,這里也可以選擇第三方的應用軟件,如圖2.70和圖2.71所示。

圖2.70 工程屬性對話框選擇第三方綜合工具

圖2.71 工程屬性對話框選擇第三方仿真工具

ModelSim和Synplify Pro是比較通用的第三方仿真和綜合軟件。在這里如果我們選擇了使用第三方的軟件進行綜合及仿真的話,在后面執行相應步驟的時候ISE Navigator就會自動尋找并打開相應的軟件。

(4)添加設計文件。

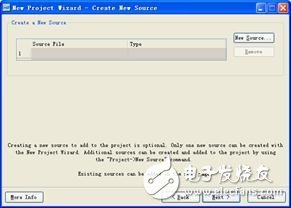

填寫好FPGA型號和使用的綜合,仿真軟件后,單擊“Next”按鈕打開如圖2.72所示的創建源文件對話框。

圖2.72 創建源文件對話框

在這個對話框里面,允許用戶為即將建立的工程創建一個新的源文件,并且這里只可以創建一個源文件。其他的要在工程建立以后創建,也可以在創建工程以后再建立所有的源文件。直接單擊“Next”按鈕,進入如圖2.73所示的添加源文件對話框。

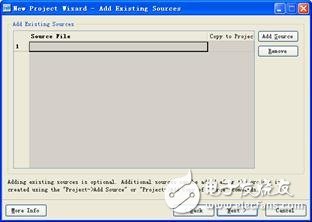

在這個對話框里面為即將建立的工程添加已經存在的源文件。如果沒有現成的源文件,直接單擊“Next”按鈕,完成新工程的創建。

(5)完成工程創建。

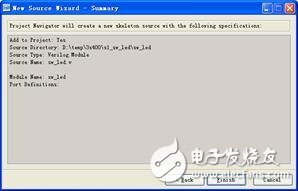

在如圖2.74所示的新工程信息對話框中,列出了新建工程的相關參數及屬性。

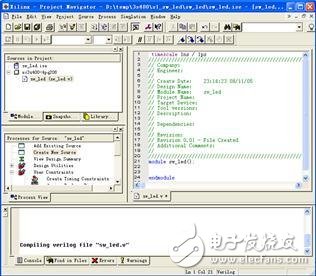

在這個對話框里面顯示將要創建的工程的全部信息,確認無誤后單擊“Finish”按鈕,Project Navigator將自動創建一個名為sw_led的工程。如圖2.75所示是新工程的界面。

圖2.73 添加源文件對話框

圖2.74 工程信息對話框

圖2.75 工程創建后的界面

2.設計輸入

創建好工程以后就要為工程添加源文件了,具體方法如下。

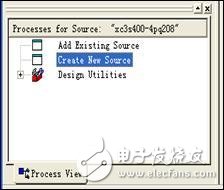

為工程添加源文件有兩種方式,可以雙擊“Process View”對話框里面的“Create New Source”,也可以在“Module View”對話框里面的“xc3s400-4pq208”圖標上面單擊鼠標右鍵,選擇“New Source…”選項,如圖2.76所示。

圖2.76 添加源文件的兩種方式

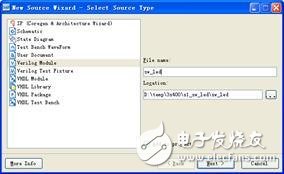

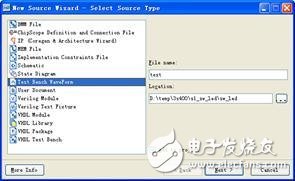

選擇“New Source”,彈出如圖2.77所示的新建源文件對話框。

圖2.77 新建資源對話框

在右面的“File Name”欄里面填寫要生成的源文件的名字,在“Location”欄填寫源文件保存的路徑,一般位于工程文件夾里面,沒有特殊需要不必更改。另外一定要選擇“Add to project”選項,然后在左邊的一排圖標里面選擇源文件的類型后單擊“Next”按鈕,進入如圖2.78所示的Verilog源定義對話框。

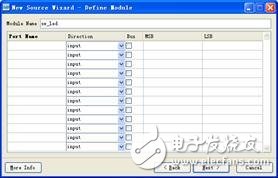

可以在上面的對話框里面輸入源文件的模塊名稱和管腳定義,也可以先不輸入,后面寫程序的時候自己輸入。單擊“Next”按鈕,完成源文件的創建,在如圖2.79所示的對話框中列出了新建源文件的一些信息。

確認信息無誤后,單擊“Finish”按鈕,ISE將生成名為sw_led.v的源文件,如圖2.80所示。

圖2.78 新建Verilog文件設置對話框

圖2.79 新建源文件信息對話框

圖2.80 添加新資源后工程界面

用戶可以在工作區中開始進行設計的輸入,也可參考實例代碼中的例程,將代碼直接復制到新建的Verilog文件下。輸入好程序以后,保存源文件,完成設計的輸入。

3.綜合及仿真

(1)綜合。

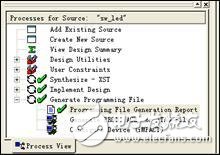

在“Process View”對話框里面雙擊“Synthesize – XST”,開始進行工程的綜合,如圖2.81所示。

綜合主要檢查源文件程序里面的語法錯誤(Check Syntax),雙擊“View Synthesis Report”可以觀察綜合的結果報告,如圖2.82所示。

圖2.82 綜合報告

如果在這步發現源程序的設計語言有語法毛病,就會彈出Error警告。這樣就可以根據報錯的位置,在源程序里面查找錯誤位置,修改好以后重新進行綜合,直至無錯誤為止。

(2)綜合后仿真。

這里的仿真是綜合后的仿真,也可以稱為功能仿真。仿真時并不考慮工程的約束條件及器件的資源使用狀況,因此不會產生仿真延遲。這里使用的是ISE自帶的仿真工具進行綜合后仿真。下面是仿真的步驟。

① 產生仿真文件。

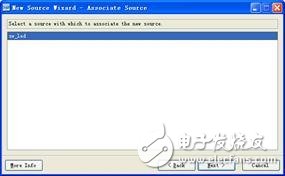

如圖2.76的方式,在“New Source”對話框里面選擇創建Test Bench Wavefrom文件,如圖2.83所示。

單擊“Next”按鈕,在如圖2.84所示對話框中為Test Bench指定源文件。如圖所示在源文件對話框中只有一個文件,這是因為我們只為工程添加了一個設計文件。如果我們為工程添加了幾個設計文件,在這個對話框中,將出現多個源文件。此時用戶可以選擇需要進行仿真的源文件即可。

圖2.83 新建Test Bench對話框

在本訓練中,將要進行仿真的源文件是sw_led,如圖2.84所示。單擊“Next”按鈕完成仿真文件的產生,如圖2.85所示。

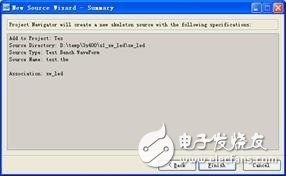

圖2.84 為Test Bench指定源文件

圖2.85 Test Bench信息對話框

單擊“完成”按鈕,ISE將創建名為test.tbw的仿真文件,同時彈出如圖2.86所示的對話框。在該對話框中,用戶可以對仿真的時間參數進行設置。

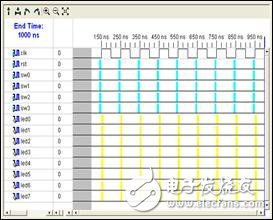

在這個對話框中,包括時鐘信息、時鐘時間信息、全局信號、仿真時間等多個參數都可以進行設置。按照仿真需求修改好時間參數以后,單擊“OK”按鈕就能在ISE的工作區里面看見新建的波形文件了,如圖2.87所示。

在波形文件里面,clk是時鐘信號,在前面的時間參數設計里面已經設置好了。用戶若需要對時鐘進行更改,可選擇執行“Test Bench”→“Rescale Timing…”命令,彈出修改時間參數的對話框,如圖2.88所示。

圖2.86 仿真時間參數設置對話框

圖2.87 時鐘波形

圖2.88 修改時間參數對話框

同樣也可以執行“Test Bench”→“Set End of Test Bench…”,在彈出的對話框里面修改仿真波形的截止時間,如圖2.89所示。

圖2.89 截止時間設置對話框

單擊“OK”按鈕就會發現仿真波形的時間長度由1000ns變成了2000ns。

② 添加仿真激勵。

要進行仿真,還需要為仿真添加激勵。這里可以通過點擊波形圖中的藍色方塊來設置輸入波形電平的高低,如圖2.90所示。

圖2.90 設置輸入電平

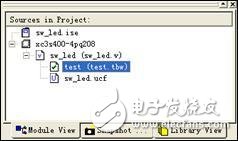

設置好以后一定不要忘記保存波形文件。保存以后就會在工程瀏覽器的當前工程的子目錄下看見剛生成測試的文件,如圖2.91所示。

圖2.91 保存仿真文件到工程

③ 仿真。

首先在工程瀏覽器的【Module View】里面選擇“test(test.tbw)”。

圖2.92 由波形文件生成測試代碼

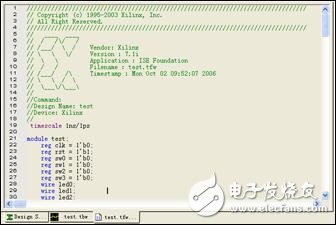

然后在進度瀏覽器的“Process View”對話框里面雙擊“View Generated Test Bench As HDL”圖標,就能看見ISE根據剛才設置的波形文件自動生成的測試文件,如圖2.93所示。

圖2.93 生成的測試代碼

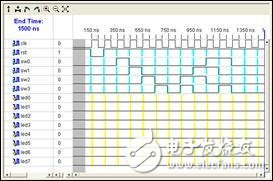

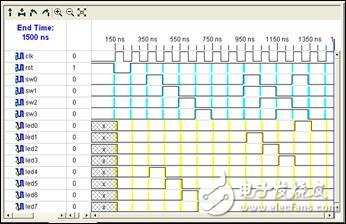

在進度瀏覽器中雙擊【Generate Expected Simulation Result】,彈出兩個對話框,都選擇是(Y),將看見生成的預期輸出波形,如圖2.94所示。

圖2.94 預期仿真波形

在進度瀏覽器中雙擊“Add Test Bench to Project”,將測試波形添加到工程里面。將會看到工程瀏覽器中test文件的圖標由變成。

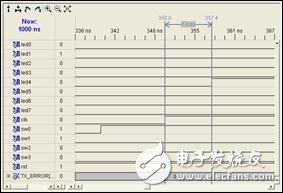

如圖2.95所示,在進度瀏覽器中雙擊“Simulate Behavioral Model”將對工程進行行為仿真,仿真結果如圖2.96所示。

圖2.95 運行功能仿真

圖2.96 功能仿真結果

從圖中可以看出功能仿真結果符合設計要求,可以繼續進行下面的設計。如果此處仿真發現設計功能不符合要求,則要對原代碼進行修改,直到仿真結果符合設計要求為止。4.約束設計在源程序輸入完成以后,就可以設置約束,規劃布局布線了。

約束有很多種:時序約束(Timing Constrains)、管腳約束(Assign Package Pins)以及面積約束(Area Const- raints)等。

如圖2.97所示是ISE進度瀏覽器中包含的用戶約束的選項。

圖2.97 設置約束

(1)時序約束。

時需約束主要約束設計的時序和時鐘頻率,雙擊圖2.97中的“Create Timing Constraints”圖標,ISE將打開約束編輯器,如圖2.98所示。

圖2.98 時序約束界面

在約束編輯器里面有4個復選頁,定義如表2.5所示。

表2.5 屬性定義屬 性

定 義Global 用于附加全局約束,包括周期約束,輸入延遲約束和輸出延遲約束Ports 附加端口約束,可以對每一個端口進行單獨設置,包括物理位置、輸入延遲和輸出延遲。同時,也可以設置分組,進行分組約束Advanced 附加分組約束(TNM/TNM_NET/TIMEGRP)和時序約束(FROM_TO/TIG O/OFFSET)等Misc 附加專用約束,包括電壓、初始值等 注意:附加約束的原則是先加全局約束后加分組約束。 在本實例中只做簡單的時鐘約束。在clk的period中輸入:20ns HIGH 50%,即設置時鐘的周期和占空比。設置后保存,完成時序約束。

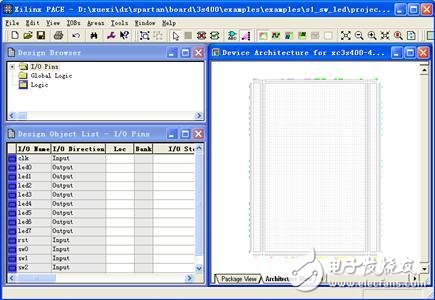

(2)管腳約束。

管腳約束即約束工程設計源文件與選定器件對應的輸入/輸出管腳屬性。雙擊圖2.97中的“Assign Package Pins”圖標,ISE將打開PACE工具,如圖2.99所示。 通過圖2.99的“Design Object List”對話框里面的Loc列,可以為設計添加輸入/輸出管腳,添加形式為“Pxxx”或者“pxxx”。其中P/p代表Pin,xxx是數值。

(3)面積約束。

面積約束目的在于規劃FPGA里面的邏輯使用大小。雙擊圖2.97中的“Create Area Constraints”圖標,ISE同樣打開PACE工具,面積約束和管腳約束用的是一個界面。在面積約束里面我們可以對設計使用的資源面積加以規劃,控制使用資源在FPGA里面的位置。

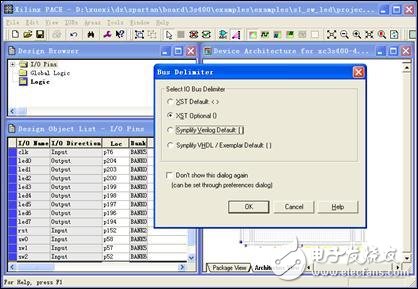

這里只使用到管腳約束,按照按鍵和LED燈與FPGA的連接,輸入管腳分配,然后保存分配。在保存選項中,選擇“XST Optional”,如圖2.100所示,關閉對話框,完成約束設計。

圖2.99 管腳約束工具PACE

圖2.100 保存管腳約束結果

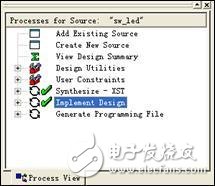

5.布局布線

設置好了各種約束以后就可以進行布局和布線了。雙擊進度瀏覽器中的“Implement Design”,開始進行布局布線實現。與綜合相同,如果在“Implement Design”的右邊出現綠色的對號,說明已經完成布局布線,沒有發現錯誤,如圖2.101所示。

圖2.101 運行布局布線

如果實現過程中出現錯誤,在信息欄中根據錯誤的提示,修改相關的約束設計,再進行布局布線的實現,直至沒有錯誤為止。

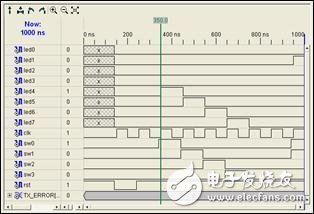

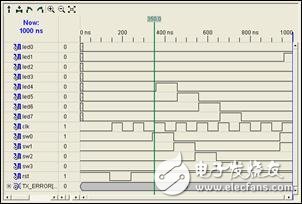

6.布局布線后仿真

在工程瀏覽器中選擇測試文件,雙擊進度瀏覽器中“Implement Design”下面的“Simulate Post-Place & Route Model”,對工程進行布局布線后仿真,仿真結果如圖2.102所示。

圖2.102 時序仿真結果

通過與行為仿真結果圖2.96對比,可以發現,布局布線后仿真加入了布線的延遲,輸出的結果相對于時鐘有相應的延遲。在工作區里面單擊鼠標右鍵,在彈出的菜單里面選擇“Add Measure”選項,可以通過放大工作區和拖動時間測量游標,讀取時間延遲,如圖2.103所示。

由上圖可以看出,盡管輸出相對于時鐘存在一定的延時,但輸出結果是正確的,符合設計要求,可以進行下載和在線調試了。

圖2.103 測量時間延遲

7.下載程序

布局布線完成以后就可以將程序下載到開發板上進行調試。開發板提供兩種下載方式:JTAG模式和PROM模式。區別在于JTAG模式是用于在線調試使用的,斷電后不保留程序;而PROM模式則是將程序燒寫在存儲器里面,上電后自動加載。

(1)JTAG模式下載。

如圖2.104所示,在進度瀏覽器中“Generate Programming File”下面可以看到有3個選項,分別是編程文件生成報告、生成編程文件和使用iMPACT配置器件。

在“Generate Programming File”圖標上面單擊右鍵,選擇“Properties…”,彈出如圖2.105所示的屬性對話框,在其中可以設置下載文件的屬性。

圖2.104 生成下載文件

圖2.105 “General Options”選項卡

在該對話框中有4個選項卡,可以對相應的下載參數進行設置。

“General Options”選項卡里面的“Create Bit File”選項生成用于JTAG模式下載的二進制下載文件。確定選擇該項,如圖2.105所示。

在“Startup Options”選項卡里面將“FPGA Start-Up Clock”后面的內容改為“JTAG Clock”,如圖2.106所示,在這里要根據不同的下載模式正確地選擇時鐘。

在“Readback Options”選項卡里面將“Security”后面的內容置為“Enable Readback an Reconfiguration”,如圖2.107所示,然后單擊“OK”按鈕,完成下載的屬性設置。

圖2.106 “Startup Options”選項卡

圖2.107 “Readback Options”選項卡

如圖2.108所示,雙擊進度瀏覽器里面的“Generate Programming File”圖標,ISE將生成供 JTAG模式下載的bit文件。“Generate Programming File”左邊的綠色對號說明已經成功生成了下載 文件。

圖2.108 生成下載文件

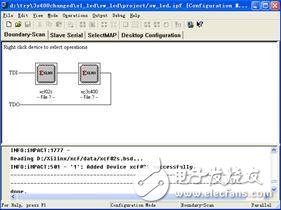

雙擊“Generate Programming File”下面的“Configure Device(iMPACT)”圖標,打開如圖2.109所示的iMPACT工具。

圖2.109 iMPACT工具

在如圖2.109所示的對話框里面選擇器件配置的模式,這里選擇邊界掃描模式“Boundary-Scan Mode”,單擊“下一步”按鈕,如圖2.110所示。

圖2.110 邊界掃描模式選擇對話框

選擇自動加載邊界掃描鏈路,單擊完成。

由于開發板上面的JTAG和PROM下載是在一條鏈路上的,所以會彈出如圖2.111所示的對話框,單擊“確定”按鈕就能看見ISE掃描到的開發板上面的下載鏈,如圖2.112所示。圖2.111 邊界掃描檢測結果對話框

圖2.112 ISE掃描下載鏈結果

其中下面標有xcf02s的圖標代表的是PROM,下面標有xc3s400的圖標代表FPGA。

雙擊FPGA圖標,在彈出的對話框里面選擇剛才生成的二進制下載文件(后綴為.bit)。配置好以后右鍵單擊FPGA圖標,在彈出的菜單里面選擇“Program…”選項,如圖2.113所示。此時將會出現如圖2.114所示的下載屬性設置對話框。

圖2.113 設置配置文件

圖2.114 配置設置對話框 單擊“OK”按鈕就可以開始下載了。若下載成功將會有如圖2.115所示的下載成功提示。

圖2.115 JTAG下載成功

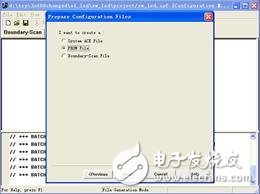

(2)PROM模式下載。

PROM模式下載是把程序存在一塊存儲器里面(開發板上面使用的是Xilinx公司的xcf02s)。當開發板上電的時候,FPGA就自動加載存儲器里面的程序。下面是PROM模式下載的具體操作方法。 要進行PROM模式下載,首先要生成相應的二進制下載文件,雙擊進程瀏覽器中“Generate Programming File”下面的“Generate PROM, ACE, or JTAG File”圖標,彈出如圖2.116的對話框。

圖2.116 生成PROM文件對話框

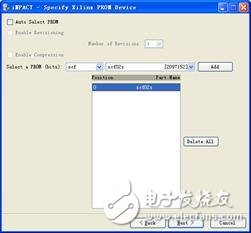

選擇“PROM File”選項,單擊“下一步”按鈕,打開如圖2.117所示的PROM文件配置對話框。

圖2.117 PROM文件設置對話框

在該對話框中,選擇生成一個Xilinx PROM,后綴選擇MCS,文件格式選擇FF(十六進制),在“PROM File Name”后面填寫生成的PROM下載文件的名稱,在“Location”后面填寫PROM文件保存地址。配置后單擊“Next”按鈕,出現PROM器件配置對話框,如圖2.118所示。 選擇PROM的型號,要與開發板上面使用的對應。這里選擇xcf02s,單擊“Next”按鈕。

?

圖2.118 選擇PROM型號

圖2.119 為生成PROM文件添加二進制文件

在出現的如圖2.119所示對話框中單擊“Add File…”按鈕,在彈出的對話框里面選擇JTAG下載的時候使用的二進制文件(后綴為.bit),ISE將通過這個二進制文件生成PROM文件。圖2.120 是否還要加載一個設計文件對話框 選擇完一個二進制文件后,會彈出如圖2.120所示的對話框,詢問是否還要加載一個設計文件。單擊“NO”按鈕,完成PROM模式下載的配置。

圖2.121 生成PROM文件

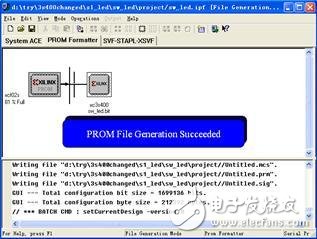

在出現的圖2.121中單擊“Finish”按鈕,ISE就會自動為我們生成后綴為.MCS的十六進制PROM下載文件。生成成功后,將出現如圖2.122所示的提示。

圖2.122 PROM文件生成成功提示

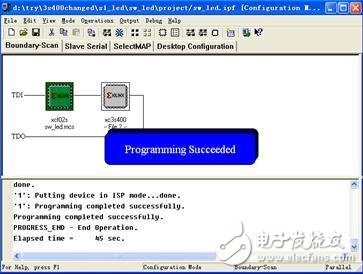

生成了PROM的下載文件以后,再按照JTAG下載的方法,掃描下載鏈。將生成的.MCS文件加載到PROM圖標中去,然后再在PROM圖標上面點擊右鍵,選擇“Program…”選項,如圖2.123所示。 如圖2.124,在出現的下載屬性配置對話框中選擇相應的選項后,單擊“OK”按鈕就開始PROM的下載了(PROM下載相對比較慢,并且最好先擦除PROM里面的內容再下載)。成功下載會出現如圖2.125所示的提示。

圖2.123 下載PROM器件

圖2.124 下載PROM器件設置對話框

圖2.125 完成對PROM器件的燒寫

需要注意的是,如果選用JTAG下載模式,則下載成功后,FPGA就可實現預想的功能。如果選用PROM下載模式,下載成功后,要重新上電后FPGA才能正常工作。

因為PROM直接方式是將文件下載到PROM器件中,并沒有直接下載到FPGA里,要重新上電后由FPGA自動從PROM器件中加載配置文件,才能實現預想的功能。

當然用戶也可以在如圖2.124所示的屬性配置中選擇“Load FPGA”選項。這樣PROM下載完成后,下載的邏輯將自動加載至FPGA內,而無需重新上電。

2.6.4 小結

上述步驟就是利用ISE進行的一個完整的FPGA設計流程。雖然例程實現的功能比較簡單,但對于初學者來說,是一個不錯的入門實例。

此實例的主要目的是讓初學者對FPGA的設計有一個初步的了解,并熟悉ISE軟件的使用,為今后的學習打下基礎。

?

電子發燒友App

電子發燒友App

評論