Virtex系列是賽靈思的高端產(chǎn)品,也是業(yè)界的頂級(jí)FPGA產(chǎn)品,賽靈思公司正是憑借Virtex系列產(chǎn)品贏得市場(chǎng),從而獲得FPGA供應(yīng)商領(lǐng)頭羊的地位。可以說賽靈思以其Virtex-5、Virtex-4、Virtex-2 Pro和Virtex-2系列FPGA產(chǎn)品引領(lǐng)現(xiàn)場(chǎng)可編程門陣列行業(yè)。主要面向電信基礎(chǔ)設(shè)施、汽車工業(yè)、高端消費(fèi)電子等應(yīng)用。目前的主流芯片包括:Vitrex-2、Virtex-2 Pro、Virtex-4和Virtex-5等種類。

(1)Vitrex-2系列

Vitrex-2系列具有優(yōu)秀的平臺(tái)解決方案,這進(jìn)一步提升了其性能;且內(nèi)置IP核硬核技術(shù),可以將硬IP核分配到芯片的任何地方,具有比Virtex系列更多的資源和更高的性能。其主要特征如下所示: 采用0.15/0.12 工藝; 核電壓為1.5V,工作時(shí)鐘可以達(dá)到420MHz; 支持20多種I/O接口標(biāo)準(zhǔn); 內(nèi)嵌了多個(gè) 硬核乘法器,提高了DSP處理能力; 具有完全的系統(tǒng)時(shí)鐘管理功能,多達(dá)12個(gè)DCM模塊。

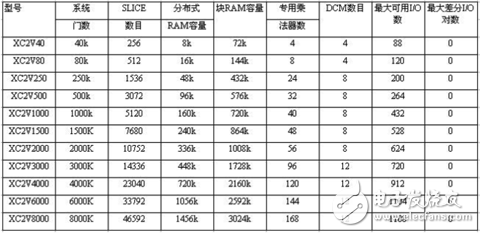

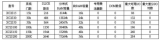

Virtex-2系列產(chǎn)品的主要技術(shù)特征如下表所示。

表3-10 Virtex-2系列 FPGA主要技術(shù)特征

(2)Virtex-2Pro系列

Virtex-2 Pro系列在Virtex-2的基礎(chǔ)上,增強(qiáng)了嵌入式處理功能,內(nèi)嵌了PowerPC?405內(nèi)核,還包括了先進(jìn)的主動(dòng)互聯(lián)(Active Interconnect)技術(shù),以解決高性能系統(tǒng)所面臨的挑戰(zhàn)。此外還增加了高速串行收發(fā)器,提供了千兆以太網(wǎng)的解決方案。其主要特征如下所示: 采用0.13 工藝; 核電壓為1.5V,工作時(shí)鐘可以達(dá)到420MHz; 支持20多種I/O接口標(biāo)準(zhǔn); 增加了2個(gè)高性能RISC技術(shù)、頻率高達(dá)400MHz的PowerPC?處理器;增加多個(gè)3.125Gbps速率的Rocket串行收發(fā)器; 內(nèi)嵌了多個(gè) 硬核乘法器,提高了DSP處理能力; 具有完全的系統(tǒng)時(shí)鐘管理功能,多達(dá)12個(gè)DCM模塊。

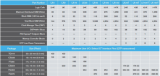

Virtex-2 Pro系列產(chǎn)品的主要技術(shù)特征如下表所示。

表3-11 Virtex-2 Pro系列 FPGA主要技術(shù)特征

(3)Virtex-4系列

Virtex-4器件整合了高達(dá)200,000個(gè)的邏輯單元,高達(dá)500 MHz的性能和無(wú)可比擬的系統(tǒng)特性。Virtex-4產(chǎn)品基于新的高級(jí)硅片組合模塊(ASMBL)架構(gòu),提供了一個(gè)多平臺(tái)方式(LX、SX、FX),使設(shè)計(jì)者可以根據(jù)需求選用不同的開發(fā)平臺(tái);邏輯密度高,時(shí)鐘頻率能夠達(dá)到500MHz;具備DCM模塊、PMCD相位匹配時(shí)鐘分頻器、片上差分時(shí)鐘網(wǎng)絡(luò);采用了集成FIFO控制邏輯的500MHz SmartRAM技術(shù),每個(gè)I/O都集成了ChipSync源同步技術(shù)的1 Gbps I/O和Xtreme DSP邏輯片。其主要特點(diǎn)如下: 采用了90 工藝,集成了高達(dá)20萬(wàn)的邏輯單元;系統(tǒng)時(shí)鐘500MHz; 采用了集成FIFO控制邏輯的500MHz Smart RAM 技術(shù); 具有DCM模塊、PMCD相位匹配時(shí)鐘分頻器和片上差分時(shí)鐘網(wǎng)絡(luò); 每個(gè)I/O都集成了ChipSync源同步技術(shù)的1Gbps I/O; 具有超強(qiáng)的信號(hào)處理能力,集成了數(shù)以百計(jì)的XtremeDSP Slice,單片最大的處理速率為 。 Virtex-4 LX平臺(tái)FPGA的特點(diǎn)是密度高達(dá)20萬(wàn)邏輯單元,是全球邏輯密度最高的FPGA系列之一,適合對(duì)邏輯門需求高的設(shè)計(jì)應(yīng)用。

Virtex-4 SX平臺(tái)提高了DSP、RAM單元與邏輯單元的比例,最多可以提供512個(gè)XtremeDSP硬核,可以工作在500MHz,其最大的處理速率為 ,并可以以其創(chuàng)建40多種不同功能,并能多個(gè)組合實(shí)現(xiàn)更大規(guī)模的DSP模塊。與Virtex-2 Pro系列相比,還大大降低了成本和功耗,具有極低的DSP成本。SX平臺(tái)的FPGA非常適合應(yīng)用于高速、實(shí)時(shí)的數(shù)字信號(hào)處理領(lǐng)域。

Virtex-4 FX平臺(tái)內(nèi)嵌了1~2個(gè)32位RISC PowerPC?處理器,提供了4個(gè)1300 Dhrystone MIPS、10/100/1000自適應(yīng)的以太網(wǎng)MAC內(nèi)核,協(xié)處理器控制器單元(APU)允許處理器在FPGA中構(gòu)造專用指令,使FX器件的性能達(dá)到固定指令方式的20倍;此外,還包含24個(gè)Rocket I/O串行高速收發(fā)器,支持常用的0.6Gbps、1.25 Gbps、2.5 Gbps、3.125 Gbps、4 Gbps、6.25 Gbps、10 Gbps等高速傳輸速率。FX平臺(tái)適用于復(fù)雜計(jì)算和嵌入式處理應(yīng)用。

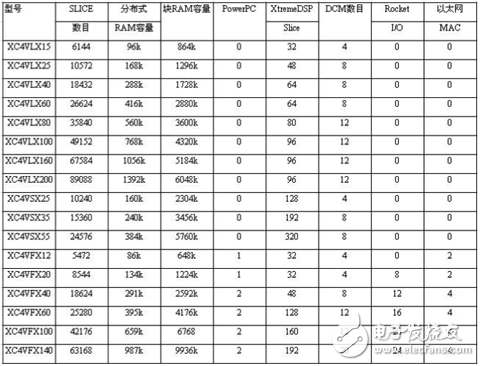

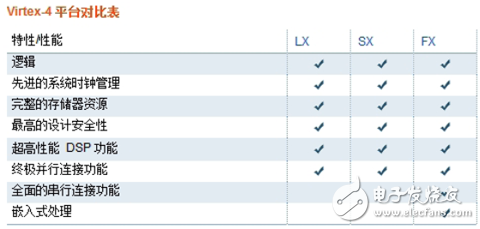

Virtex-4系列產(chǎn)品的主要技術(shù)特征如下表所示。

表3-12 Virtex-4系列 FPGA主要技術(shù)特征

表3-13 Virtex-4系列平臺(tái)性能對(duì)比

(5)Virtex-5系列

Virtex?-5 FPGA 是世界上首款 65nm FPGA 系列,采用 1.0v、三柵極氧化層工藝技術(shù)制造而成,并且根據(jù)所選器件可以提供 330,000 個(gè)邏輯單元、1,200 個(gè) I/O 引腳、48 個(gè)低功耗收發(fā)器以及內(nèi)置式PowerPC?440、PCIe? 端點(diǎn)和以太網(wǎng) MAC 模塊。已經(jīng)提供了5種系列平臺(tái),分別是LX、LXT 、SXT、FXT、TXT,每種平臺(tái)都在高性能邏輯、串行連接功能、信號(hào)處理和嵌入式處理性能方面實(shí)現(xiàn)了最佳平衡。例如LX針對(duì)高性能邏輯進(jìn)行了優(yōu)化,LXT針對(duì)具有低功耗串行連接功能的高性能邏輯進(jìn)行了優(yōu)化,SXT針對(duì)具有低功耗串行連接功能的DSP 和存儲(chǔ)器密集型應(yīng)用進(jìn)行了優(yōu)化。Virtex-5 FXT 則用于實(shí)現(xiàn)具有速率最高的串行連接功能的嵌入式處理,Virtex-5 TXT可用于實(shí)現(xiàn)超高帶寬應(yīng)用,如有線通信與數(shù)據(jù)通信系統(tǒng)內(nèi)的橋接、開關(guān)和集聚。

現(xiàn)有的Virtex-5系列產(chǎn)品的主要技術(shù)特征如下表所示。

表3-14 Virtex-5系列 FPGA主要技術(shù)特征

其主要特點(diǎn)如下:

采用了最新的65工藝,結(jié)合低功耗IP塊將動(dòng)態(tài)功耗降低了35%;此外,還利用65nm三柵極氧化層技術(shù)保持低靜態(tài)功耗; 利用65nm ExpressFabric技術(shù),實(shí)現(xiàn)了真正的6輸入LUT,并將性能提高了2個(gè)速度級(jí)別。內(nèi)置有用于構(gòu)建更大型陣列的FIFO邏輯和ECC的增強(qiáng)型36 Kbit Block RAM帶有低功耗電路,可以關(guān)閉未使用的存儲(chǔ)器。 邏輯單元多達(dá)330,000個(gè),可以實(shí)現(xiàn)無(wú)與倫比的高性能; I/O引腳多達(dá)1,200個(gè),可以實(shí)現(xiàn)高帶寬存儲(chǔ)器/網(wǎng)絡(luò)接口,1.25 Gbps LVDS; 低功耗收發(fā)器多達(dá)24個(gè),可以實(shí)現(xiàn)100 Mbps - 3.75 Gbps高速串行接口; 核電壓為1V,550 MHz系統(tǒng)時(shí)鐘; 550 MHz DSP48E slice內(nèi)置有25 x 18 MAC,提供352 GMACS的性能,能夠在將資源使用率降低50%的情況下,實(shí)現(xiàn)單精度浮點(diǎn)運(yùn)算; 利用內(nèi)置式PCIe端點(diǎn)和以太網(wǎng)MAC模塊提高面積效率 ; 更加靈活的時(shí)鐘管理管道(Clock Management Tile)結(jié)合了用于進(jìn)行精確時(shí)鐘相位控制與抖動(dòng)濾除的新型PLL和用于各種時(shí)鐘綜合的數(shù)字時(shí)鐘管理器(DCM); 采用了第二代sparse chevron封裝,改善了信號(hào)完整性,并降低了系統(tǒng)成本; 增強(qiáng)了器件配置,支持商用flash存儲(chǔ)器,從而降低了成本。

注:一個(gè)Virtex-5 Slice具有4個(gè)LUT和4個(gè)觸發(fā)器,而一個(gè)前文所提及的常規(guī)Slice只包含2個(gè)LUT個(gè)2個(gè)觸發(fā)器。每個(gè)DSP48E包含一個(gè)25*18位的硬核乘法器、一個(gè)加法器和一個(gè)累加器。

?

?

Virtex-5 FPGA 訂購(gòu)信息適用于所有封裝,包括無(wú)鉛封裝

(6)Virtex-6 FPGA系列

基于采用第三代Xilinx ASMBL? 架構(gòu)的40nm制造工藝,Virtex-6 FPGA系列還擁有新一代開發(fā)工具和早已針對(duì)Virtex-5 FPGA而開發(fā)的廣泛IP庫(kù)支持。這些都為多產(chǎn)的開發(fā)和設(shè)計(jì)移植提供了強(qiáng)大的支持。 與競(jìng)爭(zhēng)廠商提供的40nm FPGA產(chǎn)品相比,新的Virtex-6 FPGA系列器件性能提高15%,功耗降低15%。新器件在1.0v內(nèi)核電壓上操作,同時(shí)還有可選的0.9v低功耗版本。 這些使得系統(tǒng)設(shè)計(jì)師可在設(shè)計(jì)中采用Virtex-6 FPGA,從而支持建設(shè)“綠色”中心辦公室和數(shù)據(jù)中心。對(duì)于電信行業(yè)這一點(diǎn)特別重要,因?yàn)樵撔袠I(yè)正在擴(kuò)展對(duì)因特網(wǎng)視頻和富媒體內(nèi)容的支持。

Virtex- 6 FPGA系列包括三個(gè)面向應(yīng)用領(lǐng)域而優(yōu)化的FPGA平臺(tái),分別提供了不同的特性和功能組合來更好地滿足不同客戶應(yīng)用的需求:

Virtex-6 LXT FPGA—優(yōu)化目標(biāo)應(yīng)用需要高性能邏輯、DSP以及基于低功耗GTX 6.5Gbps串行收發(fā)器的串行連接能力。

Virtex-6 SXT FPGA—優(yōu)化目標(biāo)應(yīng)用需要超高性能DSP以及基于低功耗GTX 6.5Gbps串行收發(fā)器的串行連接能力。

Virtex-6 HXT FPGA—作為優(yōu)化的通信應(yīng)用需要最高的串行連接能力,多達(dá)64個(gè)GTH串行收發(fā)器可提供高達(dá)11.2Gbps帶寬 。

Virtex-6 FPGA把先進(jìn)的硬件芯片技術(shù)、創(chuàng)新的電路設(shè)計(jì)技術(shù)以及架構(gòu)上的增強(qiáng)完美結(jié)合在一起,與前一代Virtex器件以及競(jìng)爭(zhēng)FPGA產(chǎn)品相比,功耗大大降低,性能更高并且成本更低。表3-15顯示了Virtex-6FPGA系列主要技術(shù)特征。

表3-15 Virtex-6 FPGA系列主要技術(shù)特征

(7)Xilinx PROM芯片介紹

賽靈思公司的Platform Flash PROM能為所有型號(hào)的Xilinx FPGA提供非易失性存儲(chǔ)。全系列PROM的容量范圍為1Mbit到32Mbit,兼容任何一款Xilinx FPGA芯片,具備完整的工業(yè)溫度特性(-40°C 到 +85°C),支持IEEE1149.1所定義的JTAG邊界掃描協(xié)議。

PROM芯片可以分成3.3V核電壓的 系列和1.8V核電壓的 系列兩大類,前者主要面向底端引用,串行傳輸數(shù)據(jù),且容量較小,不具備數(shù)據(jù)壓縮的功能;后者主要面向高端的FPGA芯片,支持并行配置、設(shè)計(jì)修訂(Designing Revisioning)和數(shù)據(jù)壓縮(Compression)等高級(jí)功能,以容量大、速度快著稱,其詳細(xì)參數(shù)如下表所示。

表3-16 賽靈思公司PROM芯片總結(jié) (截至2008年11月數(shù)據(jù))

該系列包含XCF01S、XCF02S和XCF04S(容量分別為:1Mb、2Mb和4Mb),其共同特征有3.3V核電壓,串行配置接口以及SOIC封裝的VO20封裝。 內(nèi)部控制信號(hào)、數(shù)據(jù)信號(hào)、時(shí)鐘信號(hào)和JTAG信號(hào)的整體結(jié)構(gòu)如圖3-2所示。

圖3-2 XCF01S/XCF02S/XCF04S PROM結(jié)構(gòu)組成框圖

系列有XCP08P、XCF16P和XCF32P(容量分別為:8Mb、16Mb和32Mb),其共同特征有1.8V核電壓、串行或并行配置接口、設(shè)計(jì)修訂、內(nèi)嵌的數(shù)據(jù)壓縮器、FS48封裝或VQ48封裝和內(nèi)嵌振蕩器。 內(nèi)部控制信號(hào)、數(shù)據(jù)信號(hào)、時(shí)鐘信號(hào)和JTAG信號(hào)的整體結(jié)構(gòu)如圖3-3所示,其先進(jìn)的結(jié)構(gòu)和更高的集成度在使用中帶來了極大的靈活性。

?

圖3-3 XCP08P/XCF16P/XCF32P PROM結(jié)構(gòu)組成框圖

值得一提的是系列設(shè)計(jì)修正和數(shù)據(jù)壓縮這兩個(gè)功能。設(shè)計(jì)修訂功能在FPGA加電啟動(dòng)時(shí)改變其配置數(shù)據(jù),根據(jù)所需來改變FPGA的功能,允許用戶在單個(gè)PROM中將多種配置存儲(chǔ)為不同的修訂版本,從而簡(jiǎn)化FPGA配置更改,在FPGA內(nèi)部加入少量的邏輯,用戶就能在PROM中存儲(chǔ)多達(dá)4個(gè)不同修訂版本之間的動(dòng)態(tài)切換。數(shù)據(jù)壓縮功能可以節(jié)省PROM的空間,最高可節(jié)約50%的存儲(chǔ)空間,從而降低成本,是一項(xiàng)非常實(shí)用的技術(shù)。當(dāng)然如果編程時(shí)在軟件端采用了壓縮模式,則需要一定的硬件配置來完成相應(yīng)的解壓縮。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論