Xilinx ISE Design Suite 12.3 – 現(xiàn)已面市!

2010-10-09 15:22:09 1235

1235 電子發(fā)燒友網(wǎng)核心提示 :Xilinx ISE 14.2安裝指南,包括Xilinx ISE 14.2軟件下載、Xilinx ISE 14.2軟件安裝、Xilinx ISE 14.2相關(guān)產(chǎn)品介紹、Xilinx ISE軟件激活、Xilinx ISE14.2軟件啟動(dòng)和Xilinx ISE 14.2新建工

2012-10-31 11:59:13 61264

61264

直接在modelsim軟件內(nèi)執(zhí)行.do文件進(jìn)行仿真,不通過(guò)vivado調(diào)用modelsim,vivado僅用于生成IP核。

2023-12-04 18:26:34 477

477

仿真的工具。synplify:一般用來(lái)進(jìn)行綜合的工具。為什么要用modelsim和synplify呢?因?yàn)閟ynplify是專(zhuān)業(yè)的綜合工具,綜合的效果肯定比ISE自帶的綜合器要強(qiáng)大的多。。。對(duì)于很大

2016-03-15 13:40:51

直接進(jìn)行編寫(xiě),那么我們就需要在文件夾下面對(duì)所用到的文件的屬性進(jìn)行修改。ISE和Modelsim的聯(lián)調(diào)之前的設(shè)置:1.開(kāi)始-所有程序-Xilinx ISE Design Suits ->ISE

2015-01-27 10:21:14

ISE和Modelsim聯(lián)合仿真_修訂版

2014-01-26 22:44:31

用ISE和modelsim聯(lián)合仿真,每次在ISE修改程序后必須把原來(lái)打開(kāi)的modelsim關(guān)閉了再重新打開(kāi)嗎?

2017-02-21 20:40:27

的波形--->運(yùn)行仿真。如果仿真結(jié)果不理想,還得需要重新修改代碼,重復(fù)上述的操作。計(jì)算機(jī)擅長(zhǎng)做重復(fù)的事情,為什么不讓計(jì)算機(jī)代勞呢?我們可以參照Xilinx ISE是如何調(diào)用ModelSim進(jìn)行仿真的

2019-06-03 09:11:11

ISE聯(lián)合Modelsim進(jìn)行仿真,里面介紹得非常詳細(xì)

2018-01-12 15:01:09

大家好!我在使用Modelsim進(jìn)行仿真時(shí),從 ISE 啟動(dòng) Modelsim 仿真是完全正常的,但從 Modelsim 直接建立工程,進(jìn)行仿真,總是提示“Module 'IBUFG

2015-01-26 23:17:51

在使用 ISE 軟件進(jìn)行仿真,仿真工具是 Modelsim,提示錯(cuò)誤,錯(cuò)誤詳情如下: > unisim (ERROR: Library path "d:/Xilinx/14.3

2015-01-19 14:12:08

這次利用Xilinx公司的芯片做FPGA開(kāi)發(fā)的時(shí)候用到了ROM,肯定要對(duì)ROM做仿真,經(jīng)過(guò)了一天的努力,總算可以做仿真了,現(xiàn)在把過(guò)程寫(xiě)出來(lái),供大家參考一下。1.首先需要編譯XINLINX的庫(kù)文件

2012-02-29 10:44:56

各位,小弟最近遇到一個(gè)很奇怪的問(wèn)題。我在使用modelsim進(jìn)行仿真時(shí),無(wú)論是通過(guò)quartus調(diào)用還是直接運(yùn)行modelsim,都會(huì)遇到提示:“error loading design“,從而仿真

2015-08-30 22:14:39

我之前是使用quartus和Modelsim聯(lián)調(diào)的,直接從Quartus里調(diào)用。仿真的時(shí)候可以看到Quartus整個(gè)工程文件下的輸入輸出值和工程里各個(gè)模塊的輸入輸出值都可以看到。但是我現(xiàn)在

2015-10-12 10:41:08

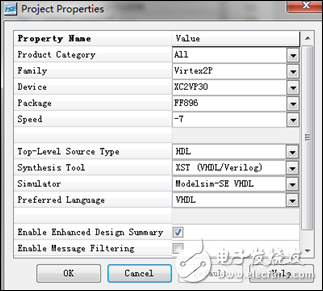

我使用ISE 13.4對(duì)設(shè)計(jì)的代碼進(jìn)行邏輯綜合和布局布線(xiàn)等。寫(xiě)的測(cè)試文件調(diào)用了一個(gè)RAM IP核,見(jiàn)圖1。其中test_HRV_top為測(cè)試文件,調(diào)用了RAM_fangzhen這個(gè)IP核和設(shè)計(jì)頂層

2015-08-29 16:55:16

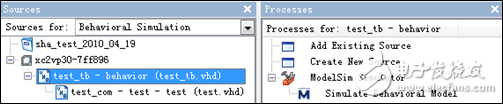

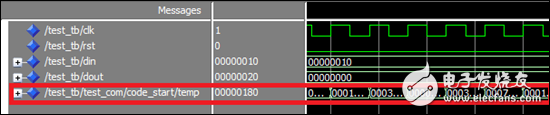

Xilinx ISE 12.2調(diào)用 Modelsim 進(jìn)行行為仿真詳解最近閑來(lái)無(wú)事,整點(diǎn)東西,以饗各位。第一步:新建工程: File->New Project 創(chuàng)建工程 cnt_for_sim

2012-02-29 10:17:25

本帖最后由 eehome 于 2013-1-5 09:54 編輯

Xilinx ISE 12.2 調(diào)用Modelsim進(jìn)行行為仿真詳解

2012-03-05 16:05:08

目的:使用ISE調(diào)用modelsim進(jìn)行仿真,并使用debussy查看仿真波形準(zhǔn)備:安裝ISE、Modelsim和Debussy軟件將C:\modeltech_6.5a\modelsim.ini設(shè)置

2012-03-08 15:27:01

`Xilinx FPGA入門(mén)連載10:Modelsim仿真驗(yàn)證特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 ISE基本設(shè)置好,既然

2015-09-25 12:39:34

`Xilinx FPGA入門(mén)連載5:ISE與Modelsim聯(lián)合仿真之庫(kù)編譯特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm1 操作系統(tǒng)

2015-09-14 12:37:44

`Xilinx FPGA入門(mén)連載6:ISE與Modelsim聯(lián)合仿真之關(guān)聯(lián)設(shè)置特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 ISE

2015-09-16 13:06:48

modelsim仿真DDR3時(shí),出現(xiàn)下面錯(cuò)誤。Instantiation of 'B_MCB' failed. The design unit was not found.并沒(méi)有用ISE聯(lián)合仿真

2016-01-21 10:12:40

如題,如果想用modelsim 仿真ise12.2的工程,應(yīng)該用什么版本的modelsim? 求指教!!

2013-08-26 19:04:37

剛開(kāi)始用modelsim,在ise和modelsim的聯(lián)合仿真中,一般都是從ise中啟動(dòng)modelsim的,但是如果仿真文件有錯(cuò),或者要修改仿真文件,難道都要先關(guān)掉modelsim,然后再在ise中打開(kāi)modelsim,不能不關(guān)閉modelsim直接進(jìn)行修改仿真文件,然后直接進(jìn)行仿真嗎

2015-11-12 10:11:44

`大蝦們,小女子最近調(diào)程序的時(shí)候用到了ise ip core的除法器,但是調(diào)用modelsim仿真的時(shí)候發(fā)現(xiàn)木有進(jìn)行除法啊,單獨(dú)寫(xiě)了個(gè)除法器也還是用不了,這是什么情況呢?(vhdl寫(xiě)的程序哈)`

2013-06-15 11:52:45

在ise調(diào)用modelsim時(shí)出現(xiàn)

2017-01-01 10:29:46

的ModelSim工程文件目錄中,并將*.v中模塊名稱(chēng)改為我自己工程文件中調(diào)用的模塊名。4、將ModelSim跟目錄下的modelsim.ini文件的只讀屬性去掉。5、將compxlib文件所在目錄(即Xilinx

2012-05-15 19:02:08

:\modeltech_10.1c\Xilinx_lib 開(kāi)始編譯XILINX仿真庫(kù),等待完成,如果0 error則正確,D:\..為你安裝MODELSIM的目錄,改為自己的目錄

2017-04-16 20:36:41

請(qǐng)問(wèn)一下在ISE14.6中編譯完modelsim10.0a,在用modelsim進(jìn)行仿真時(shí)會(huì)閃退是怎么回事,有什么解決辦法?期待熱心的你給以指教!

2016-05-19 21:10:18

Altera和Xilinx Modelsim仿真庫(kù)Altera和Xilinx Modelsim仿真庫(kù) 我們通常使用modelsim軟件作為仿真工具,不同階段的仿真使用不同的庫(kù)文件,在開(kāi)始仿真前將庫(kù)

2012-08-10 18:31:02

FPGA基礎(chǔ)篇(三):modelsim仿真的幾個(gè)常見(jiàn)問(wèn)題對(duì)于FPGA開(kāi)發(fā)的流程無(wú)外乎就三步,第一編寫(xiě)程序,第二仿真,第三仿真結(jié)束之后下載到板子。其中仿真是必須經(jīng)歷的過(guò)程,對(duì)于altera的芯片來(lái)說(shuō)

2017-04-15 21:46:29

HDLBencher,同時(shí)又提供了使用 Model Technology 公司的 ModelSim 進(jìn)行仿真的接口。? 實(shí)現(xiàn)(Implementation) 此功能包括了翻譯(Translate

2018-09-27 09:29:57

本人安裝的是Quartus17.0-Lite(配套Modelsim-Altera)添加PLL的IP核,仿真的時(shí)候c0輸出高阻,locked一直輸出低;選用:Cyclone10

2017-11-05 11:59:40

為什么quartusII 調(diào)用modelsim仿真時(shí),modelsim還沒(méi)出波形前就自動(dòng)關(guān)閉,但是單獨(dú)打開(kāi)modelsim時(shí),它又是可以的,求高手解答!!1!!!

2015-10-12 21:32:17

本人使用的是ISE14.7這個(gè)版本,現(xiàn)在安裝modelsim仿真軟件,請(qǐng)問(wèn)最好是下載哪個(gè)版本的啊,求大神支招!非常感謝

2016-10-09 21:47:21

各位大神,本人FPGA初學(xué)者,在使用ISE調(diào)用Modelsim時(shí),出現(xiàn)這樣的問(wèn)題Unable to automatically find executables for simulator 'mti_se' from the following paths:,這個(gè)該怎么解決哇。

2012-09-13 21:12:34

`小弟最近在使用ISE14.7和modelsim聯(lián)合仿真的時(shí)候出現(xiàn)了一些問(wèn)題,百度很久也不能解決,特來(lái)論壇求助各位大哥!!!!真心求助!!!!具體問(wèn)題就是在啟動(dòng)仿真的時(shí)候ISE14.7會(huì)出現(xiàn)一個(gè)警告

2017-09-14 23:07:53

ise沒(méi)啥問(wèn)題,,,用modelsim仿真就這樣了,哪個(gè)哥哥能交下感謝

2018-11-27 11:36:26

我是通過(guò)quartus來(lái)調(diào)用Modelsim的,比如程序?qū)懲曛缶C合完成后調(diào)用Modelsim進(jìn)行仿真。但是如果發(fā)現(xiàn)仿真的結(jié)果不對(duì),我就要去返回修改verilog代碼,再編譯綜合。那么問(wèn)題來(lái)了,此時(shí)

2015-10-10 11:33:01

在quartus 中編好程序,生成仿真需要的 .vho 和 .sdf 文件在用modelsim仿真的時(shí)候出現(xiàn)如下錯(cuò)誤,# ** Error: (vsim-SDF-3250) C:/Users

2016-04-05 13:28:34

時(shí)就能看到像在功能仿真的工程文件層次結(jié)構(gòu),可以找到定義的內(nèi)部信號(hào)。因?yàn)樵谧龊蠓聲r(shí),源文件中的信號(hào)名稱(chēng)已經(jīng)沒(méi)有了,被映射為軟件綜合后自己生成的信號(hào)名,觀(guān)察起來(lái)很不方便。這個(gè)設(shè)置與ISE里綜合右鍵屬性

2012-03-01 11:46:29

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載47:基于仿真的第一個(gè)工程實(shí)例之調(diào)用Modelsim仿真特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2018-02-05 15:37:06

本帖最后由 lee_st 于 2017-10-31 09:24 編輯

在MODELSIM中仿真XILINX工程

2017-10-30 17:06:29

在MODELSIM中仿真XILINX工程

2018-01-24 17:25:05

在ModelSim中添加xilinx仿真庫(kù)的具體步驟

2018-09-12 14:58:15

在A(yíng)ltera Quartus II下如何調(diào)用ModelSim進(jìn)行仿真?

2021-04-30 07:15:55

RT,在用ModelSim進(jìn)行功能仿真的時(shí)候,出現(xiàn)的是二進(jìn)制的數(shù)字。這樣看著很麻煩也不利于觀(guān)察,我在其他資料里看到有用十進(jìn)制顯示的,有沒(méi)有什么方法可以使他顯示成十進(jìn)制,謝謝!

2014-09-02 19:37:06

這里給出大部分的文字,工程和完成的在附件里,我實(shí)在懶得在把文檔補(bǔ)齊截圖Modelsim 進(jìn)行VHDL仿真的預(yù)備知識(shí)這里即將介紹使用Modelsim 進(jìn)行VHDL仿真的預(yù)備知識(shí)(大部分參考至網(wǎng)絡(luò)

2015-11-29 21:35:23

如何在ISE環(huán)境中使用ModelSim仿真

2012-08-20 18:45:23

文件,可以在ISE 中生成設(shè)計(jì)的行為仿真(將設(shè)計(jì)轉(zhuǎn)換為RTL 描述后進(jìn)行的仿真)、轉(zhuǎn)換后仿真(將設(shè)計(jì)轉(zhuǎn)換為Xilinx 器件的基本模塊來(lái)實(shí)現(xiàn)后進(jìn)行的仿真)、映射后仿真(將設(shè)計(jì)用Xilinx 的具體器件

2012-02-24 21:51:12

本帖最后由 diangongshi 于 2012-2-24 21:42 編輯

蓋住了版本號(hào),為的是告訴大家,這個(gè)各個(gè)版本通用。在使用ModelSim軟件對(duì)Xilinx ISE進(jìn)行后仿真時(shí),需要

2012-02-24 21:40:17

本帖最后由 阿兮 于 2014-9-17 18:56 編輯

小弟初學(xué)者,使用ISE仿真(調(diào)用Modelsim)時(shí)出現(xiàn)以下錯(cuò)誤,希望各位大哥大姐幫忙看下怎么解決,拜謝!ERROR

2014-09-17 18:56:55

最近幾天在學(xué)習(xí)用quartus調(diào)用modelsim進(jìn)行仿真,可是仿真的時(shí)候一直出現(xiàn)這種情況,一直處于loading的狀態(tài)。求幫助。另外我的版本是quartus9,modelsim10.1c64位。重裝也沒(méi)用。

2014-10-26 16:12:08

利用ise編寫(xiě)的fpga工程,采用modelsim進(jìn)行仿真,如何提高仿真的速度?這里提高速度指的不是優(yōu)化程序,而是采用提高電腦硬件配置,或者采用硬件加速,或者軟硬件聯(lián)合仿真的方法進(jìn)行加速。請(qǐng)高手具體

2016-04-16 20:32:36

現(xiàn)在做仿真,每次在ISE上編輯代碼然后直接launch關(guān)聯(lián)的Modelsim進(jìn)行仿真,稍微做一點(diǎn)修改保存后就需要關(guān)掉Modelsim,再?gòu)男聫?b class="flag-6" style="color: red">ISE上重新luanch仿真。這樣又重新得填寫(xiě)信號(hào),改

2017-08-28 21:06:27

沒(méi)用過(guò)ISE,不知道生成的IP核文件夾中 ,哪些是需要添加到modelsim中用于仿真的文件 。拿ram舉例,仿真庫(kù)文件還應(yīng)該添加哪些內(nèi)容。希望大神們指導(dǎo)下 多謝

2018-12-18 17:58:32

本文主要描述了如何在 QUARTUS II 中輸入程序文件,生成網(wǎng)表及標(biāo)準(zhǔn)延時(shí)文件,然后通過(guò)MODELSIM 進(jìn)行功能仿真與后仿真的過(guò)程,主要為圖解,含全部代碼及仿真波形。

2009-07-22 15:44:53 0

0 我把我用到的軟件說(shuō)明一下。如果你發(fā)現(xiàn)根據(jù)我的操作,你還是解決不了ModelSim后仿真的問(wèn)題,那就可能是軟件版本的問(wèn)題。

2009-07-22 15:46:27 0

0 FPGACPLD設(shè)計(jì)工具——Xilinx ISE使用詳解的主要內(nèi)容:第1章 ISE系統(tǒng)簡(jiǎn)介第2章 工程管理器與設(shè)計(jì)輸入工具第3章 ModelSim仿真工具第4章 ISE中集成的綜合工具第5章 約束第6章

2009-07-24 16:06:58 197

197 我想很多人跟我一樣,被ModelSim的后仿真搞的頭暈?zāi)X脹。為了這個(gè)問(wèn)題,我在網(wǎng)上找了很多的資料,但發(fā)現(xiàn)這些資料往往說(shuō)的不明白。一些步驟被作者有意無(wú)意地省略掉,這常常給讀

2010-03-31 09:46:36 112

112 xilinx ISE設(shè)計(jì)套裝10.1下載

2010-04-17 16:15:18 1915

1915 一、配置Modelsim ISE的Xilinx的仿真庫(kù) 1、編譯仿真庫(kù): A、先將Modelsim安裝目錄C=Modeltech_6.2b下面的modelsim.ini改成存檔格式(取消只讀模式); B、在DOS環(huán)境中,進(jìn)入Xilinx的根目錄,然后依次進(jìn)入

2011-03-30 10:19:07 307

307 ModelSim為HDL仿真工具,我們可以利用該軟件來(lái)實(shí)現(xiàn)對(duì)所設(shè)計(jì)的VHDL或Verilog程序進(jìn)行仿真,支持IEEE常見(jiàn)的各種硬件描述語(yǔ)言標(biāo)準(zhǔn)。可以進(jìn)行兩種語(yǔ)言的混合仿真,但推薦大家只對(duì)一種語(yǔ)言

2011-04-19 20:52:46 151

151 1、熟悉Xilinx的ISE 軟件的設(shè)計(jì)流程; 2、并使用移位相加運(yùn)算設(shè)計(jì)一個(gè)4*4位的乘法器; 3、掌握ISE 仿真器或Modelsim仿真軟件的使用方法; 4、用ISE 仿真器或Modelsim仿真軟件對(duì)設(shè)計(jì)進(jìn)行仿真

2011-05-20 15:32:45 79

79 ModelSim為HDL仿真工具,我們可以利用該軟件來(lái)實(shí)現(xiàn)對(duì)所設(shè)計(jì)的VHDL或Verilog程序進(jìn)行仿真,支持IEEE常見(jiàn)的各種硬件描述語(yǔ)言標(biāo)準(zhǔn)。可以進(jìn)行兩種語(yǔ)言的混合仿真,但推薦大家只對(duì)一種語(yǔ)言

2011-05-27 16:41:59 132

132 本教程主要是向ISE的初學(xué)者描述和演示, 在XILINX的ISE集成軟件環(huán)境中如何用VHDL和原理圖的方式進(jìn)行設(shè)計(jì)輸入如何用 ModelSim 仿真工具對(duì)設(shè)計(jì)進(jìn)行功能仿真和時(shí)序仿真如何實(shí)現(xiàn)設(shè)計(jì).

2011-11-01 14:44:07 0

0 Altera ModelSim 6.5仿真入門(mén)教程,需要的可自行下載。 平臺(tái) 軟件:ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition 內(nèi)容 1 設(shè)計(jì)流程 使用ModelSim仿真的基本流程為: 圖1.1 使用 ModelSim仿真的基本

2012-08-15 15:40:24 255

255 基于Xilinx ISE的modelsim仿真教程

2015-11-30 15:52:56 8

8 本章為ModelSim的初級(jí)教程,讀者讀完本章可以較為熟練的使用ModelSim進(jìn)行設(shè)計(jì)仿真,本章沒(méi)有也不可能涉及ModelSim的各個(gè)方面,要想全面的掌握ModelSim可以參閱軟件文檔。

2015-12-24 18:29:37 0

0 xilinx_ise9.01中文教程 xilinx_ise9.01中文教程

2016-02-18 18:16:58 0

0 xilinx-ise 新手教程VHDL的,感興趣的可以看看。

2016-09-27 15:19:03 77

77 以前在用modelsim對(duì)Xilinx進(jìn)行器件庫(kù)編譯時(shí),我用的比較多的是直接在ISE中編譯器件庫(kù),感覺(jué)很方便簡(jiǎn)單,就是編譯時(shí)間有點(diǎn)長(zhǎng)。自從前段時(shí)間,在自己電腦裝MathType,360殺毒軟件將它

2017-02-08 12:20:12 207

207

由于兩個(gè)軟件都是較新的版本,在配合使用過(guò)程中出現(xiàn)的問(wèn)題會(huì)比較多,且與之前版本的解決辦法有出入。 1.在使用ModelSim軟件對(duì)Xilinx ISE進(jìn)行后仿真時(shí),需要先編譯Xilinx的仿真庫(kù)。這個(gè)

2017-02-08 15:20:11 826

826 最近在學(xué)習(xí)FPGA,使用ModelSim對(duì)ISE進(jìn)行仿真,首先要將ISE和ModelSim進(jìn)行有效的關(guān)聯(lián),折騰了一天終于弄懂了如何將他們有效的關(guān)聯(lián)在一起。 (1)首先要安裝ModelSim,注意

2017-02-09 01:34:11 1385

1385 在System Generator做了點(diǎn)仿真,驗(yàn)證成功之后,自動(dòng)生成了testbench文件,然后在ISE中打開(kāi)生成的工程,調(diào)用Modelsim選擇behavior仿真......

2017-02-11 11:02:02 1911

1911

我們經(jīng)常使用Xilinx Ise與Modelsim聯(lián)合仿真,但是經(jīng)常出現(xiàn)一些由于庫(kù)沒(méi)有編譯而出現(xiàn)的錯(cuò)誤!下面是我總結(jié)的方法:

2017-02-11 13:43:06 1348

1348

當(dāng)ISE調(diào)用ModelSim進(jìn)行仿真的時(shí)候,如果在FPGA設(shè)計(jì)中使用了Xilinx提供的的IP core或者其他的原語(yǔ)語(yǔ)句,ModelSim不添加Xilinx相應(yīng)的庫(kù)文件的話(huà),是無(wú)法仿真的。

2017-02-11 15:22:37 1274

1274

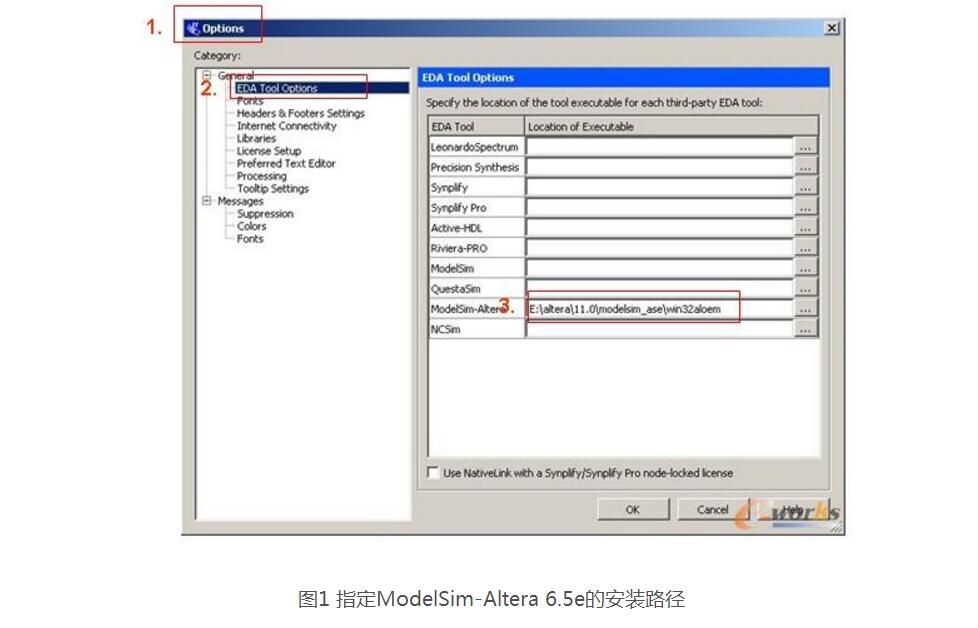

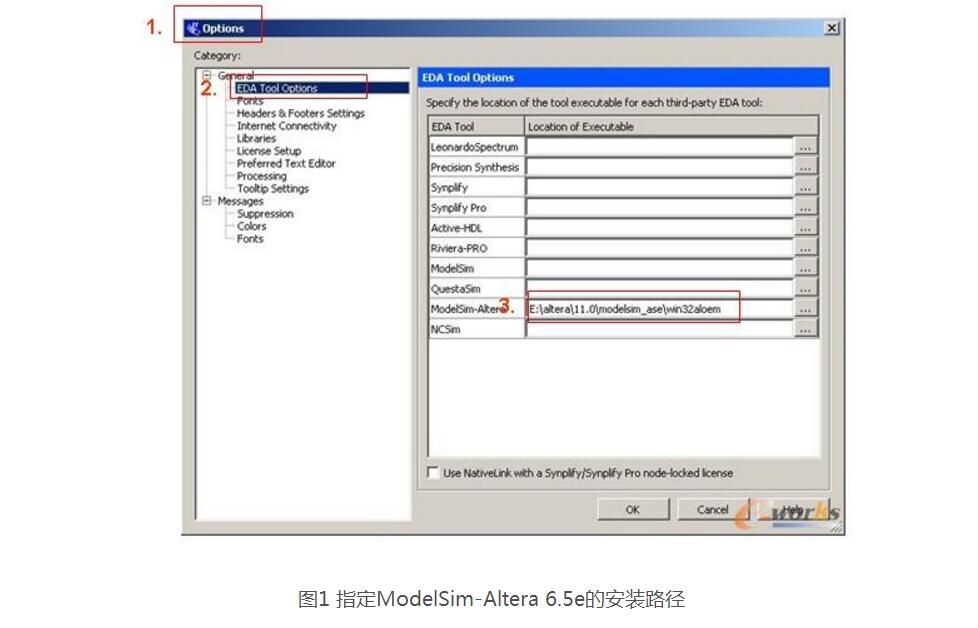

本文主要詳細(xì)介紹了在Quartus II 11.0中調(diào)用ModelSim-Altera 6.5e,另外還介紹了Quartus II調(diào)用modelsim無(wú)縫仿真教程。

2018-05-18 10:39:16 34625

34625

本次使用的Vivado版本為Vivado_2017.3版本,從Xilinx官方文檔可以了解到,該版本的Vivado只支持Modelsim10.6或者更高版本,但是筆者只有Modelsim

2019-03-30 09:51:46 16946

16946

是Modelsim,但是Modelsim不是仿真,嚴(yán)格來(lái)講Modelsim只是仿真所需的工具而已,又或者說(shuō)Modelsim只是學(xué)習(xí)仿真的一部小插曲而已。除此之外,筆者也認(rèn)為仿真可以是驗(yàn)證語(yǔ)言,但是驗(yàn)證語(yǔ)言卻不是仿真,因?yàn)轵?yàn)證語(yǔ)言只是仿真的一小部分而已,事實(shí)上仿真也不一定需要驗(yàn)

2019-04-30 18:24:00 23

23 本文檔的主要內(nèi)容詳細(xì)介紹的是結(jié)合實(shí)例,通過(guò)圖片及配套文字解說(shuō),分步驟詳細(xì)介紹了Quartus13.0環(huán)境中調(diào)用Modelsim進(jìn)行功能仿真。

2019-07-01 08:00:00 7

7 的 ModelSim 自動(dòng)仿真,所謂自動(dòng)仿真,其實(shí)是在 Quartus II 中調(diào)用 ModelSim 軟件來(lái)進(jìn)行仿真。 在調(diào)用過(guò)程中,Quartus II 會(huì)幫我們完成 ModelSim 中的所有操作,我們

2021-07-23 10:51:17 1710

1710

4.1 新建仿真工程 在開(kāi)始動(dòng)手仿真之前,首先,我們需要?jiǎng)?chuàng)建一個(gè)文件夾用來(lái)放置我們的 ModelSim 仿真工程文件,這里我們就在之前創(chuàng)建的 Quartus 工程目錄下的 simulation

2021-07-23 11:10:48 3514

3514 )文件和延時(shí)(.sdo)文件,其實(shí)我們?cè)谧詣?dòng)仿真的配置仿真功能中已經(jīng)生成了,當(dāng)我們配置好仿真功能之后,我們?cè)?Quartus 進(jìn)行一次全編譯。 這時(shí),我們打開(kāi) Quartus 工程目錄

2021-07-23 11:55:41 1915

1915 調(diào)用第三方仿真軟件查看波形的過(guò)程中存在的一些問(wèn)題。 1、添加新的觀(guān)測(cè)信號(hào)需要重新仿真 Vivado直接調(diào)用Modelsim/QuestaSim進(jìn)行仿真時(shí),波形文件里默認(rèn)只會(huì)出現(xiàn)仿真最頂層中包含

2021-09-02 10:12:06 7274

7274

通過(guò)該圖,我們可以看出,這個(gè)工程是我們之前做功能仿真的工程,當(dāng)我們關(guān)閉 ModelSim之后,我們?cè)俅未蜷_(kāi) ModelSim 這個(gè)軟件,它會(huì)自動(dòng)記錄上一個(gè)我們使用的工程并打開(kāi)。我們就直接在這個(gè)工程

2022-07-18 14:17:25 894

894 的時(shí)間在5分鐘左右。為此,通過(guò)不斷地學(xué)習(xí),終于將波形仿真的各個(gè)事項(xiàng)了解清楚。這里做一下記錄,方便以后回顧。

2022-11-29 09:52:13 2374

2374 Modelsim是十分常用的外部仿真工具,在Vivado中也可以調(diào)用Modelsim進(jìn)行仿真,下面將介紹如何對(duì)vivado進(jìn)行配置并調(diào)用Modelsim進(jìn)行仿真,在進(jìn)行仿真之前需要提前安裝Modelsim軟件。

2023-07-24 09:04:43 1817

1817

ModelSim為HDL仿真工具,我們可以利用該軟件來(lái)實(shí)現(xiàn)對(duì)所設(shè)計(jì)的VHDL或Verilog程 序進(jìn)行仿真,支持IEEE常見(jiàn)的各種硬件描述語(yǔ)言標(biāo)準(zhǔn)。可以進(jìn)行兩種語(yǔ)言的混合仿真,但 推薦大家只對(duì)一種語(yǔ)言仿真。

2024-01-14 09:47:47 0

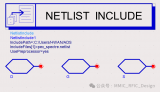

0 ADS是支持調(diào)用spice/spectre等網(wǎng)表文件進(jìn)行仿真的,可以用NetlistInclude控件來(lái)進(jìn)行調(diào)用。

2024-03-07 09:57:11 226

226

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論