為了更好的控制時(shí)鐘,Virtex-6器件分成若干個(gè)時(shí)鐘區(qū)域,最小器件有6個(gè)區(qū)域,最大器件有18個(gè)區(qū)域。每個(gè)時(shí)鐘區(qū)域高40個(gè)CLB。在時(shí)鐘設(shè)計(jì)中,推薦使用片上專用的時(shí)鐘資源,不推薦使用本地時(shí)鐘(如邏輯產(chǎn)生的時(shí)鐘)。

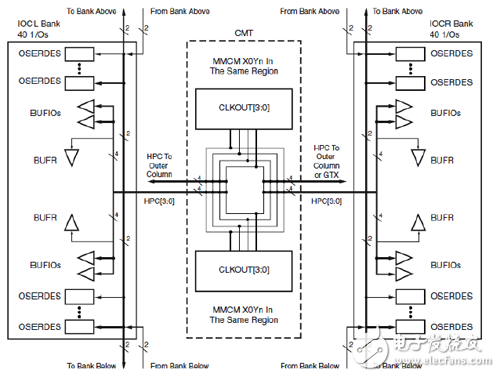

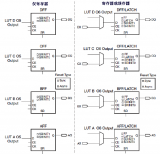

每個(gè)Virtex-6的中間列包含了專門配置引腳(CFG),該列的其余區(qū)域?yàn)镃LB。其右邊排列著一個(gè)CMT列。每個(gè)區(qū)域(40個(gè)CLB高)對(duì)應(yīng)一個(gè)CMT。一個(gè)CMT包含2個(gè)混合模式時(shí)鐘管理單元(MMCM),還有32個(gè)垂直全局時(shí)鐘樹。每個(gè)時(shí)鐘區(qū)域的中間方向有一個(gè)時(shí)鐘行(HROW),包含12個(gè)水平時(shí)鐘線,6個(gè)BUFR和最多12個(gè)BUFH。Virtex-6的時(shí)鐘資源圖如圖5-7所示。

每個(gè)Virtex-6 FPGA中間列的左右兩邊各有一個(gè)I/O列,分別標(biāo)號(hào)為IOCL和IOCR,I/O列和中間列之間是CLB。

每個(gè)區(qū)域/BANK的中間有一個(gè)水平時(shí)鐘行(HROW),HROW包含水平時(shí)鐘線、BUFG和BUFH。內(nèi)部I/O列包含8個(gè)全局時(shí)鐘引腳對(duì)(GC),所有的I/O列包含4個(gè)Clock-Capable引腳對(duì)(CC),可以連到BUFIO和BUFR。每個(gè)BANK的4個(gè)CC中的兩個(gè)可以連到相鄰區(qū)域的BUFIO上。另外,中間列的BUFR和CC腳可以直接驅(qū)動(dòng)同一個(gè)區(qū)域的MMCM,或者間接通過垂直全局時(shí)鐘線驅(qū)動(dòng)BUFG。

Virtex-6器件的片內(nèi)時(shí)鐘資源為片內(nèi)的同步元件提供時(shí)鐘,片內(nèi)時(shí)鐘資源有3種類型,分別是全局時(shí)鐘資源、區(qū)域時(shí)鐘資源、I/O時(shí)鐘資源。

圖5-7 Virtex-6的時(shí)鐘資源圖

一、 全局時(shí)鐘資源

全局時(shí)鐘是一種專用互連網(wǎng)絡(luò),它可以降低時(shí)鐘歪斜、占空比失真和功耗,提高抖動(dòng)容限。

Virtex-6的全局時(shí)鐘資源設(shè)計(jì)了專用時(shí)鐘緩沖與驅(qū)動(dòng)結(jié)構(gòu),從而使全局時(shí)鐘到達(dá)CLB、IOB和BRAM的延時(shí)最小。

全局時(shí)鐘資源由以下通路和組件構(gòu)成。

二、 全局時(shí)鐘輸入

Virtex-6全局時(shí)鐘輸入包含專用的全局時(shí)鐘輸入管腳和全局輸入緩沖器。全局時(shí)鐘輸入管腳可以直接連接外部單端或差分時(shí)鐘;全局輸入緩沖器(IBUFG)是FPGA內(nèi)部與專用全局時(shí)鐘輸入管腳相連的首級(jí)全局緩沖器。

Virtex-6器件里有8個(gè)全局時(shí)鐘輸入。8個(gè)全局時(shí)鐘輸入可以連接到電路板上的8個(gè)時(shí)鐘輸入。

時(shí)鐘輸入管腳可以不用作時(shí)鐘輸入引腳,而用作普通I/O。

外部單端或差分時(shí)鐘通過專用全局時(shí)鐘輸入引腳進(jìn)入FPGA,在FPGA內(nèi)部,信號(hào)必須接入全局輸入緩沖器(IBUFG),否則在布局布線時(shí)會(huì)報(bào)錯(cuò)。

可以在HDL代碼中例化全局輸入緩沖器。

(1) 全局時(shí)鐘緩沖器。

每個(gè)Virtex-6器件有32個(gè)全局時(shí)鐘緩沖器,時(shí)鐘信號(hào)只有經(jīng)過BUFG之后才可以驅(qū)動(dòng)全局時(shí)鐘網(wǎng)絡(luò)。一個(gè)全局時(shí)鐘輸入能直接從差分全局時(shí)鐘引腳對(duì)的P端連接到全局時(shí)鐘緩沖器的輸入。每個(gè)差分全局時(shí)鐘引腳對(duì)可以連接到PCB上的一個(gè)差分或單端時(shí)鐘。如果使用單端時(shí)鐘,則必須使用引腳對(duì)的P端,因?yàn)橹挥羞@一引腳上存在直接連接。必須將一個(gè)單端時(shí)鐘連接到差分全局時(shí)鐘引腳的正(P)端。如果單端時(shí)鐘連接到差分引腳對(duì)的P端,則不能用其N端作為另一個(gè)單端時(shí)鐘輸入。不過,可以將其用作普通I/O。

全局時(shí)鐘緩沖器的輸入源包括以下幾種。

全局時(shí)鐘輸入。

內(nèi)部I/O列的同一區(qū)域Clock-Capable時(shí)鐘輸入。

時(shí)鐘管理單元(CMT)。

其他全局時(shí)鐘緩沖器的輸出(BUFG)。

通用互連。

區(qū)域時(shí)鐘緩沖器(BUFR)。

千兆收發(fā)器。

Virtex-6 FPGA的CC輸入間接通過MMCM列中的垂直時(shí)鐘網(wǎng)絡(luò)驅(qū)動(dòng)BUFG。32個(gè)BUFG分成兩組,每組16個(gè),分別位于器件的頂部和底部。頂部的MMCM只能驅(qū)動(dòng)頂部的16個(gè)BUFG,底部的MMCM只能驅(qū)動(dòng)底部的BUFG。

全局時(shí)鐘緩沖器還可配置成多路復(fù)用器,可以在2個(gè)輸入時(shí)鐘之間切換。這兩個(gè)時(shí)鐘可以是同步的,也可以是異步的,多路復(fù)用器的輸出是無毛刺的時(shí)鐘。

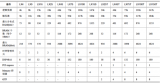

全局時(shí)鐘緩沖器的多種原語模型如表5-6所示。

表5-6 全局時(shí)鐘緩沖器的原語

(2) 全局時(shí)鐘樹和時(shí)鐘網(wǎng)絡(luò)(GCLK)。

Virtex-6中的全局時(shí)鐘樹和時(shí)鐘網(wǎng)絡(luò),如果未被使用,它就是斷開的,這可以降低功耗。另外,時(shí)鐘樹還具有對(duì)負(fù)載/扇出的管理功能。所有全局時(shí)鐘線和緩沖器都以差分形式實(shí)現(xiàn),這有助于改善占空比、提高對(duì)共模噪聲的抑制能力。在Virtex-6架構(gòu)中,全局時(shí)鐘線不僅可以用作時(shí)鐘,還可以當(dāng)作其他信號(hào)線,例如扇出較大的信號(hào)。

(3) 時(shí)鐘區(qū)域。

Virtex-6通過使用時(shí)鐘區(qū)域,改善了時(shí)鐘的分配性能。每個(gè)時(shí)鐘區(qū)域最多可有12個(gè)全局時(shí)鐘。這12個(gè)全局時(shí)鐘可由32個(gè)BUFG的任12個(gè)驅(qū)動(dòng)。時(shí)鐘區(qū)域的大小固定為40個(gè)CLB高,半個(gè)晶片寬。因此大尺寸的器件有更多的時(shí)鐘區(qū)域。CMT和全局時(shí)鐘資源位于包含配置引腳中間列的右邊,如圖5-8所示。

?

圖5-8 XC6VLX75T的時(shí)鐘區(qū)域

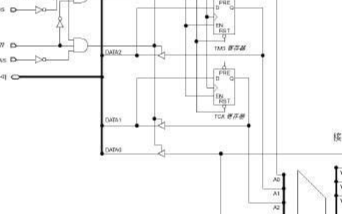

三、 區(qū)域時(shí)鐘資源

區(qū)域時(shí)鐘網(wǎng)絡(luò)是獨(dú)立于全局時(shí)鐘網(wǎng)絡(luò)的。它與全局時(shí)鐘不同,區(qū)域時(shí)鐘信號(hào)BUFR的作用區(qū)域最多為三個(gè)時(shí)鐘區(qū)域,這些網(wǎng)絡(luò)對(duì)于源同步接口設(shè)計(jì)尤其有用。

區(qū)域時(shí)鐘控制資源和網(wǎng)絡(luò)由以下通路和組件構(gòu)成:

(1) Clock-Capable I/O。

每個(gè)時(shí)鐘區(qū)域中有4個(gè)Clock-Capable I/O引腳對(duì)。每個(gè)BANK中有4個(gè)專用Clock-Capable I/O位置。當(dāng)用作時(shí)鐘輸入時(shí),Clock-Capable引腳可以驅(qū)動(dòng)BUFIO和BUFR。

如果用作單端時(shí)鐘引腳,如“全局時(shí)鐘緩沖器”中所述,外部單端時(shí)鐘必須接到引腳對(duì)的P端,因?yàn)橹挥羞@一引腳上存在直接連接。

(2) I/O時(shí)鐘緩沖器(BUFIO)。

BUFIO是用來驅(qū)動(dòng)I/O列內(nèi)的專用時(shí)鐘網(wǎng)絡(luò),這個(gè)專用的時(shí)鐘網(wǎng)絡(luò)獨(dú)立于全局時(shí)鐘資源,適合采集源同步數(shù)據(jù)。BUFIO只能由位于同一時(shí)鐘區(qū)域的Clock-Capable I/O驅(qū)動(dòng)。一個(gè)時(shí)鐘區(qū)域有4個(gè)BURIO,其中的2個(gè)可以驅(qū)動(dòng)相鄰區(qū)域的I/O時(shí)鐘網(wǎng)絡(luò)。BUFIO不能驅(qū)動(dòng)邏輯資源(CLB、BRAM等),因?yàn)镮/O時(shí)鐘網(wǎng)絡(luò)只存在于I/O列中。

可以調(diào)用BUFIO的原語來使用它。

(3) 區(qū)域時(shí)鐘緩沖器(BUFR)。

BUFR可以驅(qū)動(dòng)其所在時(shí)鐘區(qū)域中的6個(gè)區(qū)域時(shí)鐘網(wǎng)絡(luò)和相鄰區(qū)域中的6個(gè)時(shí)鐘網(wǎng)絡(luò)。與BUFIO不同,BUFR不僅可以驅(qū)動(dòng)其所在時(shí)鐘區(qū)域和相鄰時(shí)鐘區(qū)域中的I/O邏輯,還可以驅(qū)動(dòng)CLB、BRAM等。BUFR可由CC引腳、本地時(shí)鐘、GT以及MMCM高性能時(shí)鐘驅(qū)動(dòng)。BUFR對(duì)于要求跨時(shí)鐘域或串并轉(zhuǎn)換的源同步應(yīng)用來說,是理想的選擇。

可以通過調(diào)用BUFR原語來使用它。

(4) 區(qū)域時(shí)鐘網(wǎng)絡(luò)。

除了全局時(shí)鐘樹和全局時(shí)鐘網(wǎng)絡(luò),Virtex-6器件還包含區(qū)域時(shí)鐘網(wǎng)絡(luò)。和全局時(shí)鐘樹一樣,這些區(qū)域時(shí)鐘樹也是為低歪斜SKEW和低功耗操作設(shè)計(jì)的。區(qū)域時(shí)鐘網(wǎng)絡(luò)的傳播是僅限于一個(gè)時(shí)鐘區(qū)域。一個(gè)時(shí)鐘區(qū)域包含6個(gè)獨(dú)立的區(qū)域時(shí)鐘網(wǎng)絡(luò)。

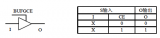

要進(jìn)入?yún)^(qū)域時(shí)鐘網(wǎng)絡(luò),必須例化BUFR。一個(gè)BUFR最多可以驅(qū)動(dòng)兩個(gè)相鄰時(shí)鐘區(qū)域中的區(qū)域時(shí)鐘,如圖5-9所示。此時(shí),BUFR的作用區(qū)域?yàn)槿齻€(gè)時(shí)鐘區(qū)域。頂部和底部區(qū)域中BUFR只能連接相鄰的一個(gè)時(shí)鐘區(qū)域,也就是說,頂部的BUFR連接它所在的下面一個(gè)相鄰區(qū)域。底部的BUFR只能連接它所在的上邊一個(gè)相鄰區(qū)域。因此,底部和頂部BUFR的作用區(qū)域?yàn)閮蓚€(gè)時(shí)鐘區(qū)域。

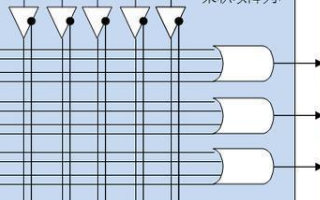

圖5-9 區(qū)域時(shí)鐘和時(shí)鐘網(wǎng)絡(luò)

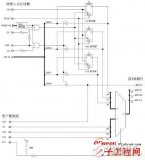

(5) 水平時(shí)鐘緩沖器(BUFH)。

BUFH驅(qū)動(dòng)區(qū)域中的水平全局時(shí)鐘樹,如圖5-10所示,每個(gè)區(qū)域有12個(gè)BUFH,每個(gè)BUFH有一個(gè)CE腳,該引腳可控制時(shí)鐘動(dòng)態(tài)開關(guān)。BUFH可由以下幾種資源驅(qū)動(dòng)。

同一區(qū)域的MMCM輸出。

BUFG輸出。

局部互聯(lián)。

同一區(qū)域內(nèi)部inner columns的CC引腳。

圖5-10 時(shí)鐘區(qū)域中BUFH位置圖

可以通過時(shí)鐘CE腳關(guān)掉時(shí)鐘來節(jié)省功耗。同BUFG驅(qū)動(dòng)兩個(gè)相鄰區(qū)域相比,BUFH的功耗更低。

BUFH的原語如表5-9所示。

表5-9 BUFH的原語

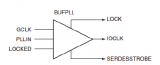

(6) 高性能時(shí)鐘(HPC-High Performance Clock)。

Virtex-6每個(gè)I/O列包含4個(gè)HPC。這些時(shí)鐘由MMCM電源驅(qū)動(dòng),不由VCCINT供電,因此,這些時(shí)鐘能改善JITTER和占空比。HPC結(jié)構(gòu)圖如圖5-11所示,在I/O列中,HPC連接BUFIO,驅(qū)動(dòng)I/O邏輯。4個(gè)HPC中的2個(gè)可以不通過多區(qū)域BUFIO直接驅(qū)動(dòng)I/O BANK(上和下BANK)。HPC可以不通過另一個(gè)時(shí)鐘緩沖器直接連接到OSERDES,提供了一個(gè)改善JITTER和占空比性能的時(shí)鐘。HPC沒有專用緩沖器與它相連,ISE軟件自動(dòng)檢查設(shè)計(jì)中IOLOGIC的連接,確定HPC的連接。HPC能驅(qū)動(dòng)同一區(qū)域中的BUFR,支持源同步接口設(shè)計(jì)。

圖5-11 HPC結(jié)構(gòu)圖

四、 I/O時(shí)鐘

第三種時(shí)鐘控制資源是I/O時(shí)鐘,其速度非常快,可用于局部化的I/O串行器/解串器電路。I/O時(shí)鐘信號(hào)只驅(qū)動(dòng)一個(gè)區(qū)域。這些I/O時(shí)鐘網(wǎng)絡(luò)對(duì)于源同步設(shè)計(jì)尤其有用。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論