9.3 ChipScope Pro內(nèi)核插入器

ChipScope Pro內(nèi)核插入器的文件后綴名為cdc。在ISE工程中可以創(chuàng)建一個(gè)新的cdc程序,也可以在實(shí)現(xiàn)流程中激活內(nèi)核插入器。

注意:使用內(nèi)核插入器之前,要注意一些工程項(xiàng)目的屬性設(shè)臵。

(1) 如果采用XST綜合工具,將【Keep Hierarchy】屬性設(shè)置成【Yes】或【Soft】,禁止XST工具對(duì)設(shè)計(jì)的優(yōu)化,保留原來設(shè)計(jì)層次,同時(shí)也保留了NET網(wǎng)絡(luò)節(jié)點(diǎn)名稱。設(shè)置方法如下。

選擇【Edit】→【Preferences】,打開屬性對(duì)話框。

選擇【Processes】頁。

設(shè)臵屬性顯示下拉框?yàn)椤?a target="_blank">Advanced】,單擊【OK】。

右擊【Synthesize】,選擇【Properties】選項(xiàng)。

設(shè)臵【Keep Hierarchy】屬性為【Yes】或【Soft】,單擊【OK】。

(2) 正確設(shè)置比特流生成選項(xiàng)。

在Project Navigator里,單擊【Generate Programming File】右鍵,選擇【Properties】選項(xiàng)。

選擇【Startup options】頁。

選擇【FPGA Start-Up Clock】下拉框,JTAG Clock啟動(dòng)時(shí)鐘。

接下來,介紹如何在ISE的環(huán)境下調(diào)用ChipScope的內(nèi)核插入器(Core Inserter),以及內(nèi)核插入器的各種參數(shù)的含義及其配置方法。

1. 運(yùn)行ISE 11.1,打開設(shè)計(jì)的工程項(xiàng)目。

2. 創(chuàng)建CDC文件。在ISE11.1的界面下,有兩個(gè)創(chuàng)建CDC文件的方法:

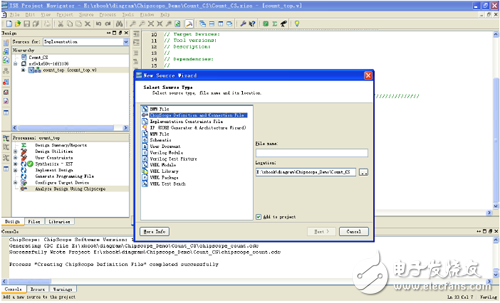

單擊選擇【Project】→【New Source】,彈出源程序設(shè)臵界面,選擇【ChipScope Definition and Connection File】,輸入文件名,如圖9-28所示。單擊【Next】,按照缺省設(shè)臵產(chǎn)生和配臵調(diào)試內(nèi)核,直到【Finish】生成.cdc文件。

注意:只有安裝了ChipScope Pro 11.1,才可以在ISE 11.1的【New Source】里出現(xiàn)【ChipScope Definition and Connection File】。

圖9-28 【New Source Wizard】源程序類型選擇界面

選擇【Project】→【Add Source】(【Add Copy of Source】),選擇已經(jīng)存在的.cdc文件。

3. ChipScope內(nèi)核插入器的屬性和參數(shù)設(shè)置。

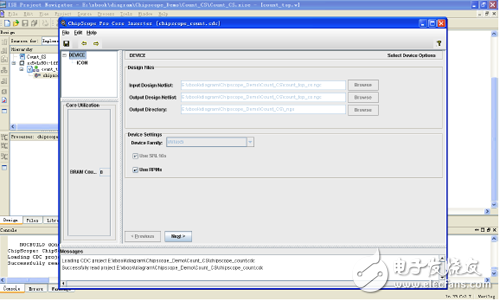

(1) 在【Sources in Project】窗口中,雙擊cdc文件。彈出的內(nèi)核插入器界面如圖9-29所示,設(shè)置Chipscope Pro的參數(shù)。

圖9-29 內(nèi)核插入器用戶界面

菜單欄中的菜單項(xiàng)及其功能有:

【File】菜單:包含常見的文件操作命令,如【Open Project】、【Save】、【Save As】。【Refresh Netlist】用于手動(dòng)更新網(wǎng)表。

【Edit】菜單:包含創(chuàng)建新的集成邏輯分析單元【New ILA Unit】,或者創(chuàng)建新的ATC2單元【New ATC2 Unit】,刪除單元【Remove Unit】,以及參數(shù)設(shè)臵【Preferences】等命令。

【Insert】菜單:包含【Insert Core.】命令,當(dāng)設(shè)臵ILA Core的各項(xiàng)參數(shù)后,可以利用這個(gè)命令把集成邏輯分析儀的網(wǎng)表插入到原設(shè)計(jì)的網(wǎng)表中。

【Design Files】設(shè)計(jì)文件選項(xiàng)組,有如下幾個(gè)選項(xiàng):

指定輸入設(shè)計(jì)的網(wǎng)表

單擊【Browse】,選擇輸入設(shè)計(jì)所在的目錄

修改輸出設(shè)計(jì)網(wǎng)表和輸出目錄(如果核插入器在ISE里激活,那么輸入網(wǎng)表和輸出網(wǎng)表、目錄、器件型號(hào)等參數(shù)自動(dòng)填入,在這鐘情況下,這些參數(shù)只能在ISE工程屬性中修改,不在核插入器里修改。)

工程參數(shù)

【Device Setting】器件設(shè)置選項(xiàng)組:

【Device Family】:選擇目標(biāo)FPGA器件家族,內(nèi)核生成器會(huì)生成針對(duì)該器件優(yōu)化的ICON和捕獲內(nèi)核。

【Use SRL16s】:用來控制是否用SRL16和SRL16E邏輯生成內(nèi)核,如果不選擇該選項(xiàng),將會(huì)用觸發(fā)器和多路選擇器來代替,影響生成核的大小和性能。缺省設(shè)臵為使能。

【Use RPMs 】:用來控制是否用相關(guān)布局宏(RPMs)生成一個(gè)獨(dú)立的內(nèi)核,該復(fù)選框能阻止布局布線器對(duì)區(qū)域內(nèi)放臵ChipScope Pro內(nèi)核的邏輯進(jìn)行布局優(yōu)化。如果設(shè)計(jì)中占用了大部分的邏輯資源,這些布局限制有可能不被滿足。

【Core Utilization】選項(xiàng)組:內(nèi)核生成器的左邊是內(nèi)核資源利用顯示窗口,列出插入設(shè)計(jì)網(wǎng)表中的ChipScope核資源利用情況,包括查找表(LUT), 觸發(fā)器 (FF)和塊RAM (BRAM)。

注意:只有Spartan-3、Spartan-3E、Spartan-3A、Spartan-3A DSP和Virtex-4器件家族顯示ChipScope核資源利用特性。

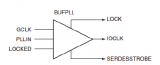

(2) ICON核配置選項(xiàng)設(shè)置。在圖9-29中單擊【Next】,彈出ICON核配置選項(xiàng)設(shè)置界面,如圖9-30所示。

圖9-30 ICON核配置選項(xiàng)界面

【Boundary Scan Chain】下拉選擇框:邊界掃描鏈,分析儀可以通過USER1、USER2、USER3或USER4邊界掃描鏈與ChipScope內(nèi)核通信。(Spartan-3、Spartan-3E、Spartan-3A或Spartan-3A DSP器件不支持該選項(xiàng)。)

可以禁止BUFG插入。

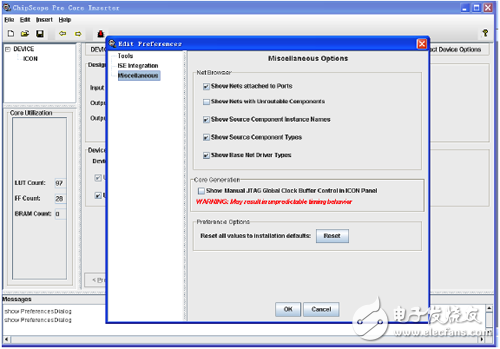

打開【Edit】菜單→【Preferences】屬性,彈出【Edit Preferences】屬性編輯對(duì)話窗,如圖9-31所示。

使能JTAG全局時(shí)鐘緩沖器控制:在【Miscellaneous】選項(xiàng)卡里,【Show Manual JTAG Global Clock Buffer Control in ICON Panel】復(fù)選框選中。

禁止JTAG時(shí)鐘上的BUFG:【Put JTAG Clock on a Global Clock Buffer】復(fù)選框不選中。

圖9-31 【Edit Preferences】界面

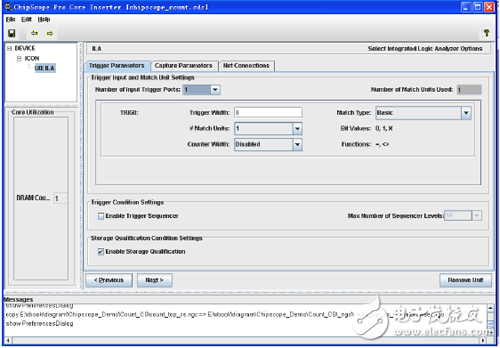

(3) 在圖9-30中單擊【New ILA Unit】,彈出ILA觸發(fā)選項(xiàng)和參數(shù)設(shè)置界面,如圖9-32所示。

圖9-32 ILA觸發(fā)選項(xiàng)和參數(shù)設(shè)置界面

Trigger Parameters選項(xiàng)卡:

Trigger Input and Match Unit Settings選項(xiàng)組:

【Number of Input Trigger Ports】下拉列表框:選擇ILA核輸入觸發(fā)端口數(shù)目,ILA核最多支持16個(gè)輸入觸發(fā)端口。每個(gè)觸發(fā)端口的參數(shù)在下方列出,包括觸發(fā)寬度、觸發(fā)匹配條件判斷類型和數(shù)目。

TRIGn選項(xiàng)組:

【Trigger Width】編輯框:觸發(fā)端口由一條或者多條信號(hào)線組成,信號(hào)線的總數(shù)成為觸發(fā)寬度,最大為256。

【# Match Unit】下拉列表框:觸發(fā)比較匹配單元是個(gè)比較器,和觸發(fā)端口相連,用于檢測(cè)觸發(fā)端口是否滿足設(shè)定的條件。每個(gè)觸發(fā)端口可以有1~16個(gè)觸發(fā)匹配單元。觸發(fā)匹配設(shè)置單元設(shè)置的越多,觸發(fā)事件就越靈活,但是要占用更多的內(nèi)部資源。在滿足條件的情況下,盡量減少觸發(fā)匹配單元的數(shù)量。

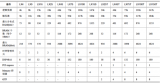

【MatchType】下拉列表框:請(qǐng)參見表9-1。

【Count Width】下拉列表框:匹配單元計(jì)數(shù)器寬度,用于選擇滿足匹配條件的次數(shù),最大32位。

Trigger Condition Settings選項(xiàng)組

【Enable trigger condition sequencer】復(fù)選框:設(shè)臵是否使能觸發(fā)隊(duì)列器和隊(duì)列器深度。觸發(fā)序列是為了增加觸發(fā)的復(fù)雜性,使觸發(fā)的條件更加特殊,我們可以把若干個(gè)狀態(tài)組合起來形成觸發(fā)條件,這樣就能更好的使用有限的資源存儲(chǔ)有用的數(shù)據(jù)。

【Max Number of Sequencer levels】下拉列表框:設(shè)臵最大的觸發(fā)條件序列級(jí)數(shù)。

Storage qualification condition Settings選項(xiàng)組

【Enable Storage Qualification】復(fù)選框:存儲(chǔ)器限制條件。請(qǐng)參考9.2.2小節(jié)中的相關(guān)內(nèi)容。

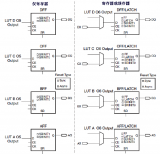

Captures Parameters選項(xiàng)卡:采樣參數(shù)選項(xiàng)卡(參見圖9-33)。

圖9-33 【Captures Parameters】參數(shù)設(shè)置界面

【Sample On】下拉選擇框:設(shè)臵在時(shí)鐘的上升沿或者下降沿采集數(shù)據(jù)。

【Data Depth】下拉選擇框:設(shè)臵ILA核存儲(chǔ)的最大數(shù)據(jù)采樣個(gè)數(shù)。

【Data Same as Trigger】復(fù)選框:設(shè)臵ILA觸發(fā)端口和數(shù)據(jù)采集端口是否相同。請(qǐng)參考9.2.2小節(jié)中的相關(guān)內(nèi)容。

Trigger Port Used As Data選項(xiàng)組:

如果選中了【Data Same As Trigger】復(fù)選框,那么在數(shù)據(jù)選項(xiàng)的每個(gè)TRIGn端口前都會(huì)出現(xiàn)一個(gè)【Include TRIGn Port】復(fù)選框,選中該選項(xiàng),表明數(shù)據(jù)和觸發(fā)端口合并。

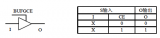

Net connections選項(xiàng)卡(參見圖9-34)。

圖9-34 【Net connections】網(wǎng)絡(luò)連接界面

Net Connections選項(xiàng)組:用于將集成邏輯分析儀ILA核的輸入信號(hào)與設(shè)計(jì)中的網(wǎng)線連接起來。如果觸發(fā)和數(shù)據(jù)信號(hào)分離,那么必須指定數(shù)據(jù)、時(shí)鐘和觸發(fā)端口。雙擊【CLOCK PORT】或者單擊【CLOCK PORT】左邊的加號(hào)(+)。如果還沒連接,該選項(xiàng)顯示為紅色。如圖9-34所示,包括【CLOCK PORT】和【TRIGGER PORTS】?jī)山M端口的連接。

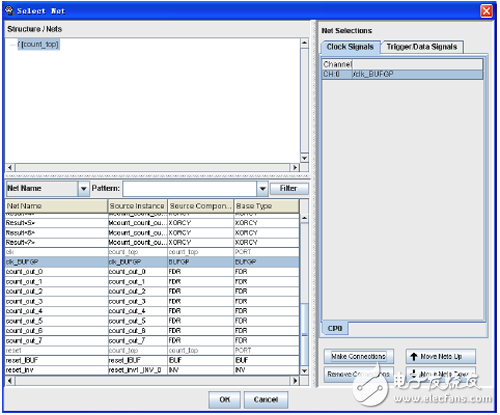

【Modify Connections】按鈕:?jiǎn)螕粼摪粹o彈出【Select Net】對(duì)話框,對(duì)話框很容易地將ILA核工作時(shí)鐘、觸發(fā)信號(hào)、數(shù)據(jù)信號(hào)與設(shè)計(jì)中的網(wǎng)線連接起來,如圖9-35所示。

【Structure/Nets】窗格:列出設(shè)計(jì)的層次結(jié)構(gòu)。

【Net Name】:EDIF網(wǎng)表中的網(wǎng)絡(luò)名,由于重命名或者綜合中的優(yōu)化原因,可能和HDL中的源碼名字不一樣。

【Source Instance】:當(dāng)前綜合結(jié)果中較低層次的元件例化名稱。

【Source Component】:【Source Instance】選項(xiàng)中描述的組件。

【Base Type】:最底層的組件類型,基本類型為原語(primitive)或黑盒子。

【Pattern】編輯框和【Filter】按鈕:通過這兩個(gè)選項(xiàng),可以有選擇地顯示設(shè)計(jì)中可用于ChipScope的網(wǎng)線。

【Remove Connections】按鈕:刪除當(dāng)前的連接。

【Move Nets Up】按鈕:向上移動(dòng)連接的位臵。

【Move Nets Down】按鈕:向下移動(dòng)連接的位臵。

【Make Connections】按鈕:連接所選擇的網(wǎng)絡(luò)節(jié)點(diǎn)和ChipScope內(nèi)核。

圖9-35 【Select Net】界面

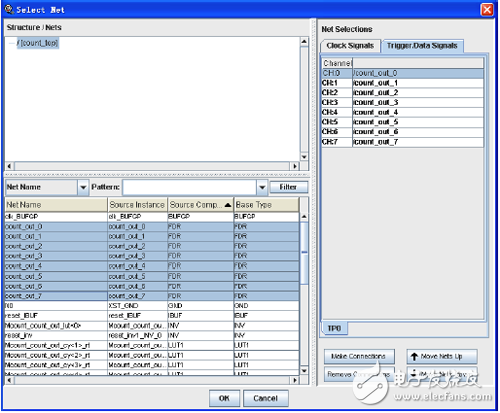

在【Structure/Nets】中,選擇想要連接到ChipScope核的網(wǎng)絡(luò)節(jié)點(diǎn)(可以配合Shift/Ctrl鍵,選擇多個(gè)網(wǎng)線)。在【Net Selections】中選擇【Clock Signals】、【Trigger Signals】或【Data Signals】選項(xiàng)卡,選擇想用于連接網(wǎng)絡(luò)節(jié)點(diǎn)的通道,例如CH0,單擊【Make Connections】按鈕建立網(wǎng)絡(luò)節(jié)點(diǎn)與ChipScope內(nèi)核的連接,如圖9-36所示。

圖9-36 【Select Net】界面

ChipScope Pro只能分析FPGA內(nèi)部邏輯信號(hào),不能直接連接到FPGA的輸入,所以輸入信號(hào)全部以灰色顯示,如圖9-35所示的clk、reset信號(hào)。如果要觀察輸入信號(hào),可連接此輸入信號(hào)的輸入緩沖器的輸出來實(shí)現(xiàn),時(shí)鐘信號(hào)選擇相應(yīng)的BUFGP,如圖9-36所示的clk_BUFGP信號(hào),普通信號(hào)選擇相應(yīng)的IBUF。

連接完成后,單擊“OK”按鈕返回連接顯示界面,發(fā)現(xiàn)所有提示字符“UNIT”、【CLOCK PORT】以及【TRIGGER PORTS】沒有紅色,則單擊【Return Project Navigator】,退出Chipscope,返回到ISE 中。

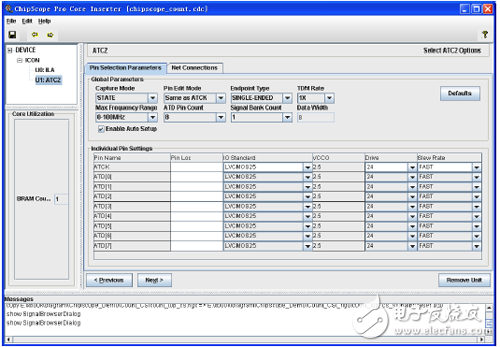

(4) 在圖9-30中單擊【New ATC2 Unit】,彈出ATC2的選項(xiàng)和參數(shù)設(shè)置界面,如圖9-37所示。

圖9-37 ATC2【Pin Selection Parameters】參數(shù)設(shè)置界面

Pin Selection Parameters選項(xiàng)卡。

【Capture Mode】下拉選擇框:可以設(shè)臵成STATE模式和Timing模式,STATE模式用于和CLK輸入信號(hào)同步的數(shù)據(jù)捕獲。數(shù)據(jù)信號(hào)經(jīng)ATC核輸出到FPGA引腳上的通道由流水線觸發(fā)器和CLK組成。Timing模式用于異步數(shù)據(jù)捕獲。數(shù)據(jù)信號(hào)經(jīng)ATC核輸出到FPGA引腳上的通道由組合邏輯組成。

【Max Frequency Range】下拉列表框:ATC2核的最大頻率范圍。有效的最大頻率選項(xiàng)為0~100 MHz、101~200 MHz、201~300 MHz和301~500 MHz。當(dāng)【Capture Mode】設(shè)臵成【State】,【Max Frequency Range】的選擇對(duì)ATC2核實(shí)現(xiàn)有效。

【Pin Edit Mode】下拉列表框:引腳編輯模式,用于設(shè)臵引腳是否為一組,如果設(shè)臵成【Same as ATCK】一組,那么所有ATD的IO標(biāo)準(zhǔn)、驅(qū)動(dòng)、Slew斜率都和ATCK相同。設(shè)臵成【Individual】,則要設(shè)臵每個(gè)引腳的屬性。

【ATD Pin Count】下拉列表框:ATD輸出引腳數(shù),范圍為4~128。

【Endpoint Type】下拉列表框:ATCK和ATD輸出驅(qū)動(dòng)類型為單端或者差分。

【Signal Bank Count】下拉列表框:ATC2核內(nèi)部包含了一個(gè)實(shí)時(shí)可切換的多路數(shù)據(jù)信號(hào)組選通器,【Signal Bank Count】代表了多路信號(hào)選通器的輸入信號(hào)組數(shù)量。有效的信號(hào)組為1、2、4、8、16、32或64。

【TDM Rate】下拉列表框:ATC2核不用片上存儲(chǔ)器資源來存儲(chǔ)捕獲的數(shù)據(jù),Agilent邏輯分析儀通過一個(gè)專用探頭和FPGA引腳連接傳送捕獲的數(shù)據(jù)。ATC2內(nèi)核數(shù)據(jù)傳送到FPGA引腳上的速率可以和ATC2輸入端口DATA的速率相同或者是2倍速率。只有當(dāng)目標(biāo)數(shù)據(jù)捕獲方式設(shè)臵成【State】時(shí),TDM速率才可以設(shè)臵成2倍。

【Data Width】:ATC2核的每個(gè)輸入信號(hào)組數(shù)據(jù)寬度與捕獲模式及TDM速率相關(guān)。在【State】模式,每個(gè)信號(hào)組數(shù)據(jù)端口的寬度等于【ATD Pin Count】ATD引腳數(shù)和【TDM Rate】TDM速率的乘積。在【Timing】模式下,每個(gè)信號(hào)組數(shù)據(jù)端口的寬度等于(【ATD Pin Count】ATD引腳數(shù)+1)和【TDM Rate】TDM速率的乘積。

【Enable Auto Setup】復(fù)選框:使能Agilent邏輯分析儀自動(dòng)設(shè)臵ATC2核引腳和邏輯分析儀POD的連接。這個(gè)屬性使得Agilent邏輯分析儀能自動(dòng)設(shè)定每個(gè)ATC2引腳的相位和采樣電壓偏移。缺省狀態(tài)為使能。

Individual Pin Settings選項(xiàng)組。

【Pin Name】引腳名。

【Pin Loc】編輯框:設(shè)臵引腳的位臵。

【IO Standard】下拉列表框:設(shè)臵ATCK或每個(gè)ATD引腳的I/O標(biāo)準(zhǔn),標(biāo)準(zhǔn)根據(jù)器件和驅(qū)動(dòng)器終端類型而定。

【VCCO】:選擇【IO Standard】后,VCCO會(huì)自動(dòng)顯示該標(biāo)準(zhǔn)對(duì)應(yīng)的輸出電壓。

【Drive】下拉列表框: 設(shè)臵引腳輸出驅(qū)動(dòng)器的最大輸出驅(qū)動(dòng)電流,2~24mA。

【SKEW Rate】下拉列表框:設(shè)臵ATCK和ATD引腳的信號(hào)邊沿斜率為FAST或SLOW。

Net connections選項(xiàng)卡:ATC2核網(wǎng)絡(luò)連接,操作和ILA的網(wǎng)絡(luò)連接部分一樣。

Net Connections選項(xiàng)組:用于將ATC2核的輸入信號(hào)與設(shè)計(jì)中的網(wǎng)線連接起來。

【Modify Connections】按鈕:?jiǎn)螕粼摪粹o彈出【Select Net】對(duì)話框,對(duì)話框很容易地將ILA核工作時(shí)鐘、觸發(fā)信號(hào)、數(shù)據(jù)信號(hào)與設(shè)計(jì)中的網(wǎng)線連接起來。

4. 單擊【Return Project Navigator】,退出內(nèi)核插入器的配置,返回ISE中。

5. 在ISE的【Process】中雙擊【Implement】和【Generate Programming File】,可以生成比特流,并將剛才插入的各類核包含在比特文件中。如果只對(duì)ChipScope內(nèi)核插入器修改,不需要重新【Sythesize】綜合。

6. 打開ChipScope Analyzer,對(duì)采樣數(shù)據(jù)進(jìn)行分析。ChipScope Analyzer在后面小節(jié)中介紹。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論