1.Virtex6 GTX Transceiver簡介 在Xilinx的Virtex6 FPGA中,GTX作為一種低功耗的吉比特收發器,配置靈活,功能強大,并與FPGA內部的其他邏輯資源緊密聯系,可用于實現多種高速接口(如XAUI、PCIE等)。V6 系列的FPGA中,GTX工作帶寬范圍是600 Mb/s到6.6 Gb/s,支持收發雙向,且收發雙向獨立。GTX接收和發送方向均由PMA和PCS兩部分組成,PCS提供豐富的物理編碼層特性,如8b/10b編碼、時鐘校準等功能;PMA部分為模擬電路,提供高性能的串行接口特性,如預加重、均衡等功能。GTX同時還提供動態重配置接口,用于動態的修改GTX的配置。

2.GTX時鐘與布局在Virtix6 FPGA中,GTX是以Quad為單位組織的,每個Quad包含4個GTX和2對差分時鐘輸入。當整個芯片多個GTX被使用時,需要合理的分布GTX與時鐘輸入。從一個Quad輸入的時鐘往上只能給相鄰的一個Quad提供參考時鐘,往下也只能給相鄰的一個Quad提供參考時鐘輸入,最多只能驅動三個Quad,當整個芯片多個GTX使用到同樣的參考時鐘輸入時,合理的分布時鐘輸入可以節省需要的時鐘數量,也可以為時鐘的提供冗余設計。

因此,基本的原則是同一個物理接口的幾個GTX放在一起,由同一個參考時鐘作為時鐘輸入;不同物理接口的GTX如果在同一個參考時鐘的驅動覆蓋范圍內,可以采用同一個參考時鐘輸入。有條件的情況下,可以做時鐘備份;當一個時鐘可以覆蓋更多個GTX的時候,考慮到時鐘驅動能力的不確定性,為留有更多余量,沒必要使用到極限(一個時鐘驅動12個GTX)。另外在V5的GTP中,關于多個GTP共用同一個參考時鐘輸入,要求在這個輸入時鐘的時鐘鏈上,每一個GTP都被使用(即使不需要,也要例化),不允許共用同一個參考時鐘的兩個GTP中間有一個沒有使用的GTP。

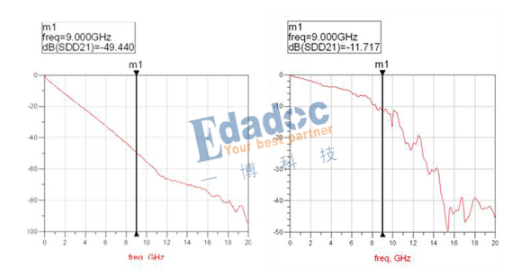

3.預加重和均衡當GTX收發器出現信號質量不佳、數據丟包、傳輸誤碼等的情形時,為提高信號質量,可以調整GTX的預加重、均衡、輸出振幅的值,以及調整采樣點的位置,來優化GTX通道的通信質量。在高速串行接口上,高頻分量衰減比低頻分量更嚴重,導致信號失真。因此,在數據發送方向可以調整預加重值和輸出振幅來提高信號質量。預加重用于增加信號中高頻分量的強度,預加重的值由參數TXPREEMPHASIS[3:0]來設定。調整振幅用于增加信號的整體強度,振幅強度由參數TXDIFFCTRL[3:0]來設定。在數據接收方向可以調整均衡的值,還可以調整采樣點在采樣窗中的位置。均衡用于補償接收信號中的高頻分量,使接收到的信號恢復原狀,均衡值由參數RXEQMIX[2:0]。采樣點設置可以選擇采樣窗的眼中,使采樣更穩定。以上參數的取值以及各個值的意義,請參見《Virtex-6 FPGA GTX Transceivers User Guide》(UG336)。

4.GTX的調試手段Virtex6 GTX提供了四種不同的環回,分別是近端PCS環回、近端PMA環回、遠端PCS環回、遠端PMA環回,可用于定位問題出現在GTX的哪個部分。同時,通過觀察GTX輸出的PLL時鐘鎖定信號,可以分析問題是否和時鐘相關。Xilinx提供了一系列的GTX Transceiver調試手段和工具,最有用的就是使用Chipscope進行IBERT比特流誤碼率測試(即PRBS,偽隨機二進制序列誤碼率測試)。關于IBERT(PRBS)測試的詳細內容,將另有博文來介紹。

Virtex6 GTX設計總結:預加重、均衡、輸出振幅的值

- FPGA(591969)

- Xilinx(119164)

相關推薦

8個GTX TX通道的Virtex-6 VC6VLX240TFF1156-3失敗

我有一個帶有8個GTX TX通道的Virtex-6 VC6VLX240TFF1156-3項目。我正在使用EDK 13.3。根據coregen示例HDL,每個GTX TX通道都有一個相關的用戶時鐘

2018-10-23 10:30:06

GTX可以生成和接收LVDS信號嗎?

親愛的Xilinx人,我有一些簡單的問題要問。我正在使用Virtex 6 SX475T進行PCB設計。我正在考慮添加一個擴展端口,它有2對CML和6對LVDS信號。從用戶指南,我認為一個GTX銀行

2020-06-13 08:38:27

Virtex-6有專用的clkout(PLL輸出)引腳嗎?

你好。如今,我設計了使用Virtex-6的主板。我想知道Virtex-6是否有專用的PLL輸出引腳(clkout引腳)。我檢查了Virtex-6系列概述Virtex-6 FPGA時鐘資源用戶指南

2020-06-12 10:05:21

Virtex-6電源去耦的疑問如何解答

你好,在閱讀Virtex-6 PCB設計UG(ug373)和http://forums.xilinx.com/t5/Virtex

2020-06-15 16:27:01

Virtex6內部錯誤的解決辦法?

你好;我將FPGA代碼從Virtext 5(240t)遷移到virtex6(xc6vsx475t-2ff1156)。我在合成期間收到錯誤消息: 目標設備:xc6

2020-06-03 16:42:14

Virtex6后備故障如何解決

我正在運行一個使用Master SPI配置的virtex6。我的黃金圖像位于地址0x000000處,它指向0x100000以供下一個要加載的圖像。當地址0x100000具有良好的圖像時,它會正確加載

2020-06-15 12:34:36

Virtex6怎么配置寄存器初始值

你好我想配置寄存器初始值。有任何約束(UCF)可以實現嗎?環境 -Virtex6 -ISE 14.7以上來自于谷歌翻譯以下為原文Hello I want to configure

2018-10-26 15:03:36

Virtex 6 GTX耗盡資源的解決辦法?

您好,我正在使用Plan Ahead 14.7和Virtex6 xc6vlx240tff1759-2目標FPGA。我的設備中有一個PCIe內核,它使用了FPGA中可用的24個GTX通道。我有5個通信

2020-06-17 07:46:51

Virtex 6 FPGA的目標阻抗值是什么?

嗨,我目前正在使用75K Virtex-6 FPGA(XC6VLX75T_FFG484)。如果我們看一下Virtex-6 FPGA PCB設計指南(ug373-ver 1.3.1)中的“PCB去耦

2020-06-18 15:30:22

Virtex 6 MMCM輸入時鐘源問題怎么解決

嗨,我使用Virtex6 LX75T和4個高速DAC設計了一塊電路板。我將每個DAC連接到一個FPGA io Bank,我使用MRCC引腳作為MMCM(差分)的時鐘輸入,4個引腳用于片外反饋。不幸

2020-06-16 10:06:19

Virtex 6 如何使用PCIe端口連接定制板

嗨,我正在嘗試將子板連接到Virtex6 ML605評估板的PCI-e端口。我想使用相關的pinas通用IO引腳。我在MAP中遇到錯誤(包:1107錯誤)。涉及的符號:BUF符號“b19_IBUF

2020-06-02 16:41:45

virtex-6 FPGA的存儲條件是什么

你好我搜索了virtex-6的數據表,但我找不到有關virtex-6XC6VLX240T-1FFG1156C FPGA的存儲信息,我想保留一段時間,FPGA的最大值是多少?或者我在哪里可以找到相關信息?謝謝希望你的回答

2020-06-17 13:39:05

virtex6中使用SRIO時遇到了一些問題怎么解決

大家好,我在virtex6中使用SRIO時遇到了一些問題。所以我試著用ibert來測試他的問題所在。但測試也失敗了。我不知道出了什么問題.Plase幫幫我!非常感謝你。

2020-06-19 10:15:08

virtex6配置電路設計問題求助

我使用的是virtex6下的HX38OT-1155,并沒有使用官方推薦的system ACE配置方式,只采用JTAG配置模式。配置bank0設計原理圖和附件,第一次設計硬件,有的地方可能有問題,還希望發現問題的諸位不惜賜教。謝謝!

2014-09-02 15:12:04

預加重是什么意思

預加重是什么意思理論證明鑒頻器的輸出噪聲功率譜按頻率的平方規律增加。但是,許多實際的消息信號,例如語言、音樂等,它們的功率譜隨頻率的增加而減小,其大部分能量集中在低頻范圍內。這就造成消息信號高頻端

2010-03-30 12:13:52

ISE12.3 PAR不完全但LUT使用率僅為38%(Virtex6器件)

嗨,我使用ISE12.3(Virtex6設備)并在我們的設計上多次嘗試,所有PAR結果都是不完全路由的信號。我發現時間限制不符合保持時間問題(差異-0.018ns)。如何檢查此問題以及綜合,PAR或

2018-10-09 15:38:50

JESD204B 串行鏈路的均衡器優化

去加重均衡技術來準備供傳輸的 7.4 Gbps 串行數據。通過配置,用戶可以優化輸出驅動器的去加重設置 (DEM) 和輸出電壓擺幅設置 (VOD),以便反向匹配信道特征。實驗表明可通過 20 英寸

2015-05-11 10:40:44

LT8631UX HDMI2.0 / 1.4自適應均衡RX輸入和預加重TX輸出

1.說明Lontium LT8631UX HDMI2.0 / 1.4開關具有符合HDMI2.0 / 1.4規格的3:1開關,最大6Gbps高速數據速率,自適應均衡RX輸入和預加重TX輸出,以支持長

2022-03-03 14:41:11

LVDS發送器IP可用于Virtex6和Virtex7 FPGA嗎

嗨,LVDS發送器IP(基于OpenLDI,像素和控制數據轉換為LVDS信號)可用于Virtex6和Virtex7 FPGA嗎?謝謝克里希納

2020-06-17 14:52:28

SFP銅纜預加重驅動器MAX3982相關資料下載

SFP銅纜預加重驅動器MAX3982資料下載內容主要介紹了:MAX3982引腳功能MAX3982功能和特性MAX3982應用范圍MAX3982內部方框圖MAX3982極限參數MAX3982典型應用電路

2021-04-01 07:05:05

USB3.0信號延長增益

最近在做一個USB3.0的延長方案,一直都只能做到3M長度,始終無法突破,調節各種增益都不行。3.0調節參數無非就是均衡器EQ、預加重(Pre_emphasis)、去加重(De_emphasis

2017-04-11 16:52:03

Unrecognized technology: ”VIRTEX6“

我用synplify去綜合,出現了錯誤,error:Unrecognized technology: ”VIRTEX6“error:Device Part not found:"XC6VSX315T"

2013-11-09 17:11:45

Xilinx Virtex-6系列選型

Xilinx Virtex-6系列選型1 Xilinx公司Virtex-6 FPGA共有3個系列:Virtex-6 LXT – 高邏輯密度,高速串行收發器,高密度IOVirtex-6 HXT – 高

2012-02-28 14:56:59

srio_v5_6 IP核使用發生錯誤

'srio_icon_gen.i_srio_icon'。引腳名稱拼寫錯誤可能導致此問題,缺少edif或ngc文件,塊名稱與edif或ngc文件名之間的大小寫不匹配,或者類型名稱的拼寫錯誤。目標'virtex6'不支持符號'srio_icon

2018-10-08 11:10:47

【緊急求助】Xilinx Virtex6 FPGA與PC端千兆網口通信問題

這段時間在調試FPGA與PC的千兆網口通信,用到Virtex6 Tri Mode Ethernet IP Core,遇到諸多問題,例如: 1、我用的是xilinx的virtex6中

2013-12-25 16:40:16

使用Virtex-6 FPGA GTX收發器向導出現錯誤的解決辦法?

嗨,我正在使用Virtex-6 FPGA GTX收發器向導,版本1.12。我使用Web包許可證進行模擬。device = xc6vlx75tdevicefamily = virtex6

2020-06-17 13:58:20

使用Virtex 6和14.4映射錯誤

我的目標是使用EDK 14.4進行Virtex 6的設計。我收到了自動插入GTX收發器的錯誤,因此我按照http://www.xilinx.com/support/answers

2018-10-19 14:33:57

使用gtx沒有輸出

使用GTX核輸出一個序列,仿真結果和我想要的結果一致。

如圖所示輸出結果為一個不到1M的方波。不到1M是防止示波器速率不夠。

我的板子有4個GTX,兩個在PCIE上,兩個在網口上。我把把串行輸出

2023-10-12 15:16:22

關于virtex6的XILINX Platform Cable USB 問題

本帖最后由 mr.pengyongche 于 2013-4-30 03:08 編輯

請問各位前輩,我手里有一個XILINX Platform Cable USB 的下載器,能夠下載virtex4程序我現在需要下載virtex6 的程序,這個下載器支持virtex6

2012-07-09 09:58:17

具有接收均衡器的1Gbps至10Gbps預加重驅動器MAX3984相關資料下載

的24 AWG電纜* 驅動30in的FR-4* 可選1000mVP-P或1200mVP-P差分輸出擺幅* 可選輸出預加重* 可選輸入均衡* LOS檢測內建噪聲抑制* 傳輸關閉* 可熱插拔三

2021-05-17 06:16:25

利用IBERT核對GTX收發器板級測試

8b10b編碼、時鐘校準等功能,PMA部分為模擬電路,提供高性能的串行接口特性,如預加重、均衡等功能。GTX同時還提供動態配置接口,用于動態的修改GTX的配置。

IBERT 工具的環回模式有近端PCS環回

2023-06-21 11:23:12

哪里可以找到有關Virtex-6GTX CDR PLL鎖定時間的信息?

eHi親愛的社區希望你們中的一些人還在身邊。有誰知道我在哪里可以找到有關Virtex-6GTX CDR PLL鎖定時間的信息?我試圖在一段時間內使用GTX暫停模式,這樣它只在需要時突發數據包。因此

2019-11-06 06:23:58

在Virtex-5/6 GTP / GTX收發器中如何實現JTAG

你好,關于GTP / GTX收發器的JTAG實現,我有幾個問題。1. JTAG是否針對GTP / GTX收發器實現(因此可以驅動和讀取引腳以進行電路板驗證)2. JTAG組件放在GTP磁貼中的哪個

2020-06-18 14:41:02

在原始GTX E1中應該為Virtex 6 GTX PLL TX_TDCC_CFG使用什么值

我手動配置GTX(GTXE1)的PLL以使用100MHz至125MHz范圍內的輸入時鐘。我已經從文檔(ug366)中找到了合法的價值來實現這一目標。但它表示TX_TDCC_CFG的正確值由

2020-07-13 12:46:08

在同一FPGA上運行的兩個不同系統是否具有相同的FIT值?

Xilinx器件可靠性報告”時,我看到所有FPGA的FIT值都歸類于工藝技術中,而Virtex6的FIT值明顯低于Spartan6(約為34%)。我好幾天都在搜索這個話題,但我找不到確切的答案。為什么FIT率被

2020-03-12 11:16:18

基于Virtex-5 LXT的串行背板接口設計

速率高達數千兆比特的遠距離(通常可達40英寸或更遠)信號傳輸。這兩種均衡方法都是通過增強高頻信號分量和衰減低頻信號分量,來最大限度地降低符號間干擾(ISI)的影響。區別在于,預加重是對線路驅動器輸出

2019-04-16 07:00:07

如何使用Virtex6 LX760和ISE13.4

你好,我使用Virtex6 LX760和ISE13.4是否有可能在PAR之后混淆BRAM(類似于將所需的BRAM內容合并到已生成的位文件中)。或者我必須在合成之前做到這一點?提前致謝!

2020-06-16 07:09:04

如何使用相鄰GTX磁貼的外部時鐘

你好,我在兩個通過串行背板連接的Virtex 6 FPGA中實現了一個簡單的4通道Aurora 8b / 10b內核。每個磁貼的專用GTX時鐘是固定的 - 在FPGA0上為312.5Mhz,在

2020-06-18 10:21:39

如何尋找Virtex6和7Series部件的類似亞穩態參數測量

/Metastable-Delay-in-Virtex-FPGAs/ba-p/7996有Virtex4和Virtex5的測量。我正在尋找Virtex6和7Series部件的類似亞穩態參數測量。是否存在應用說明?我猜猜V6& 7應該比

2020-07-18 16:58:50

如何將Aurora與Virtex-6 LX240t配合使用

嗨,我正在嘗試將Aurora與Virtex-6 LX240t配合使用。示例設計是由核心生成器(11.5和12.1)生成的測試代碼。當我使用環回模式(近端PCS和PMA)進行測試時,兩者都能正常工作

2020-06-02 13:14:40

如何將FX3的Tx去加重設置值設置為 “0”?

,請告訴我怎么做。

例如,是否可以將 Tx 去加重 (dB) 的值設置為 0x00,用于上述社區中描述的 Tx 去加重?

Tx 去加重 (dB) = 20 *log10 [(128 ? 2 * tx_去加重值) /128]

2024-02-23 06:05:44

如何將Vitesse交叉點連接到Virtex 6 GTX輸入

你好,如何將Vitesse交叉點(VSC3308)連接到Virtex6 GTX輸入?交叉點數據輸出電壓擺幅可在400-1100mVpp之間調節,而共模電壓為2V。我不能使用隔直電容。有解決方案的人?

2020-06-18 14:53:12

如何建立Spartan 6和Virtex 6之間的通信?

親愛的專家 我嘗試通過GTP(S6)/ GTX(V6)在SP605(Spartan6)和ML605(Virtex6)之間建立通信, 我想連接兩個主板的SFPlight模塊,并且定義極光協議,但我

2019-07-31 10:37:43

如何通過JTAG使用iMPACT SW在virtex4設備上執行回讀

在網上找到了幾個bitgen命令:“-g GLUTMASK_B:0”用于virtex6設備,“ - g write_glutmask_b:yes”用于virtes5設備。這些選項都不

2020-06-19 06:41:40

如何采用Virtex 4的SLC NAND閃存

或SD的SPI接口。我們將推出兼容ONFI的4Gb Micron SLC NAND芯片。似乎Virtex6和Kintex7有一個核心,但它們在AXI總線上。只是想知道是否有人找到了將ONFI閃存

2020-06-17 09:54:32

怎么通過GTX SMA連接器進行FPGA通信?

大家好 我正在嘗試在FPGA V6之間建立通信鏈接。我正在關注“LogiCORE IP Virtex-6FPGA GTX收發器向導v1.9”文檔。在測試示例中使用PCIeconnectors但我想

2020-05-19 07:35:21

改變7系列GTX發射器線路速率的步驟誰有嗎?

您好,我一直在論壇和互聯網上搜索,以及查看UG476,我還沒有找到改變7系列GTX發射器(Kintex 7)線路速率的步驟已配置(不進行部分重新配置)。我找到的唯一指南是Virtex5 GTX

2020-07-27 10:28:44

無法將GTX速率設置為高于6.6 Gbps的值

你好當我將7系列收發器向導用于Kintex-7設備(XC7K70T)時,我無法將GTX速率設置為高于6.6 Gbps的值。 Kintex-7 GTX應該以11.3 Gbps的速度運行,但似乎只適用于

2019-03-06 09:49:16

有沒有應用IC或電路能夠改變GTX的輸出共模電壓?

我使用Virtex-6 GTX生成LVDS信號來測試我的LVDS接收器能力。我使用交流耦合來阻止GTX直流偏置,并使用上拉電阻將交流電容器連接到新的直流偏置,它可以正常工作。但是當我發送一個特殊

2020-06-10 08:47:41

求virtex5與部分重新配置教程?

嗨,我是學生 我嘗試使用virtex5與部分重新配置教程UG702,但本教程設計為virtex6(ML605)所以我需要修復它 為virtex5創建新的綜合和網表(從源代碼復制.v文件并運行合成

2020-06-16 07:28:38

缺少ISE Design Suite的設備

我為我的班級下載了ISE Webpak,我們使用的是Virtex6系列設備。在家庭下有一個完整的設備列表,但現在只剩下一個(XC6BLX75T)。我重新安裝了ISE,甚至為virtex6重新安裝并

2019-04-16 13:45:20

請問Virtex7 GTX如何生成PIPE接口PCIE PHY?

選擇的情況下,生成以下輸入和輸出端口的GTX,其在ug476_7Series_Transceivers(GTX).pdf和pg168-gtwizard.pdf中未提及。我想知道如何正確連接這些信號

2020-05-04 09:05:44

請問virtex 6 FPGA的這種電流是否正常?

大家好,當我測試virtex6 FPGA時,我遇到了一些奇怪的事情。我之前從未為FPGA供電,這是第一次為FPGA供電FPGA的電源電壓如下:VCCINT:1.0VVCCO:2.5VVCCAUX

2020-06-17 13:50:43

請問GTP和GTX兼容嗎?

生成了一個TX唯一的Aurora 8b10b內核(GTP),為Virtex7生成了一個僅限RX的Aurora 8b10b內核(GTX)。我的參考時鐘是125MHz,而我的DRP / INIT時鐘都是

2020-07-31 11:27:52

請問如何使用virtex6連接外部設備?

Aoa ....我想將外部時鐘IC DS1307與我的FPGA板(Virtex ML605)連接。這是我的項目的要求,如果您曾經使用FPGA板連接外部IC /設備,請回復。謝謝

2020-04-29 09:41:33

請問如何將GS3440與GTX端口連接?

我想知道如何將Kintex-7 GTX端口與GS3440(3G / HD / SD自適應電纜均衡器)的差分輸出接口。我可以使用直流DC耦合器還是必須使用AC耦合GTX端口?以下是GS3440數據表中的信息。非常感謝。大衛。

2020-07-26 13:29:55

采用XPS 12.3的Virtex6 ML605上的PCIe該怎么使用?

大家好,在獲得我的ML605 Virtex6(Production Silicon)開發板之后,我嘗試用XPS生成一個系統。我只使用默認設置而不添加或刪除任何核心。遺憾的是,PCIe總線

2019-08-26 10:56:44

高速串行接口互聯小議分享

)和均衡功能(Equalization)。提起這個去加重,如果接觸過Altera帶Transceiver的FPGA的同志應該了解,Altera的這些產品中的GXB均有預加重和均衡的功能。所謂預加重是在

2015-01-22 14:20:51

Virtex-6 FPGA GTX收發 User Guide

Virtex-6 FPGA GTX收發 User Guide:This document shows how to use the GTX transceivers in Virtex

2009-12-31 17:05:28 25

25

25

25ADN8102ACPZ-R7是一款均衡器

ADN8102是一款四通道雙向CX4電纜/背板均衡器,具有八路PECL/CML兼容型差分輸入和八路CML差分輸出;輸入提供可編程均衡,輸出提供可編程輸出電平及預加重或去加重。該器件針對NRZ數據

2023-07-11 11:01:52

MAX3987 8.5Gbps四通道均衡器和預加重驅動器

MAX3987 8.5Gbps四通道均衡器和預加重驅動器

MAX3987是4通道接收和發送均衡器(EQ),用于補償FR4帶狀線/微帶線和/或高速電纜中的傳輸介質損耗。器件可以

2010-01-15 15:35:17 1102

1102

1102

1102MAX4951C 雙通道均衡和預加重

該MAX4951C雙通道均衡和預加重和輸入緩沖區是理想的redrive內部串行ATA(SATA)的1i,2i的信息,和3i信號以及100萬和200萬個eSATA信號

2011-04-08 10:22:13 1594

1594

1594

1594Virtex6 FPGA GTX和Spartan6 FPGA GTP收發器的電源模塊

bstract: This reference design enables a complete solution for powering Xilinx Virtex-6 FPGA GTX

2017-04-05 10:15:57 17

17

17

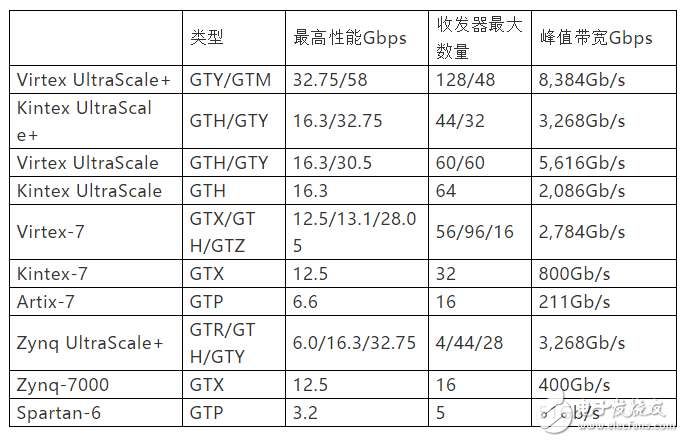

17Xilinx不同FPGA集成的GTx及性能

GTx接收和發送方向均由PCS和PMA兩部分組成,PCS提供豐富的物理編碼層特性,如8b/10b編碼等;PMA部分為模擬電路,提供高性能的串行接口特性,如預加重與均衡。

2018-06-29 08:47:00 10526

10526

10526

10526

比較 Xilinx? Virtex?-7FPGA GTH收發器和Altera Stratix V GX收發器的均衡能力

設計人員呼吁提升10G+ 芯片到芯片和背板性能, 依賴接收機均衡來補償信號失真。觀看視頻, 并排比較 Xilinx? Virtex?-7 FPGA GTH 收發器 和 Altera Stratix V GX 收發器的均衡能力。

2018-05-23 15:47:00 3974

3974

3974

3974

virtex-7 GTX的Chipscope集成誤碼率測試資料說明

用于virtex?-7 FPGA GTX收發器的Chipscope?Pro ibert核心是可定制的,設計用于評估和監控virtex-7 FPGA GTX收發器。該核心包括在FPGA邏輯中實現的模式

2019-02-25 16:43:08 15

15

15

15串行系列:預加重與均衡的優缺點總結

在這對于預加重與均衡的優缺點稍微做一下總結: 1.預加重實現起來比均衡要簡單,功耗低一些。 2.預加重增益不能做太大,一個1.1Vpp的輸出不可能預加重后轉化為5Vpp的輸出。 3.預加重會增加通道

2021-04-13 17:34:03 3923

3923

3923

3923

電子發燒友App

電子發燒友App

評論