有了前面兩個實例的鋪墊,下面這個工程就要帶大家嘗試搭建一個基于MicroBlaze的應用。特權同學也是第一次接插Xilinx的嵌入式開發平臺,跑了一個流程下來,正如所料,和Altera的SOPC Builder(今后主推Qsys)以及EDS相比,單從開發環境上來看是大同小異、換湯不換藥的。????????

如圖1所示,其實在安裝ISE軟件的時候,由于我們選擇了Embedded Edition(可參考手記2),那么在安裝完成的程序菜單中,如圖1所示,EDK(Embedded Development Kit)后有兩個開發平臺,即Xilinx Platform Studio(硬件開發平臺,簡稱XPS)和Xilinx Software Development Kit(軟件開發平臺,簡稱SDK),對應Altera的SOPC Builder(或Qsys)和EDS。由于Xilinx的SDK支持的軟核MicroBlaze片內總線是AXI,而Altera的NIOS II主推的是Avalon,這里先不論孰優孰劣,他們之間多少還是有些區別的,非常習慣于SOPC Buider下工作的特權同學第一次接觸XPS的環境還真有些不適應。而反觀軟件平臺SDK,由于和EDS一樣都是基于Eclipse的架構,所以比較容易上手,甚至連菜單按鈕的布局和使用也多少有些似曾相識的感覺。

?圖1 EDK開發環境相似歸相似,咱們還是老老實實的找個傻瓜

教程扎扎實實的熟悉一下整個開發流程。很自然的,特權同學便開啟DocNav淘淘金,如圖2所示,EDK and SDK下盡都是相關文檔,而經過粗略的瀏覽后,特權同學鎖定了“EDK Concepts, Tools, and

Techniques.pdf”文檔。雖然此文檔也只是很簡單的列舉了一個軟硬件協同開發的實例,很多設計細節都被忽略了(沒讓特權同學少吃苦頭),但是好歹能夠讓人摸著大方向,于是花費不多時間特權同學便成功構建并驗證了屬于自己的第一個

嵌入式工程(包括硬件工程和軟件工程)。

圖2 EDK和SDK相關文檔????????

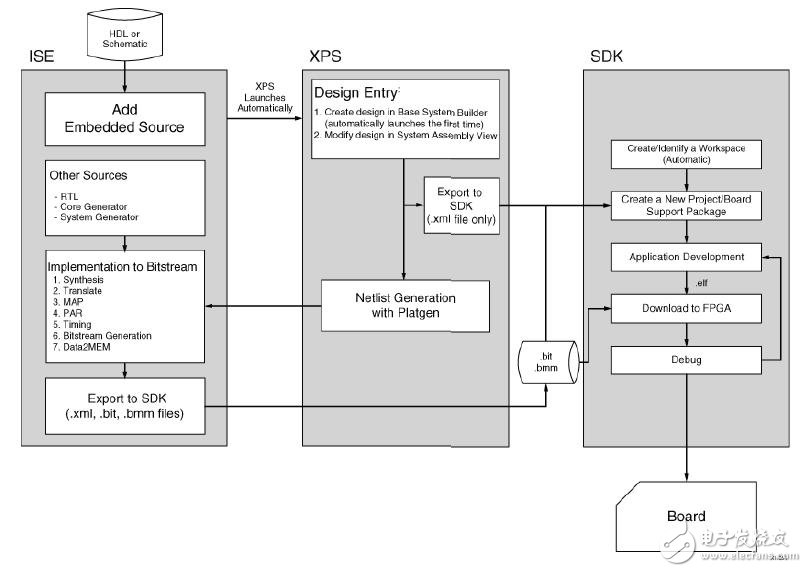

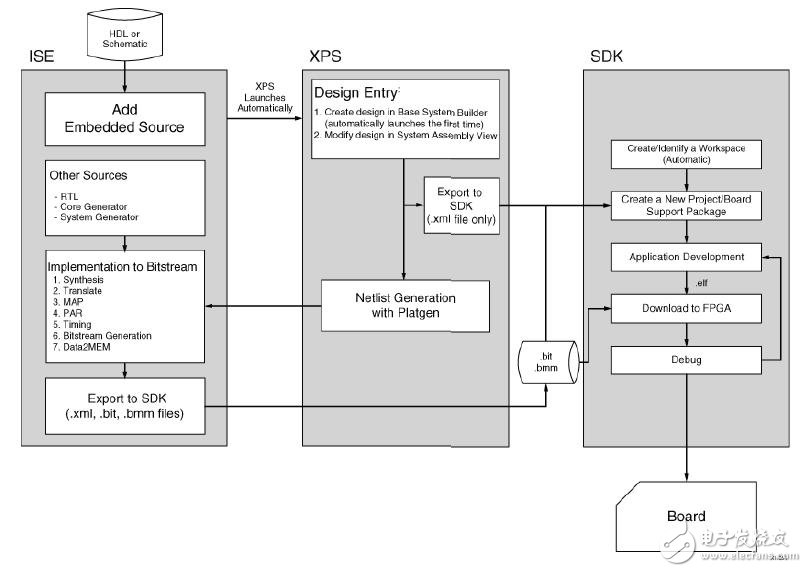

如圖3所示,這里基本示意了整個軟硬件開發的工作流程。從ISE基本設計輸入開始,包括了XPS硬件系統架構的生成,再到SDK的軟件開發,同時在ISE完成綜合、約束、映射等編譯步驟,最終生成可

下載文件進行板級的調試驗證。

圖3 基本嵌入式工作流程????????

就著前面的開發步驟,我們也簡單的跑跑流程好好體驗一番。在上一個已經例化pll工程的基礎上,我們接著使用XPS添加一個帶MicroBlaze軟核的

嵌入式系統。???????? 如圖4所示,新建一個源文件,選擇Embedded Processor,命名為mysoc。

圖4 新建Embedded Processor文件????????

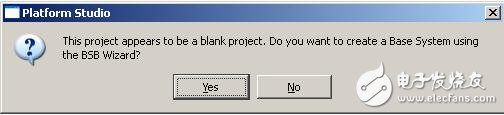

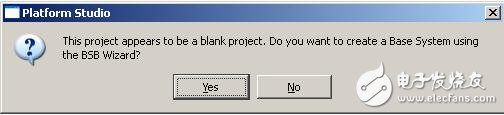

新建的Embedded Processor會自動打開XPS,然后首先彈出一個基本系統向導選擇對話框,如圖5所示。點擊“Yes”。

圖5 基本系統向導選擇????????

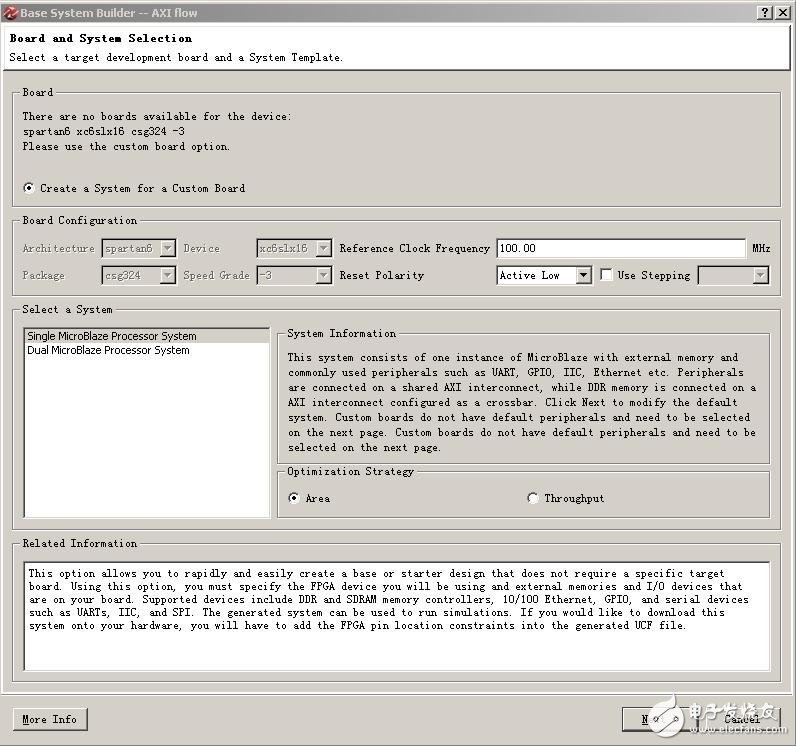

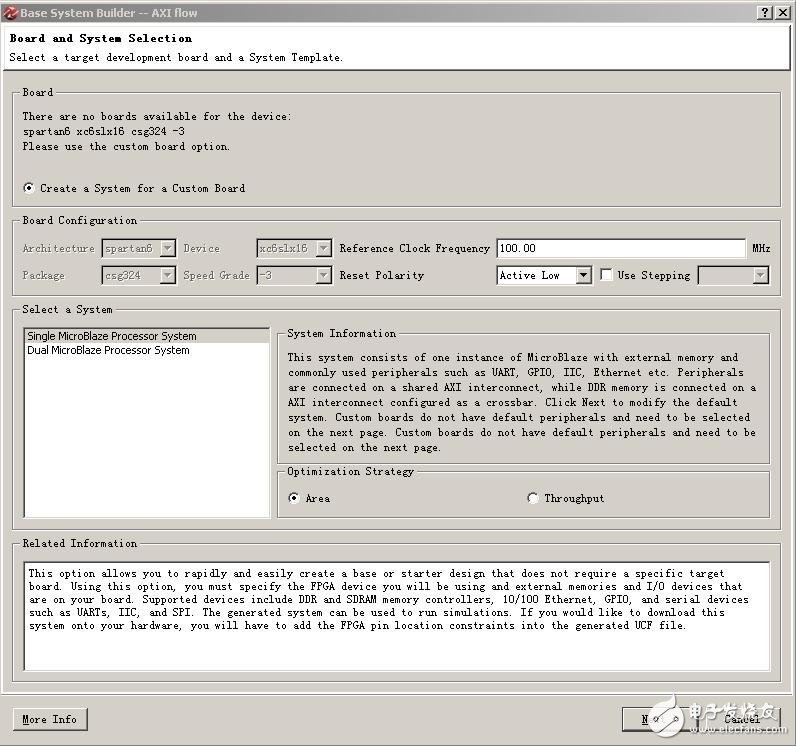

接著出現Base System Builder對話框,默認選擇AXI system后點擊“OK”。接著進入基本系統配置頁面,這里主要由兩個頁面,第1個頁面如圖6所示。這里配置板級的

信息和系統選擇,板級信息如輸入

時鐘頻率,復位

信號有效極性等,系統選擇可以配置為單核或雙核,優化策略可以是面積或吞吐量,該實例默認選擇均符合要求,無需改動,點擊“Next”到配置頁面2。

圖6 基本系統設置頁面1???????? 如圖7所示,在配置頁面2中,選擇Processor Frequency為50MHz,設置Local Memory Size為32KB。接下來需要添加一個8bit的GPIO外設,點擊“Av

ailable Peripherals”下的“

Add Device…”按鈕。

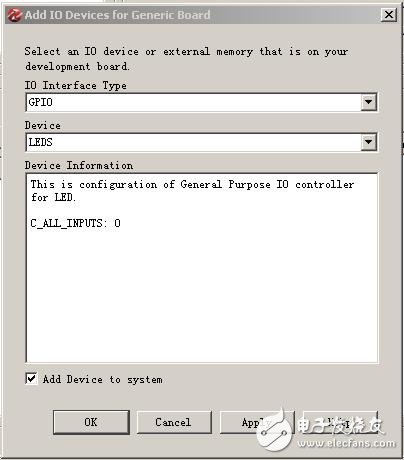

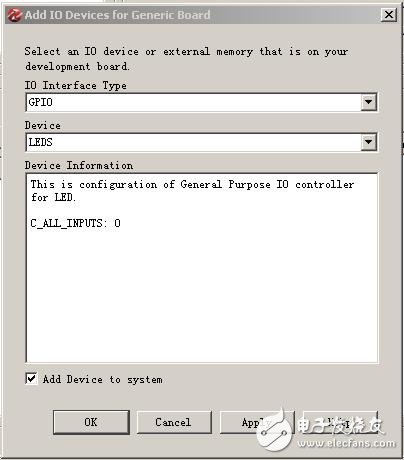

圖7基本系統設置頁面2???????? 彈出“Add IO Devices for Generic Board”窗口如圖8所示,分別設置“IO Interface Type”為“GPIO”、“Device”為“

LEDS”,完成后點擊“OK”。

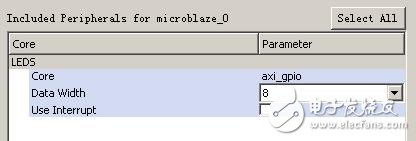

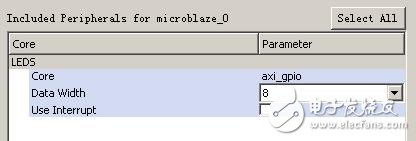

圖8 添加GPIO外設???????? 此時,在“Included Peripherals for microblaze_0”下出現如圖9所示的LEDS外設,默認設置Data Width為8。最后我們點擊Finish完成向導配置。

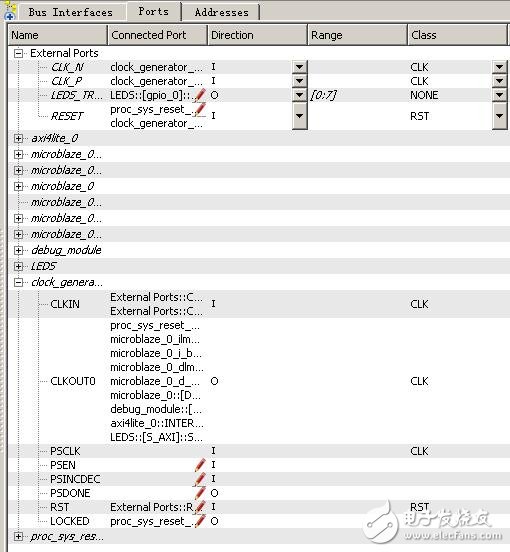

圖9 新添加的LEDS外設???????? 稍等片刻,當新系統生成好之后,如圖10所示,在XPS默認打開的System Assembly View的Bus Interfaces列表中,這個新系統的所有組件都羅列出來了,并且在左側有各個組件間的信號

接口連接關系。從他們之間的相互連接關系很容易便可理解這個簡單系統的架構方式:microblaze_0便是大名鼎鼎的軟核

CPU——MicroBlaze,它連接了AXI總線用于外設擴展,這條總線上掛著的外設包括了我們特意添加的GPIO外設LEDS;此外,microblaze_0的兩個LMR接口分別連著microblaze_0_i_bram_ctrl和microblaze_0_d_bram_ctrl,從命名上不能推斷出著兩個組件應該是CPU的指令(instruction)和數據(data)存儲

控制器,而靠右側的紅色連接部分又分別將他們與microblaze_0_bram_ctrl組件相連接,說明這個microblaze_0_bram_ctrl便是CPU的主存儲控制器。此外,兩個相對獨立的clock_generator_0和proc_sys_reset_0則為系統時鐘和復位產生組件。

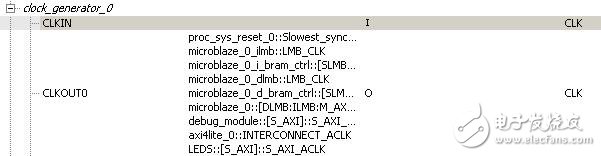

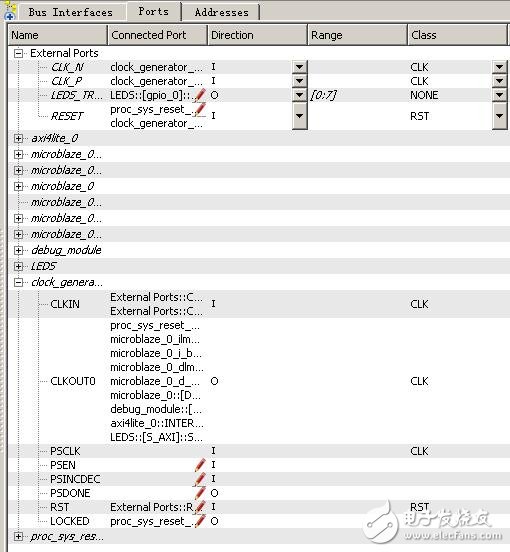

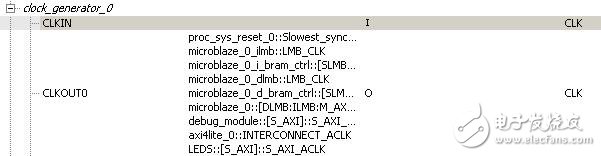

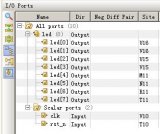

圖10 IP組件列表???????? 接著我們來看看Ports部分,如圖11所示。這里展開External Ports便是該系統所有需要與外部進行直接隱射的管腳。LEDS_TRI_O便是8個連接到板上指示燈的信號,RESET是低電平有效的復位信號,而CLK_N和CLK_P是一對100MHz輸入的差分信號。由于我們的外部輸入100MHz時鐘不是差分的,而是單時鐘接口,因此需要簡單的做些修改。???????? 展開clock_generator_0,在CLKIN一欄右擊選擇“New Connection”,此時如圖12所示,差分時鐘便成了單時鐘接口了。鼠標落在這個單時鐘信號上再次右擊并選擇“Make External”,這個單端時鐘接口便出現在了External Ports中。而之前的差分時鐘接口并未在External Ports中消失,需要依次右擊并選擇“Delete External Ports”便可將其刪除。

圖11 系統外部連接信號

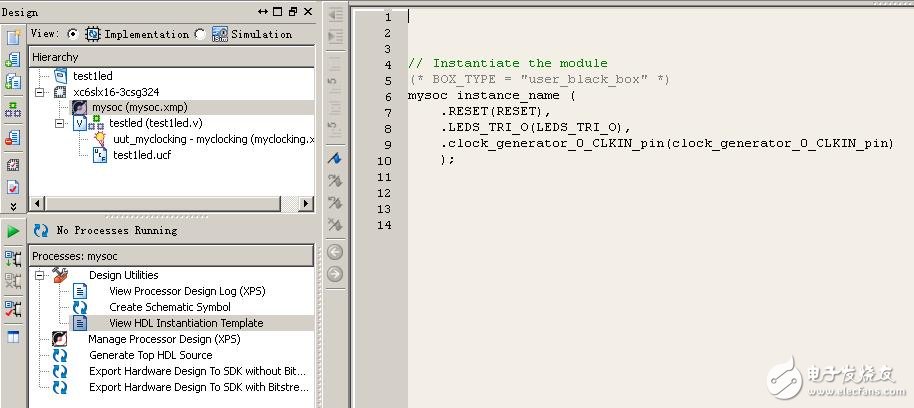

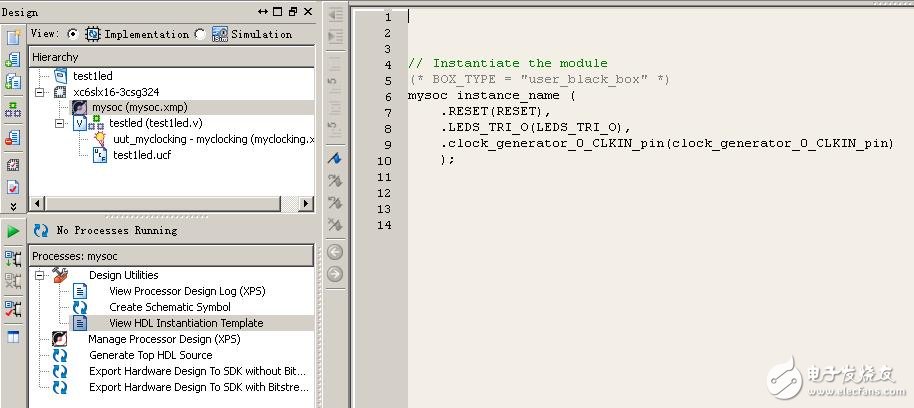

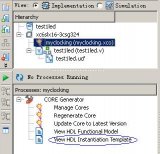

圖12 更改后的CLKIN???????? 修改好之后的External Ports列表如圖13所示。圖13 更改后的External Ports???????? 完成時鐘信號修改,點擊XPS菜單欄HardwareàGenerate Netlist生產這個嵌入式硬件系統的網表。回到ISE中,在Hierarchy下多出了mysoc.xmp文件,選中它。在Processes下展開Design Utilities,雙擊View HDL Instantiation Template生產系統的例化模板文件,如圖14右側所示。

圖14 生成系統例化模板???????? 將此模板復制到ISE頂層源代碼中,相應匹配好接口,原先的8個LED接口將由軟件

編程控制。頂層源代碼修改如下:module testled(??????????? clk,

rst_n,??????????? led??????? );?input clk;????? //100MHzinput rst_n;??? //低電平復位信號?output[7:0] led;??? //連接到

LED指示燈??wire clk_100m;????? //clocking輸出100MHzwire clk_50m;?????? //clocking輸出50MHzwire clk_25m;?????? //clocking輸出25MHzwire clk_12m5;????? //clocking輸出12.5MHzwire clk_locked;??? //clocking輸出完成標志位?//---------------------------------------------------//IP核Clocking Wizard例化//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG?? myclocking uut_myclocking?? (// Clock in ports??? .CLK_IN1(clk),????? // IN??? // Clock out ports??? .CLK_OUT1(clk_100m),???? // OUT??? .CLK_OUT2(clk_50m),???? // OUT??? .CLK_OUT3(clk_25m),???? // OUT??? .CLK_OUT4(clk_12m5),???? // OUT??? // Status and control signals??? .RESET(!rst_n),// IN??? .LOCKED(clk_locked));????? // OUT// INST_TAG_END ------ End INSTANTIATION Template ---------?//---------------------------------------------------// 例化mysoc系統(* BOX_TYPE = "user_bl

ack_box" *)mysoc uut_mysoc (??? .RESET(rst_n),??? .LEDS_TRI_O(led),??? .clock_generator_0_CLKIN_

pin(clk_100m)??? );?endmodule???????? 最后我們雙擊“Generate Prog

ramming File”完成硬件系統的編譯和下載文件生成。????????? 下一步我們把平臺轉移到SDK,在工程目錄下新建一個名為SDK_workspace的文件夾,然后打開SDK時需要選擇一個workspace,如圖15所示,對應定位到SDK_workspace文件夾下即可。

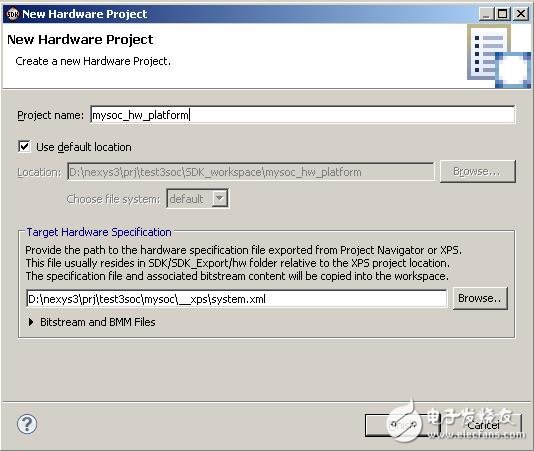

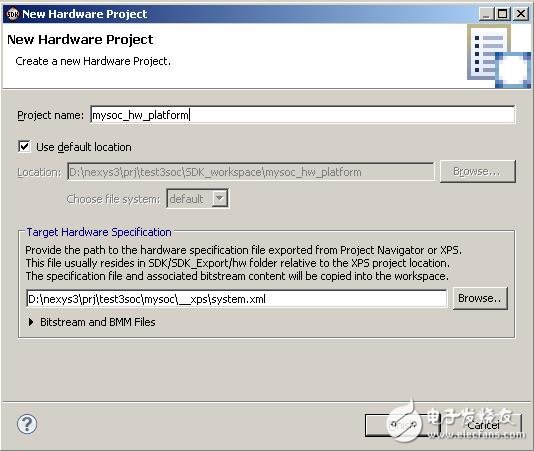

圖15 workspace設置???????? 進入SDK后,菜單欄上選擇FileàNewàXilinx C Project,然后在“New Hardware Project”中輸入Project name,并選擇工程目錄下的mysoc\__xps\system.xml作為Target Hardware Specif

ication。此配置頁面主要是設置軟件工程的硬件平臺。

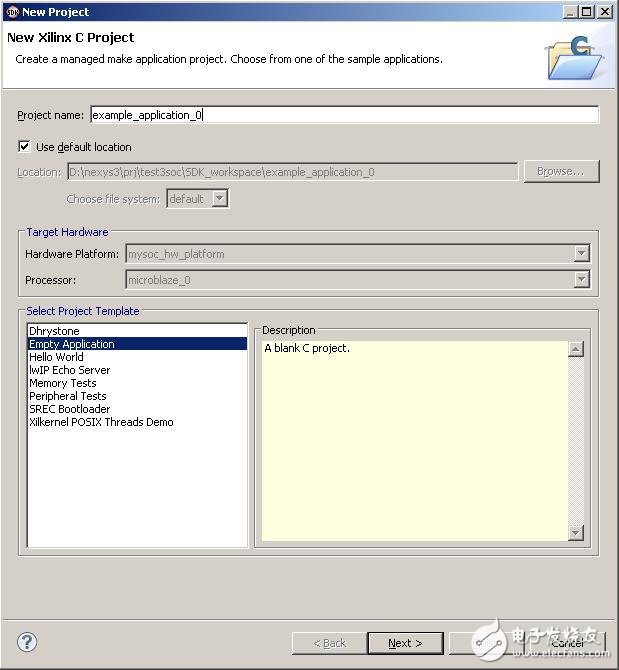

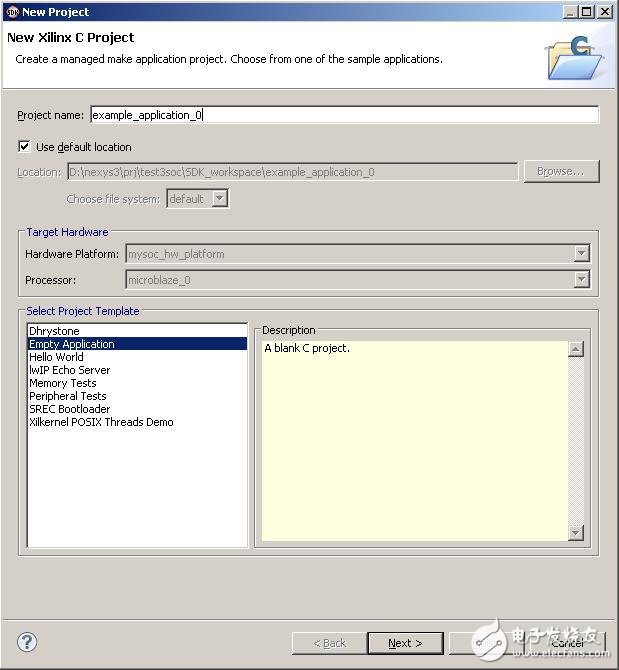

圖16 硬件平臺配置頁面???????? 下一配置頁面如圖17所示,這里設置軟件工程的Project name,并且選擇Select Project Template為“Empty Application”。其余選項使用默認,完成設置。

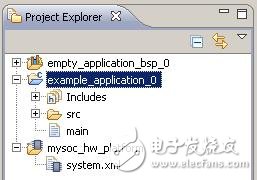

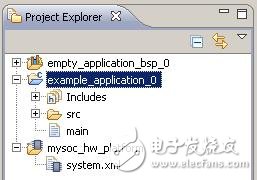

圖17 軟件工程配置頁面???????? 此時在Project Explorer下出現了mysoc_hw_platform、empty_application_bsp_0和example_application_0三個文件夾。在example_application_0上右擊并選擇NewàSource file,新建一個名為main.c的源文件,如圖18所示。

圖18 軟件工程文件夾???????? 在main.c中編寫一段簡單的流水燈測試代碼,如下所示:/* ------------------------------------------------------------ *//*????????????? Include File Definitions??????????????????????? *//* ------------------------------------------------------------ *///#include "xil_types.h"??? //This file contains b

asic types for Xilinx software IP.#include "xparameters.h"? //The hardware configuration describing constants#include "xgpio_l.h"??? //This header file contains identifiers and driver functions?#define? uchar unsigned char#define? uint? unsigned short?/* ------------------------------------------------------------ *//*????????????? delay function????????????????????????????????? *//* ------------------------------------------------------------ */void delay(uint cnt){??? uint i,j;??? for(i=0;i

圖19 FPGA燒錄原本Program FPGA用于在線燒錄FPGA器件,但是Nexys3目前的USB連接方式并不直接支持(這個后面再研究,話說“白貓黑貓抓到老鼠都是好貓”,咱只要能下載進去就行),但是不要緊,我們還有Adept呢。這里配置一下待燒錄文件的一些基本信息,然后點擊Program后雖然會報錯并提示無法成功燒錄,但是與此同時在mysoc_hw_platform文件夾下生成了一個包含軟硬件燒錄的download.bit文件,最后我們使用Adept將這個文件下載到Nexys3中即可實現在線運行的流水燈了。?轉載自:特權同學的博客

圖19 FPGA燒錄原本Program FPGA用于在線燒錄FPGA器件,但是Nexys3目前的USB連接方式并不直接支持(這個后面再研究,話說“白貓黑貓抓到老鼠都是好貓”,咱只要能下載進去就行),但是不要緊,我們還有Adept呢。這里配置一下待燒錄文件的一些基本信息,然后點擊Program后雖然會報錯并提示無法成功燒錄,但是與此同時在mysoc_hw_platform文件夾下生成了一個包含軟硬件燒錄的download.bit文件,最后我們使用Adept將這個文件下載到Nexys3中即可實現在線運行的流水燈了。?轉載自:特權同學的博客

圖19 FPGA燒錄原本Program FPGA用于在線燒錄FPGA器件,但是Nexys3目前的USB連接方式并不直接支持(這個后面再研究,話說“白貓黑貓抓到老鼠都是好貓”,咱只要能下載進去就行),但是不要緊,我們還有Adept呢。這里配置一下待燒錄文件的一些基本信息,然后點擊Program后雖然會報錯并提示無法成功燒錄,但是與此同時在mysoc_hw_platform文件夾下生成了一個包含軟硬件燒錄的download.bit文件,最后我們使用Adept將這個文件下載到Nexys3中即可實現在線運行的流水燈了。?轉載自:特權同學的博客

圖19 FPGA燒錄原本Program FPGA用于在線燒錄FPGA器件,但是Nexys3目前的USB連接方式并不直接支持(這個后面再研究,話說“白貓黑貓抓到老鼠都是好貓”,咱只要能下載進去就行),但是不要緊,我們還有Adept呢。這里配置一下待燒錄文件的一些基本信息,然后點擊Program后雖然會報錯并提示無法成功燒錄,但是與此同時在mysoc_hw_platform文件夾下生成了一個包含軟硬件燒錄的download.bit文件,最后我們使用Adept將這個文件下載到Nexys3中即可實現在線運行的流水燈了。?轉載自:特權同學的博客

電子發燒友App

電子發燒友App

評論