本文敘述概括了FPGA應用設計中的要點,包括,時鐘樹、FSM、latch、邏輯仿真四個部分。

FPGA的用處比我們平時想象的用處更廣泛,原因在于其中集成的模塊種類更多,而不僅僅是原來的簡單邏輯單元(LE)。早期的FPGA相對比較簡單,所有的功能單元僅僅由管腳、內部buffer、LE、RAM構建而成,LE由LUT(查找表)和D觸發器構成,RAM也往往容量非常小。現在的FPGA不僅包含以前的LE,RAM也更大更快更靈活,管教IOB也更加的復雜,支持的IO類型也更多,而且內部還集成了一些特殊功能單元,包括:

DSP:實際上就是乘加器,FPGA內部可以集成多個乘加器,而一般的DSP芯片往往每個core只有一個。換言之,FPGA可以更容易實現多個DSP core功能。在某些需要大量乘加計算的場合,往往多個乘加器并行工作的速度可以遠遠超過一個高速乘加器。

SERDES:高速串行接口。將來PCI-E、XAUI、HT、S-ATA等高速串行接口會越來越多。有了SERDES模塊,FPGA可以很容易將這些高速串行接口集成進來,無需再購買專門的接口芯片。

CPU core:分為2種,軟core和硬core。軟core是用邏輯代碼寫的CPU模塊,可以在任何資源足夠的FPGA中實現,使用非常靈活。而且在大容量的FPGA中還可以集成多個軟core,實現多核并行處理。硬core是在特定的FPGA內部做好的CPU core,優點是速度快、性能好,缺點是不夠靈活。

不過,FPGA還是有缺點。對于某些高主頻的應用,FPGA就無能為力了。現在雖然理論上FPGA可以支持的500MHz,但在實際設計中,往往200MHz以上工作頻率就很難實現了。

FPGA設計要點之一:時鐘樹

對于FPGA來說,要盡可能避免異步設計,盡可能采用同步設計。同步設計的第一個關鍵,也是關鍵中的關鍵,就是時鐘樹。一個糟糕的時鐘樹,對FPGA設計來說,是一場無法彌補的災難,是一個沒有打好地基的大樓,崩潰是必然的。

具體一些的設計細則:

1)盡可能采用單一時鐘;

2)如果有多個時鐘域,一定要仔細劃分,千萬小心;

3)跨時鐘域的信號一定要做同步處理。對于控制信號,可以采用雙采樣;對于數據信號,可以采用異步fifo。需要注意的是,異步fifo不是萬能的,一個異步fifo也只能解決一定范圍內的頻差問題。

4)盡可能將FPGA內部的PLL、DLL利用起來,這會給你的設計帶來大量的好處。

5)對于特殊的IO接口,需要仔細計算Tsu、Tco、Th,并利用PLL、DLL、DDIO、管腳可設置的delay等多種工具來實現。簡單對管腳進行Tsu、Tco、Th的約束往往是不行的。

可能說的不是很確切。這里的時鐘樹實際上泛指時鐘方案,主要是時鐘域和PLL等的規劃,一般情況下不牽扯到走線時延的詳細計算(一般都走全局時鐘網絡和局部時鐘網絡,時延固定),和ASIC中的時鐘樹不一樣。對于ASIC,就必須對時鐘網絡的設計、布線、時延計算進行仔細的分析計算才行。

FPGA設計要點之二:FSM

FSM:有限狀態機。這個可以說時邏輯設計的基礎。幾乎稍微大一點的邏輯設計,幾乎都能看得到FSM。FSM分為moore型和merly型,moore型的狀態遷移和變量無關,merly型則有關。實際使用中大部分都采用merly型。

FSM通常有2種寫法:單進程、雙進程。

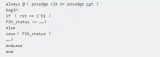

初學者往往喜歡單進程寫法,格式如下:

always @( posedge clk or posedge rst )

begin

if ( rst == 1‘b1 )

FSM_status <= 。。.。。.;

else

case ( FSM_status )

。。.。。.;

endcase

end

簡單的說,單進程FSM就是把所有的同步、異步處理都放入一個always中。

FPGA設計要點之三:latch

首先回答一下:

1)stateCAD沒有用過,不過我感覺用這個東東在構建大的系統的時候似乎不是很方便。也許用system C或者system Verilog更好一些。

2)同步、異步的叫法是我所在公司的習慣叫法,不太對,不過已經習慣了,呵呵。

這次講一下latch。latch的危害已經說過了,這里不再多說,關鍵講一下如何避免。

1)在組合邏輯進程中,if語句一定要有else!并且所有的信號都要在if的所有分支中被賦值。

always @( * ) begin

if ( sig_a == 1‘b1 ) sig_b = sig_c;

end

這個是絕對會產生latch的。

正確的應該是

always @( * ) begin

if ( sig_a == 1’b1 ) sig_b = sig_c;

else sig_b = sig_d;

end

另外需要注意,下面也會產生latch。也就是說在組合邏輯進程中不能出現自己賦值給自己或者間接出現自己賦值給自己的情況。

always @( * ) begin

if ( rst == 1‘b1 ) counter = 32’h00000000;

else counter = counter + 1;

end

但如果是時序邏輯進程,則不存在該問題。

2)case語句的default一定不能少!

原因和if語句相同,這里不再多說了。

需要提醒的是,在時序邏輯進程中,default語句也一定要加上,這是一個很好的習慣。

3)組合邏輯進程敏感變量不能少也不能多。

這個問題倒不是太大,verilog2001語法中可以直接用 * 搞定了。順便提一句,latch有弊就一定有利。在FPGA的LE中,總存在一個latch和一個D觸發器,在支持DDR的IOE(IOB)中也存在著一個latch來實現DDIO。不過在我們平時的設計中,對latch還是要盡可能的敬而遠之。

FPGA設計要點之四:邏輯仿真

仿真是FPGA設計中必不可少的一步。沒有仿真,就沒有一切。仿真是一個單調而繁瑣的工作,很容易讓人產生放棄或者偷工減料的念頭。這時一定要挺住!仿真分為單元仿真、集成仿真、系統仿真。

單元仿真:針對每一個最小基本模塊的仿真。單元仿真要求代碼行覆蓋率、條件分支覆蓋率、表達式覆蓋率必須達到100%!這三種覆蓋率都可以通過MODELSIM來查看,不過需要在編譯該模塊時要在Compile option中設置好。

集成仿真:將多個大模塊合在一起進行仿真。覆蓋率要求盡量高。

系統仿真:將整個硬件系統合在一起進行仿真。此時整個仿真平臺包含了邏輯周邊芯片接口的仿真模型,以及BFM、Testbench等。系統仿真需要根據被仿真邏輯的功能、性能需求仔細設計仿真測試例和仿真測試平臺。系統仿真是邏輯設計的一個大分支,是一門需要專門學習的學科。

Xilinx針對平板顯示器LED背光的FPGA解決方案

1.概述

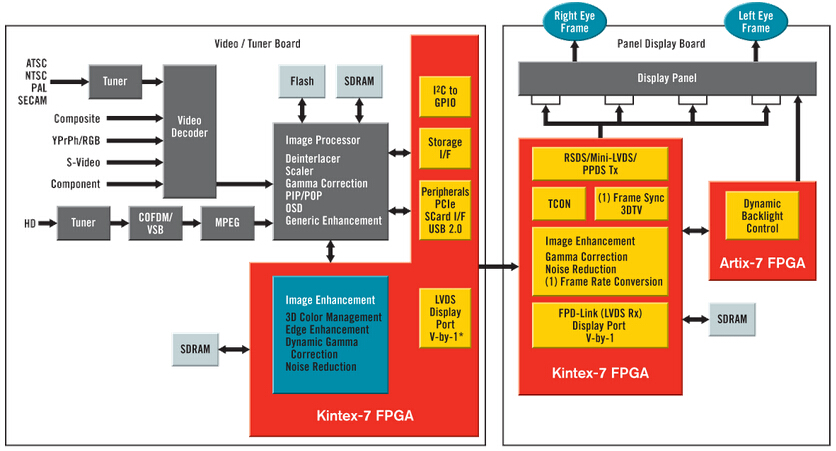

Kintex-7 FPGA 和 Artix-7 提供的功能使得平板顯示器制造商能夠提高圖像質量、降低功耗和削減成本。

2.方案特性

為 LED 背光控制器實現了復雜的局部調光和照明補償算法。

生產具有不同的 LED 區域數量和 LED 布局的直接型照明顯示器,同時調整照明以便與不同供應商生產的面板的物理特性相匹配。

為顯示器添加 3D 功能。

與利用上一代 FPGA 實現的設計相比,其系統 FPGA 功耗降低了32%

與利用上一代 FPGA 實現的設計相比,其系統 FPGA 成本削減了30%

利用 Artix-7 FPGA 實現的設計將 LED 背光控制器的功耗降低 63%

靈活的并行/串行接口技術利用 PCI Express、USB 2.0、DisplayPort 和 V-by-One 技術實現了芯片-芯片和板-板通信

3.75Gbps V-by-One@HS 的 16 或 32 信道 (per Thine’s spec)

5.4Gbps DisplayPort 1.2 的多端口 (per VESA spec)

1,866Mbps DDR3 存儲器接口實現了基于商用存儲器的視頻數據緩沖器

1.6Gbps LVDS I/O 降低了并行接口內的跡線數量

芯片級封裝實現了基于4層 PCB 的低成本生產

方案框圖:

3.業界領先的系統解決方案

Kintex?-7 FPGA 能夠提供高信號處理能力和低功耗,從而滿足各種應用需求,包括:

1)LED 背光平板顯示器和 3DTV

2)LTE 基帶

3)攜帯型超音波裝置

4)多模射頻

5)高端消費類數碼單反相機

6)Video-over-IP 網關

相關芯片介紹:賽靈思Kintex-7 FPGA 系列芯片簡介

基于京微雅格低功耗FPGA的8b/10b SERDES的接口設計

串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立的ASSP 或ASIC 器件。在過去幾年中已經看到有內置SERDES 的FPGA 器件系列,但多見于高端FPGA芯片中,而且價格昂貴。

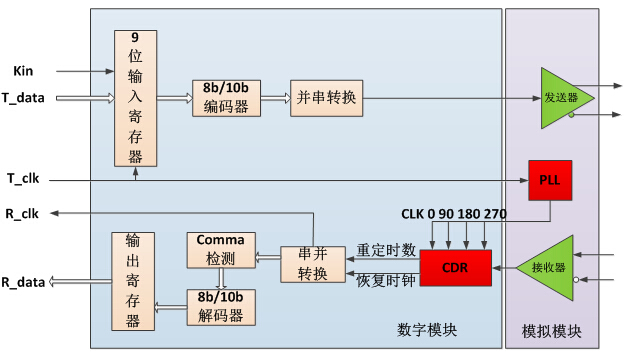

本方案是以CME最新的低功耗系列FPGA的HR03為平臺,實現 8/10b的SerDes接口,包括SERDES收發單元,通過完全數字化的方法實現SERDES的CDR(Clock Data Recovery,時鐘數據恢復),完成100~200Mhz的板間SERDES單通道通信,該SERDES接口方案具有成本低、靈活性高、研發周期短等 特點。

1硬件接口:

硬件的接口如上圖所示,主要包括發送與接收模塊。

發送模塊包括8b/10b編碼器,并串轉換器,鎖相環(PLL)頻率合成器和發送器,接收模塊包括 8b/10b解碼器,Comma 檢測器,串并轉換器,時鐘數據恢復器(CDR)和接收器。

8b/10b編碼器用于將從上層協議芯片發送過來的字節信號映射成直流平衡的 10 位8b/10b 編碼,并串轉換用于將 10 位編碼結果串行化,并串轉換所需的高速、低抖動時鐘由鎖相環提供,發送器用于將 CMOS 電平的高速串行碼流轉換成抗噪聲能力較強的差分信號,經背板連接或光纖信道發送到接收機。

在接收端,接收器將接收到的低擺幅差分信號還 原為 CMOS 電平的串行信號,CDR 從串行信號中抽取時鐘信息,完成對串行數據的最佳采樣,串并轉換利用 CDR 恢復的時鐘,將串行信號轉換成 10 位的并行數據,Comma 檢測器檢測特殊的 Comma 字符,調整字邊界,字邊界正確的并行數據經過 8b/10b 解碼,還原為字節信號,傳送到上層協議芯片,完成整個信息傳輸過程。

實際的設計中,CDR部分是由純邏輯電路完成的,為設計的核心的部分,下面將介紹數字CDR在HR03的實現方案。

2數字CDR:

CDR模塊作用是從數據中恢復嵌入的時鐘,然后接收器按照恢復的時鐘進行數據位對齊并通過comma進行字對齊。最后,將數據進行8b/10b解碼,供系統使用。

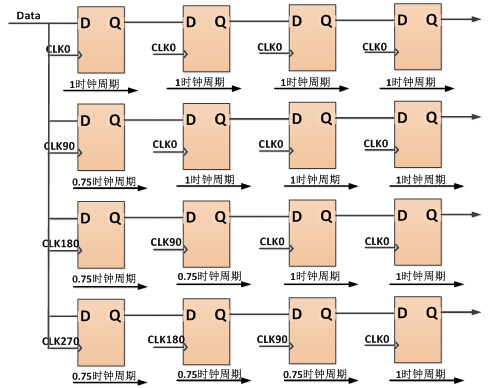

本方案采用同頻多相的時鐘采樣方法,具體實現過程利用PLL產生4個時鐘頻率相同,相位相差90度的時鐘,分別為clk0、clk90、clk180、 clk270,這四個時鐘輸出完全同步,利用4個時鐘對數據進行采樣,以獲得4倍過采樣的效果,具體的實現過程如下圖所示:

在數據時鐘恢復時,將到來的數據分別輸入到四個觸發器,分別用4個不同的相位進行采樣,要注意保證從輸入引腳到四個觸發器的延遲基本一致。

第一列觸發器的觸發分別由時鐘CLK0、CLK90、CLK180、CLK270的上升沿觸發,按照這樣的方式來觸發就可以得到四個數據采樣點。這樣就 將原始時鐘周期分成了四個單獨的90度的區域,如果系統時鐘為200MHz,上圖所示的電路就相當于產生了800MHz 的采樣速率。

僅通過一階的觸發器,輸出的采樣數據存在亞穩態的問題,因此需對采樣點作進一步的處理。這里可將四個采樣點通過進一步的觸發,除掉亞穩態的問題,從而使采 樣點移到下一個相同的時鐘域。通常,亞穩態的去除要經過兩三級的處理,這就使得在有效數據輸出前會有數位無效的數據,在數據采樣的第一個階段,電路檢測數 據線上數據的傳輸。當檢測到有數據傳輸時,對傳輸數據的有效性進行確認。確認數據有效后,輸出高電平來指示采樣點有數據傳輸。

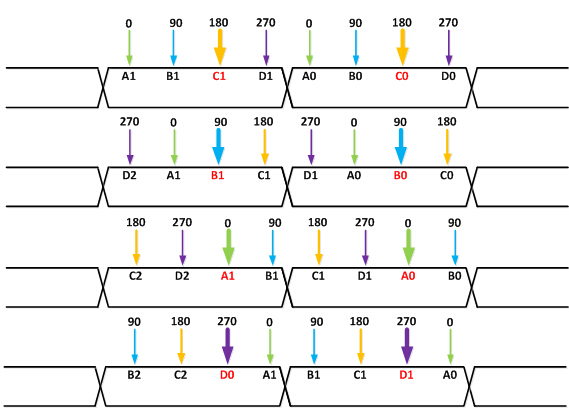

因為最終有四個輸出,所以需要一個復用器來選擇數據。發送數據與采樣時鐘的對應關系如上圖所示,其對應關系分為4種情況,每種情況下對應一個最佳的采樣 時鐘,系統通過對數據邊沿位置信息的判斷,來確定哪路時鐘為最佳采樣時鐘,并利用復用器從選定的時鐘域中選擇數據位,例如檢測電路確定從時鐘域A中采樣的 數據有效,那么將時鐘域A中采樣的數據通過輸出端輸出。

3結束語:

通過對純數字電路的CDR電路,在沒有硬核的支持下,完成了FPGA上SERDES的接口設計,并通過實驗的傳輸測試,在HR03的FPGA上,可完成100~200Mbps的數據傳輸。

作者:京微雅格系統應用工程師 易晶晶

基于FPGA的智能小車設計方案

智能監控機器人是近年來機器人應用工程中一項前沿性的題目,智能化探測小車是智能行走機器人的一種。智能監控機器小車就是針對上述情況,在參考 了目前大多數智能機器人的基礎上,以降低成本為原則設計的。小車具備溫濕度和環境監測、無線通信、躲避障礙物以及無線遙控等功能。此智能監控機器小車與目 前已有的同類設計相比,有性價比高、操作方便、可靠性好、功耗小等優點。

1 系統結構及硬件設計

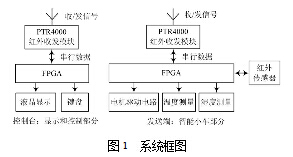

整個系統由發送端(智能小車部分)和接收端(控制臺:控制和顯示部分)組成,如圖1所示。系統由傳感器系統、動力及轉向系統、CCD圖像傳感器模塊、 LCD顯示、溫度和濕度測量電路和供電系統等組成,整個系統的控制核心以2片Altera公司的EP2C20F484為核心,在Altera公司的 QuartusⅡ和SoPC Builder開發環境中完成。根據系統硬件結構添加所需要的外圍模塊并生成NiosⅡCPU。

1.1 供電系統

小車安裝了兩塊充電電池,分別為FPGA開發板(FPGA控制電路)和小車運動提供能量,電池置于車身底部。

1.2 傳感器系統

系統采用了6個紅外對射傳感器,通過FPGA配置的NiosⅡCPU來檢測傳感器信號實現小車躲避障礙物的功能。漫反射型紅外對射傳感器也稱光電開關, 是一種集發射器和接收器于一體的傳感器,多用于檢測障礙物。原理是由光電開關輻射出來的調制紅外光束被檢測物體反射回來,紅外線經同步選通接收,由電子開 關線路驅動回路,從而來檢測物體的有或無。當被檢測物體的表面光亮或其反光率極高時,漫反射式的光電開關是首選的檢測模式。這種電路模塊體積小,信號容易 轉化為標準電平。

1.3 動力及轉向系統

本小車有左右輪兩個電機及龜機驅動。驅 動電路采用了CT Microelecttonics公司的大功率直流電機驅動芯片L298,最高支持50 V電壓,最大電流為5 A,滿足大功率電動機的要求,外圍電路簡單,同時,由于該芯片為雙路結構,分別控制左右電動機,增加了電路的可靠性,減少了復雜性。電機控制采用PWM脈 沖寬度調制方式來控制汽車的前進速度。由NiosⅡCPU寫入控制字,可得到不同占空比的PWM驅動信號,此PWM信號送入電機驅動芯片的控制端來調節速 度。

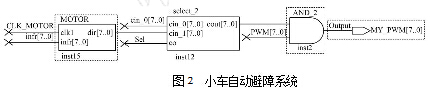

1.4 小車自動避障系統

小車自動避障系統采用Verilog HDL語言編寫驅動電路。該模塊(見圖2中的MOTOR)和一個數據選擇器(見圖2中的select_2)相連來實現自動避障與人工遙控之間的切換。當小 車上NiosⅡCPU的SEL管腳輸出低電平時,數據選擇器將把該模塊的輸出作為電機的控制指令。這樣設計的好處在于設計具有響應迅速,不需要NiosⅡ CPU參與,提高了CPU處理濕度、溫度數據并控制無線模塊收發數據的效率。該邏輯電路的工作原理是根據紅外傳感器發回來的數據,經過邏輯判斷來控制電機 的工作狀態。

1.5 小車的人工控制

小車的人工控制和自動避障之間的轉換由一個數據選擇器控制,當小車上NiosⅡCPU的SEL管腳輸出高電平時,數據選擇器將把無線模塊所發送過來的指令作為電機的控制指令,實現了對小車的無線控制。

1.6 溫度和濕度測量

在溫度測量系統中,采用抗干擾能力強的新型數字溫度傳感器DS18B20,該系統設計中將DS18B20的1,3引腳分別接于FPGA板的GND 和+3.3 V管腳,2引腳接FPGA的I/O腳,傳輸控制及數據信號。DS18B20最高可用12位表示溫度值,最高5位為符號位。

采用HS1101濕度傳感器,具有響應速度快,工作溫區寬(-40~+100℃),測量范圍大(0%~100%RH),可靠性高,穩定性好,功耗低,外圍電路簡單等優點。

工作原理為:用HS1101傳感器與TLC555構成多諧振蕩器,HS1101傳感器內部電容會隨濕度的變化而變化,從而使輸出頻率發生變化。編寫VHDL程序在FPGA設計一個頻率計可精確的測出頻率值,通過輸出頻率與濕度的關系便可得到濕度值。

1.7 無線收發系統

系統采用PTR4000無線嵌入式模塊,工作頻率為2.4 GHz,最高工作速率可達1 Mb/s,高效GMSK調制,且有CRC檢錯功能。具有低功耗,抗干擾能力強,體積小等優點。主要有三種工作模式,分別為:配置模式、 ShockBurst發送模式和ShockBurst接收模式。

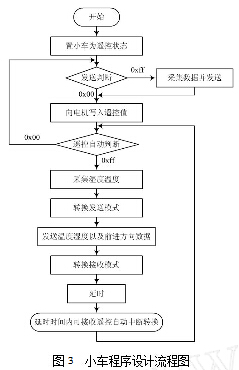

2 軟件設計和調試

采用NiosⅡ進行C語言編程。NiosⅡ集成開發環境(IDE)是NlosⅡ系列嵌入式處理器的基本軟件開發工具。所有軟件開發任務都可以在Nios ⅡIDE下完成,包括編輯、編譯和調試程序。NiosⅡIDE是基于開放式的、可擴展Eclipse IDE project工程以及EclipseC/C++開發工具(CDT)工程,NiosⅡIDE為GCC編譯器提供了一個圖形化用戶界面,可以支持標準C。 NiosⅡIDE編譯環境自動地生成一個基于用戶特定系統配置(SoPC Builder生成的SoPC文件)的makefile,有利于程序的開發。

NiosⅡIDE包含一個強大的、在GNU調試器基礎之上的軟件調試器——GDB。完成軟件代碼的編寫后,可以對代碼進行仿真和調試。Nios-Ⅱ IDE提供了一個方便的閃存編程方法。任何連接到FPGA的兼容通用閃存接口(CFI)的閃存器件都可以通過NiosⅡIDE閃存編程器來燒結。針對本設 計及應用,編寫了系統控制程序和LCD顯示程序。流程圖如圖3所示。

3 系統調試

小車系統需要測試能否準確接收控制臺發送的指令并控制小車運動或停止,以及向前、后、左、右轉向。還要測試主控機能否準確接收小車采集到的溫度以及濕度 信息,能否正確顯示。經過多次測試,發現由于系統程序是采用收發循環轉換的模式,為了讓兩個系統能夠收到對方發的信息,對小車的遙控與自動部分進行簡單的 分化。自動情況下,控制臺為主要接收端,小車為主要發送端,一般情況下小車發送數據到控制臺,需要自動到遙控的轉換時,通過在延時時間內進行中斷來實行從 自動到遙控的轉換;在遙控狀態下,控制臺為主要發射端,小車為接收端,一般情況下控制臺發送小車行進指令到小車,需要采集數據時,通過溫度、濕度采集按鍵 來對小車進行收發轉換,同時小車發出采集數據指令,之后再次轉為接收模式。這樣做之后使小車與控制臺的軟件部分清晰明了,小車的行進以及采集顯示數據能夠 實時的進行。

濕度測量系統需要測試是否能夠精準輸出頻率值。采用芯片LM555手冊上推薦的電路,由于元件的誤差,使輸出的頻率并不精 確,經過與標準的濕度儀進行比對,通過參數調整,用直線做近似,最后得到的頻率值誤差在幾赫茲(頻率范圍是6 008~7 314Hz),經過預算得到很準確的濕度值。開始求濕度值時用的是解一元三次方程的方法,由于計算量大,對小車的行進會有很大影響,后來在小車端只是把小 車采集到的頻率值通過紅外天線傳輸到主控端,并將原先的小車自動避障由NiosⅡCPU控制改為由Verilog編寫的硬件模塊控制,最后在控制臺做濕度 值的計算。這樣的更改既減少了小車NiosⅡCPU的工作量,同時由于小車的自動避障改為由獨立的Verilog模塊控制,運行起來很流暢。

對于無線收發系統,要測試其可靠性以及發送或接收的信息的準確性。測試方法是單獨設計了一個軟核下載到SoPC中,并編寫一段程序用于測試是否正確寫入 配置控制字,是否能夠進行ShockBurst模式的接收或發送。問題是對天線各模式時序的把握,一開始寫的程序總是不能正確寫入配置字,反復調試,并用 數字示波器觀察寫入配置字的瞬間過程以及各延時的時間,最后測試成功,并把發送或接收的狀態用LED顯示出來,每發送或接收到一個數據包就讓LED閃一 下。

4 結語

本設計以FPGA嵌入NiosⅡ軟核處理器為核心,輔以必要的外圍 電路,構成了高度集成化的片上系統。另外,SoPC系統的柔性配置,使得可以基于此系統擴展片外存儲器和多路輸出。設計的小車具有較強的避障能力,且能通 過接收端對其進行方便的控制,溫度和濕度采集均達了較高的精度,并且能實現動態顯示,無線收發模塊的有效范圍最遠可達300 m,可應用于較為惡劣的環境,可代替人進行溫度和濕度的實地檢測。

基于SoC FPGA進行工業設計及電機控制

工業市場的近期發展推動了對具有高集成度、高性能、低功耗FPGA器件的需求。設計人員更喜歡網絡通信而不是點對點通信,這意味著可能需要額外的控制器用于通信,進而間接增加了BOM成本、電路板尺寸和相關NRE(一次性工程費用)成本。

總體擁有成本用于分析和估計購置的壽命周期成本,它是所有與設計相關的直接和間接成本的擴展集,包括工程技術成本、安裝和維護成本、材料清單(BOM)成本和NRE(研發)成本等。通過考慮系統級因素有可能最大限度地減少總體擁有成本,從而帶來可持續的長期盈利能力。

美高森美公司(Microsemi)提供具有硬核ARM Cortex-M3微控制器和IP集成的SmartFusion2 SoC FPGA器件,它采用成本優化的封裝,具有減少BOM和電路板尺寸的特性。這些器件具有低功耗和寬溫度范圍,能夠在沒有冷卻風扇的極端條件下可靠地運行。 SmartFusion2 SoC FPGA架構將一個硬核ARM Cortex-M3 IP與FPGA架構相集成,可以實現更大的設計靈活性和更快的上市時間。美高森美為電機控制算法開發提供了具有多個多軸電機控制參考設計和IP的生態系 統,使由多處理器解決方案轉向單一器件解決方案(即SoC FPGA)更加容易。

影響TCO的因素

以下是影響系統TCO的一些因素。

(1)長壽命周期。FPGA可以在現場部署之后進行重新編程,這延長了產品的壽命周期,從而使設計人員能夠專注于新產品開發,實現更快的上市時間。

(2)BOM.美高森美基于閃存技術的FPGA在上電時無需啟動PROM或閃存MCU來加載FPGA,它們是零級非易失性/即時啟動器件。與基于SRAM的FPGA器件不同,美高森美基于閃存的FPGA無需附加上電監控器,這是因為閃存開關不會隨電壓而改變。

(3)上市時間。OEM廠商之間的激烈競爭迫切需要更多的產品差異化和更快的上市時間。經過驗證的IP模塊可大幅縮短設計時間。目前已經可以提供多個構 建工業解決方案所需的IP模塊,同時更多的模塊正在開發中。SoC表現出的另一個獨特優勢是可以用于調試FPGA設計。為了調試FPGA設計,可以通過用 于調試的高速接口,利用微控制器子系統從FPGA中提取信息。

(4)工程工具成本。與FPGA開發工具昂貴的概念相反,美高森美提供用于FPGA開發的免費Libero SoC IDE,僅在開發高端器件時才需要付費。

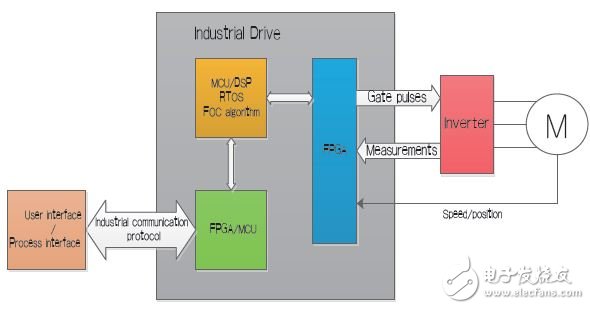

工業驅動系統

工業驅動系統由一個電機控制器件和一個通信器件構成,電機控制器件包含了驅動逆變器的邏輯和保護邏輯,通信器件則使監控控制能夠對運行時間參數進行初始化和修改。

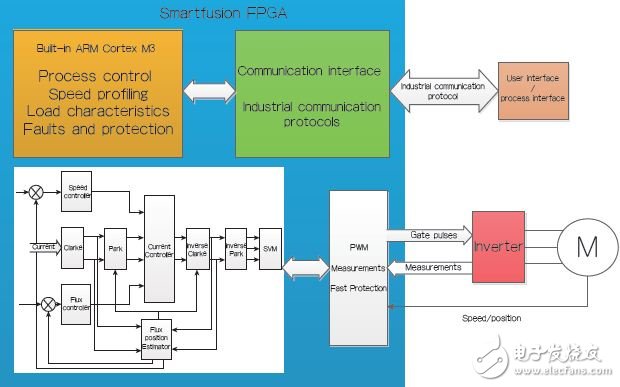

圖1:典型工業驅動系統。

在典型的驅動系統(圖1)中,可能使用多個控制器器件來實現驅動邏輯。一個器件可能執行與電機控制算法相關的計算,第二個器件可能運行與通信相關的任務,第三個器件則可能運行與安全性相關的任務。

多軸電機控制

傳統上,工業電機控制應用使用微控制器或DSP來運行電機控制所需的復雜算法,在大多數傳統的工業驅動中,FPGA與微控制器或DSP一起使用,用于數 據采集和快速作用保護。除了數據采集、PWM生成和保護邏輯,FPGA傳統上并未在實現電機控制算法方面發揮主要作用。

使用微控制器或DSP實現電機控制算法的方法并不容易擴展到多個以獨立速度運行的電機(多軸電機控制),美高森美SmartFusion2 SoC FPGA可以使用單一器件來實現集成且完整的多軸電機驅動控制(圖2)。

圖2:美高森美SmartFusion2 SoC FPGA使用單一器件來實現完整的多軸電機驅動控制。

控制方面可以分為兩個部分。一個部分用于運行磁場定向控制(FOC)算法、速度控制、電流控制、速度估計、位置估計和PWM生成;另一個部分則包括速度 曲線、負載特性、過程控制和保護(故障和報警)。執行FOC算法屬于時間關鍵型,需要在極高的采樣速率下進行(在微秒范圍),特別是針對具有低定子電感的 高速電機。這使得在FPGA中實現FOC算法變得更優越。過程控制、速度曲線和其他保護無需快速更新,因而能夠以較低的采樣速率執行(在毫秒范圍),并且 能夠在內置Cortex-M3子系統中進行編程。

晶體管開關周期在驅動中發揮著重要的作用,如果FOC回路執行時間比開關周期短得多,硬件模塊可以重用于計算第二個電機的電壓。這意味著器件可以在相同的成本下提供更高的性能。

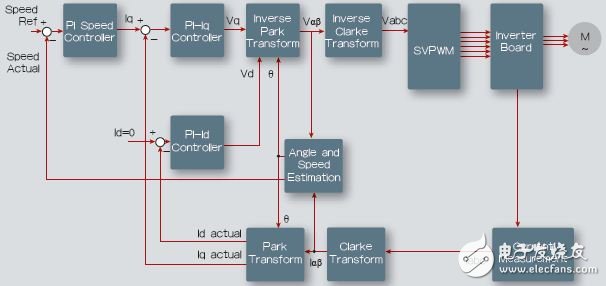

圖3:永磁同步電機的磁場定向控制(FOC)框圖。

(1)電機控制IP模塊。圖3為無傳感器磁場定向控制算法,這一部分將會討論這些模塊,它們作為IP核提供。

● PI控制器。比例積分(PI)控制器是用于控制系統參數的反饋機制,它具有兩個用于控制控制器動態響應的可調增益參數-比例和積分增益常數。PI控制器的 比例分量是比例增益常數和誤差輸入的乘積,而積分分量是累積誤差和積分增益常數的乘積。這兩個分量被加在了一起。PI控制器的積分階段可能在系統中引起不 穩定,因為數據值不受控制地增加。這種不受控制的數據上升稱作積分飽卷,所有的PI控制器實現方案都包括一個抗飽卷機制,用于確保控制器輸出是有限的。美 高森美的PI控制器IP模塊使用hold-on-saturation(保持飽和)算法用于抗飽卷。這個模塊還提供附加特性以設置最初的輸出值。

● 磁場定向控制(FOC)。FOC是通過獨立地確定和控制轉矩和磁化電流分量來為電機提供最優電流的算法。在永磁同步電機(PMSM)中,轉子已經磁化。因 此,為電機提供的電流只用于轉矩。FOC是計算密集型算法,但是美高森美電機控制參考設計已經針對器件資源的最優使用而構建。FOC算法包括 Clarke、Park、逆Clarke和逆Park變換。

● 角度估計。FOC的一個輸入是轉子角度。精確確定轉子角度對于確保低功耗是必不可少的。增添確定位置和速度的物理傳感器會增加系統的成本并降低可靠性。無 傳感器算法有助于消除傳感器,但是增加了計算復雜性。美高森美針對無傳感器控制提供了兩個角度計算算法IP模塊-一個基于Luenberger觀測器,另 一個基于直接反電動勢計算。該公司還提供基于霍爾傳感器和編碼器的單獨參考設計。

● PLL.PLL用于同步信號,在多個應用中有用,例如逆變器的角度估計和電網同步。

● 速率限制器。速率限制器模塊可以實現系統變量或輸入的平滑改變。例如,在電機控制系統中,如果電機所需的速度突然改變,系統可能變得不穩定。為了避免此類情形,速率限制器模塊用于從初始速度轉變到所需的速度。速率限制器模塊可以進行配置以控制改變的速率。

● 空間矢量調制。空間矢量調制模塊改善了直流總線利用率,并消除了晶體管開關的短脈沖。因為晶體管開啟/關斷時間比脈沖持續時間長,短脈沖會導致不正確的開關行為。

● 三相PWM生成。在所有計算的最后,可以得到三相電機電壓。這些電壓用于生成逆變器中晶體管的開關信號。PWM模塊為六個(三個高側和三個低側)晶體管產 生開關信號,并且具有死區時間和延遲時間插入等先進特性。可編程的死區時間插入特性有助于避免逆變器引腳上的災難性短路情況。可編程的延遲時間插入特性使 ADC測量與PWM信號生成能夠同步。該模塊可以配置成與僅由N-MOSFET組成的逆變器或同時包括N-MOSFET和P-MOSFET的逆變器一起工 作。

(2)在SoC中調試FPGA設計。通常,在微控制器上調試設計比在FPGA上進行調試相對簡單一些。在SoC中,可以利用 FPGA的高性能,同時保持在微控制器中更快速調試的優勢。美高森美SmartFusion2 SoC FPGA中的微控制器子系統和FPGA架構可以通過AMBA APB或AXI總線彼此進行通信。這樣可以把測試數據注入FPGA架構中,或者從FPGA架構中記錄調試數據,從而幫助實現運行時間的內部數據可視化,用 于實時調試。固件代碼可以單步運行,在代碼中可以設置斷點來分析FPGA寄存器數據。

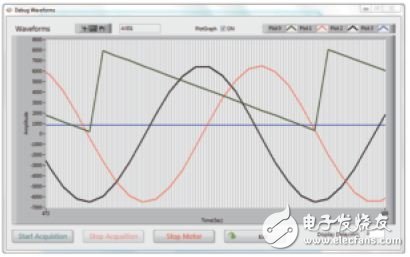

基于SmartFusion2 SoC FPGA的多軸電機控制解決方案通過USB連接至主機PC,并與圖形用戶界面(GUI)通信,進行啟動/停止電機,設置電機速度值和其他系統參數,描繪多達四個系統變量,例如電機速度、電機電流和轉子角度(圖4)。

圖4:GUI的屏幕截圖-繪制內部參數:轉子角度(綠色)、Valpha(紅色)、Vbeta(黑色)、電機速度(藍色)。

(3)生態系統。美高森美提供一組豐富的IP庫,包括前面討論過的數種電機控制功能。這些模塊可以輕易定制,并可以在美高森美器件中移植。使用 Libero SoC軟件的Smart Design工具,這些模塊可以采用圖形方式配置和連接在一起。借助于這些IP模塊,設計人員能夠顯著減少在FPGA中實現電機控制算法所需的時間。

這些IP模塊已在以高達30,000r/min轉速和200kHz開關頻率運行的電機上進行了測試。

工業通信協議

工業網絡的發展趨勢是通過使用更快的網絡通信替代點至點通信。實現此類高速通信需要支持更高的帶寬,這對于同時處理電機控制算法的微控制器或DSP來說 并不容易。在大多數情況下,會使用一個附加的微控制器或FPGA來處理與每個電機控制器的通信。通常使用的基于以太網的協議有PROFINET、 EtherNet/IP和EtherCAT標準,這些標準仍然在演進。其他的協議包括了CAN和Modbus.在這種情況下使用SoC的優勢,是在單一 FPGA平臺上支持多種工業以太網協議標準。

根據終端系統目標,可以通過重用IP和協議棧(用于通信)來優化系統的成本,或者通過仔細地在硬件(FPGA)和軟件(ARMCortex-M3子系統)中劃分功能來優化性能。

美高森美的SmartFusion2 FPGA具有內置CAN、高速USB和千兆以太網模塊作為微控制器子系統的一部分。高速SERDES模塊用于實現涉及串行數據傳送的協議。

安全性

SmartFusion2 SoC FPGA器件具有數項設計和數據安全特性。DPA認證反篡改保護和加密特性等設計安全特性能夠幫助保護客戶的知識產權。SoC FPGA器件還包括數據安全特性,例如ECC硬件加速器、AES-128/256和SHA-256服務。對于數據安全性,可以使用EnforcIT IP Suite和CodeSEAL軟件安全構件,EnforcIT IP包括一套可定制內核(作為網表),有效地將安全層移到硬件中。CodeSEAL將對策注入到固件中,可以獨立地使用,或者用作EnforcIT的提 升。

實現協議的靈活性可讓設計人員使用多個安全層來認證從中央監控控制器進入的信息。

可靠性

在多個市場中安全標準的增長推動了高可靠性的需求,SmartFusion2經設計滿足高可用性、安全關鍵型和任務關鍵型系統的需求,以下是SmartFusion2 SoC FPGA提供的某些可靠性特性。

(1)單粒子翻轉(SEU)免疫零FIT率配置。高可靠性運作需要SEU免疫零FIT率FPGA配置,SmartFusion2架構具有不受α或中子輻 射的免疫能力,因為它使用閃存來配置路由矩陣和邏輯模塊中使用的晶體管。基于SRAM的FPGA在海平面上的FIT(時間失效)率可能為1k~4k,在高 于海平面5,000英尺的位置會高得多。高可靠性應用可接受的FIT率低于20,這使得SmartFusion2最適合這些應用。

(2)EDAC保護。SmartFusion2器件具有錯誤檢測與校正(EDAC)控制器,可防止在微控制器子系統(MSS)存儲器中發生的單粒子翻轉錯誤。

(3)無外部配置器件。在具有大量FPGA的復雜系統中,使用外部配置器件會降低可靠性。在上電時,FPGA需花費時間來進行配置,這在使用多個 FPGA器件的應用中帶來了設計復雜性。SmartFusion2 SoC FPGA在器件內部包含了配置存儲器,它提供了在器件一上電時就開啟的附加優勢。

(4)軍用溫度級器件。SmartFusion2 SoC FPGA器件針對軍用溫度條件進行了全面測試。軍用級器件具有10k和150k邏輯單元,并具有允許訪問密碼加速器的安全特性和數據安全特性。

總結

美高森美SmartFusion2 SoC FPGA使用經過高度優化的電機控制IP模塊和經過驗證的參考設計,提供了數種降低工業設計TCO的特性。從微控制器遷移的客戶將能夠重用某些舊代碼,而 FPGA設計人員將能夠利用FPGA架構和ARM Cortex-M3子系統來創建一個高效的架構,允許電機控制模塊和通信模塊同時駐留在單一器件中。ARM Cortex-M3微控制器子系統的存在,可以實現靈活的設計和智能分區,而針對性能和成本做優化。微控制器子系統還可以在運行時間中注入和記錄數據,加 速調試FPGA設計。SmartFusion2平臺還提供了實現工業通信協議的廣泛選項。它同時提供用于設計和數據安全的多項安全特性,還提供了滿足高可 靠性需求的特性。SmartFusion2系列器件備有強大的生態系統支持,能夠幫助客戶以最低TCO來開發工業解決方案。

利用FPGA實現無線分布式采集系統設計

1 引言

近些年來,隨著電子技術的發展,無線通信技術、計算機網絡的發展,分布式無線數據采集網絡技術開始興起,并迅速的應用到各個領域。在一些地形復雜,不適合人類出現的區域需要進行數據采集的情況下,都可以適當的選擇無線分布式 采集來進行。現有的無線分布式采集系統中,往往使用單片機、DSP等作為系統的主控控制單元。但是由于其自身工作特點,往往對于精確的定時控制以及并行處 理能力上比FPGA弱。隨著FPGA等可編程邏輯器件的發展,為無線數據可靠傳輸提供了很好的實現平臺。采用FPGA作為時序控制和信號處理的處理器,將 使系統電路設計更加簡潔、可靠、靈活,可有效的縮短開發周期,并降低開發成本。

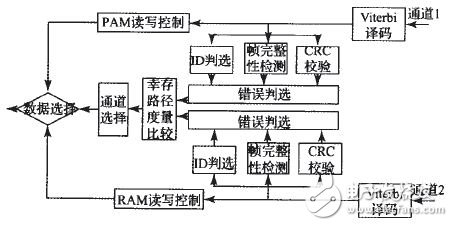

為此,基于CycloneIV+STM32設計了一種新 型的無線分布式采集系統,實現了數據的高可靠和同步傳輸。設計主要由3大部分組成:編碼器、譯碼器、無線收發電臺。在對編碼器、譯碼器同步校準后,對待發 送數據進行卷積編碼,并轉換為串行數據。數據轉換為串行數據后,在串行數據幀頭加入Barker碼來實現幀的同步,并使用2條互為備份的數據傳送通道同時 發送數據。在數據接收端檢測到barker碼后,本地對互為備份的雙通道數據進行viterbi譯碼(本文設計的viterbi譯碼器采用并行結構,大大 的降低譯碼時間)。譯碼結束后,本地對雙通道數據進行循環冗余校驗,并做出判選,最后執行相應指令。并在規定時間給出相應反饋信號。設計的無線采集系統, 即使某一數據通道出現少量錯碼,系統仍能有效的恢復出數據,并進行可靠的數據傳輸。系統添加了監控模塊,實時備份上傳的數據并監控,如發現不能正常上傳, 則啟用備用模塊保證整個系統正常工作。系統不僅能實現數據的高可靠和同步傳輸,而且具有很好的適用性,可廣泛應用工業中。

2 無線分布式采集系統簡介

2.1 系統硬件簡介

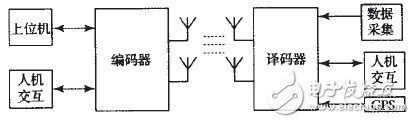

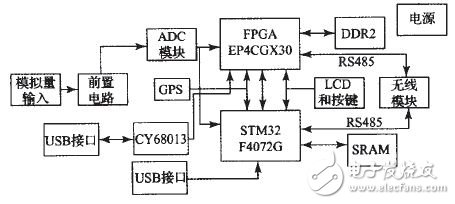

無線分布式采集系統包括編碼器、譯碼器(編碼器、譯碼器硬件完全相同,只是配置邏輯不同,可配置為編碼器、譯碼器、中繼站)和無線通信電臺。如圖1所示,這是一個最簡單的一對一式分布式系統。

圖1 無線分布式采集系統結構

編碼器作為上位機與譯碼器之間的橋梁,通過USB/RS485通道進行發送、接收命令和數據。譯碼器接收編碼器發來的命令進行配置和采集,并將數據存儲至DDR2中。譯碼器收到上傳命令后,上傳數據至編碼器。

編碼器/譯碼器硬件系統框圖如圖2所示。本系統主控單元由FPGA完成。FPGA選用Altera公司的EP4CGX30F407,邏輯單元為 29440個,80個18×18乘法器,多達290個用戶自定義IO。STM32作為監控和備用單元組成系統的基本架構,STM32F407ZG系列是基 于高性能的ARM CortexTM-M4F的32位RISC內核,工作頻率高達168 MHz,該STM32F407ZG系列采用高速嵌入式存儲器(多達1 MB閃存,高達192 KB的SRAM),擁有3個12位ADC,2個DAC,1個低功耗RTC,12個通用16位定時器,2個通用32位定時器。人機交互部分由16X2液晶顯 示字符模塊和4個按鍵組成,其主要功能是通過按鍵對基站編號設置并顯示在LCD上。無線模塊選用WSN-03系列無線模塊作為收發平臺,工作電壓為5 V,傳輸速率和工作頻段等都可配置。目前傳輸速率最大為115 200b ps,工作頻為433 MHz可調。無線模塊與FPGA主要以RXD/A,TXD/B,NRST(復位控制),SET(設置模塊參數),SLP(休眠控制)信號線連接。GPS模 塊選用VKl6U6進行定位,與FPGA以UART接口連接,波特率定位9600 bps。ADC選用基于△-Σ技術的32 bits高精度低功耗模數轉換芯片ADSl282,采樣信號電平范圍:差分輸人一2.5~+2.5 V。單個譯碼器有6個采集通道,以2 k采樣率,采樣時常16 S來計算,單個譯碼器純數據量為6×2 k×16×24-6144 Kbits.考慮到編碼器,一次采樣,8個基站的數據經編碼后數據總量為98 304 Kbits,所以編碼器和譯碼器需增加l片Micron Technology公司的MT47H256M8HG-37E IT(256Meg×8)作為緩存空間。由于DDR2 SDRAM需要特定的控制讀寫時序,系統直接采用Quartus II自帶的“DDR2 SDRAM High-Performance Controller”IP CORE。USB部分由2個通道組成,一個是由FPGA、CY7C68013和USB接口組成;另一個由STM32(自帶USB驅動)和USB接口組成。 同時本設計中還添加了RS485串口,使整個系統與上位機能保持實時通信,為系統的遠程控制提供了可能,并能保持系統更新。

圖2 系統框架

2.2 系統數據流程

系統的數據流程為:同步校準譯碼器,設置各個譯碼器接收命令后的延時-編碼器配置采集參數、命令-譯碼器采集數據保存至DDR2中一各譯碼器分時接收數 據上傳命令并上傳數據-編碼器將數據匯總保存至DDR2-數據收集齊后通過USB/RS485上傳至上位機。譯碼器節點配合計算機對各個點的數據進行輪詢 采集,它包含了無線傳輸模塊和與計算機通信的USB接口。STM32將組幀后的數據備份并實時監控FPGA,如在規定時間或未能按指令進行工 作,STM32將替代FPGA并使FPGA進入斷電狀態。

2.3 系統組幀格式

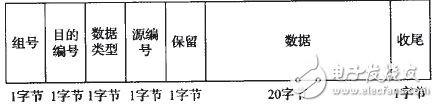

編碼器與譯碼器之間是一對多的關系,譯碼器分時上傳數據,譯碼器有2個通道,譯碼器有唯一的配置編號。數據幀的格式如圖3所示。數據幀中除20字節有效數據之外,還包括組號、目的編號等。

圖3 編碼器、譯碼器間數據幀格式

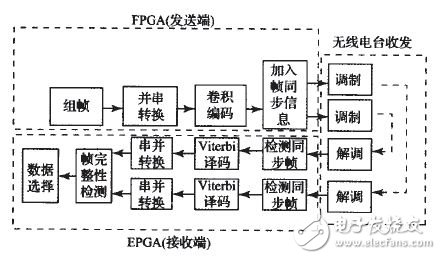

為了改進接收信號質量,本系統引入信道編碼的方法來改善信道質量。具體如圖4所示。發送端對數據進行組幀、并串轉換、卷積編碼、加入同步幀信息后,把數 據發送至無線通信電臺進行調制。接收端的無線通信電臺對信號進行解調后發送數據至接收端的FPGA.接收端的FPGA檢測到幀同步信息后對接下來的數據保 存,并進行Viterbi譯碼。FPGA對雙通道的數據進行冗余校驗,并選擇正確的數據執行相關操作。

圖4 無線數據傳輸

3 無線分布式采集系統數據傳輸的實現

3.1 可靠性

待發數據經卷積編碼,互為備份的雙通道發送,Viterbi譯碼,冗余校驗,數據判選,系統能夠很好的進行無線收發。

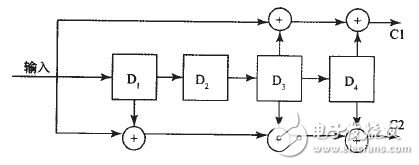

3.1.1 卷積編碼

數據組幀完成后,由低位至高位進行并串轉換,進行卷積編碼。卷積編碼是一種糾錯信道編碼,是由連續的輸入信息序列經編碼后得到連續輸出的編碼序列口。以 (n,k,m)來描述卷積碼,k為每次輸入到卷積編碼器的bit數,行為每k元組碼字對應的卷積碼輸出n元組碼字,m為編碼儲存度。卷積編碼生成的n元組 元不僅與當前輸入有關系,還與前面m一1個輸入的k元組有關系。本系統采用(2,1,4)卷積編碼器,如圖5所示。圖中“+”代表異或。每bit經編碼后 都有2 bit輸出(C1,C2)。

圖5 (2,1,4)卷積編碼器

3.1.2 Viterbi譯碼

接收端有2個接收通道,互不干擾。接收端對2個通道同時譯碼。譯碼采用Viterbi譯碼。Viterbi譯碼算法是一種卷積碼的解碼算法。 Viterbi譯碼根據最大似然算法規則,能達到最佳譯碼,特別適合向前糾錯。以本設計為例,根據圖5,編碼器4個延時狀態(0,1)組成整個編碼器的 16個狀態(D4D3D2D1),每個狀態在編碼器輸入1或0時,跳轉到另一個狀態。并且輸出也隨之改變。譯碼就是編碼的逆過程。算法規定任意t時刻收到 的數據都要進行32次路徑值計算、16次比較,比較后每個狀態只保存一個路徑值,為接下來計算減少了一半的運算量。反復208次,從16條幸存路徑中選出 一條路徑值最小的,反推出這條路徑,得出相應的譯碼輸出。考慮到每次譯碼后,譯碼器都能回到初始狀態,所以源數據最后加了8 bit的“0”。本設計采用并行處理結構,經214個周期還原出源碼。

在設計FPGA邏輯時,基本采用多條并行的流水線技術,譯碼部分 包含4個子模塊:加比選模塊、回溯模塊、存儲模塊和時鐘控制模塊。路徑值的計算和比較在3個時鐘周期內完成,4個模塊同時運行,大大的降低了譯碼時間。另 外,為了提高FPGA效率,系統加入采樣觸發信號,保證系邏輯能夠穩定運行。

3.1.3 數據判選

經譯碼后,接收端 已接收到2組互為備份的數據。經實踐證明,簡單的并聯冗余能大大的提高系統的可靠性。具體選擇流程如圖6所示。2路數據經Viterbi譯碼后,開始接收 一幀數據,并寫入RAM中,同時計算CRC校驗、幀完整性檢測、ID是否符合本地。上述檢測都沒問題時,對2路幸存路徑的度量值進行比較,選擇值小的通道 作為最終數據。

圖6 數據的選擇

3.2 同步的實現

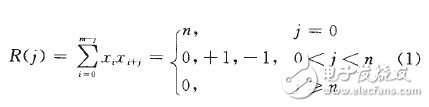

為了保證編碼器和譯碼器之間能嚴格實現同步,數據幀需要加入同步幀。實現幀同步的方法通常有2種:起止同步法和集中式插入同步法。起止式同步比較簡單, 一般在數據碼元的開始和結束位置加入特定的起始和停止脈沖來表示數據幀的開始和結束。集中插入式同步法中插人的同步碼要求在接收端進行同步識別時出現偽同 步的概率盡可能低,并且要求該碼具有尖銳的自相關特性以便識別。7位巴克碼作為幀同步碼,其局部自相關函數為:

由上公式計算可知,7位巴克碼的自相關函數在j一0時出現尖銳的單峰特性。設計中采用2組同步幀頭作為同步碼,同步幀頭由7位巴克碼和1 bit的0組成。

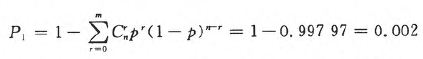

到現在為止,待發數據bit數為:208×2+8×2-432 bits。經調制解調后,接收端檢測幀同步信息,同步信息為2組11100100組成。每組同步信息高7位與7位巴克碼相比,允許出錯位數在1位以內。設 P為碼元錯誤概率,行為同步碼組的碼元數,m為判決其允許碼組中的錯誤碼元最大數,在本系統中行n=7,m=1。在P=0.01時,單一barker碼的 漏同步概率為:

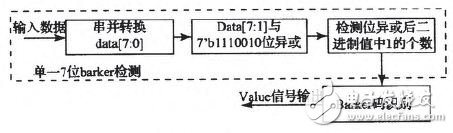

當2組同步幀都滿足時,幀同步建立,接收端保 存接下來的數據。無線通信電臺與FPGA以rs485連接,如圖7所示,FPGA檢測X是否為“0”,當檢測到“0”,不接收端對接下來的數據X與本地巴 克碼對應位進行位異或運算。當檢測1 byte barker碼,錯1位以內時,發出一value脈沖。當檢測到2個value脈沖時,說明同步已建立,接收端開始存儲接下來的數據。

圖7 barler碼識別

4 系統監控模塊的實現

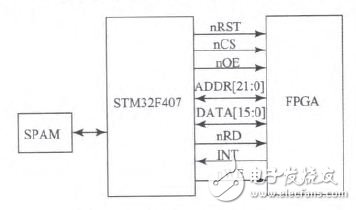

STM32與FPGA連接如圖8所示,由于ARM與FPGA的相互通信直接影響著控制器的性能,所以該并行總線的設計就成為一個非常關鍵的問題。該總線 可以包括芯片的地址總線(ADDR[021])、數據總線(DB[015])、控制總線、復位信號(nRST)以及中斷信號線(INT),其中控制總線包 括使能信號(nOE)、片選信號(nCS)、讀信號(nRD)、寫信號(nWE),這樣做的好處是,將FPGA芯片存儲器化,即STM32可通過對特定地 址的訪問來控制FPGA工作,并且可通過共同的復位信號將STM32與FPGA芯片同時復位,盡量避免總線競爭和冒險現象的出現。

圖8 STM32與FPGA連接

STM32與FPGA同時接收命令,在解析完命令后,FPGA應在規定的時間內發送數據,FH認組幀完成時,發出INT信號至黜2申請中斷。如果 STM32在規定時間內沒有接收到FPGA發來的INT信號,將開始計時,計時時間內未能接收INT信號,STM32將停止FPGA供電電源工作,由 STM32代替FPGA工作,保證整個系統能穩定進行。

結論

在無線分布式采集系統設計中,采用了基于卷積編碼、Viterbi譯碼的編碼和互為備份的雙通道傳輸方案,利用了FPGA內豐富的邏輯資源以及存儲資 源,實現了數據的遠距離同步可靠傳輸。加入備份數據通道后,通過FPGA內部邏輯控制,在硬件上實現了對兩路數據的實時校驗及自動判選,提高了系統的穩定 性和可靠性。相比于“備份-重傳”等機制,該方法實現簡單、實時性好,即使某一通道不能正常工作,系統仍能正常進行。該無線分布采集系統,滿足了現在同步 觸發和數據量不大情況下的傳輸。本文提出的互為備份的雙通道編解碼、數據冗余傳輸機制,亦可應用相關無線傳輸領域,以提高遠距離數據傳輸的可靠性和穩定性。

文章詳情:利用FPGA實現無線分布式采集系統設計

相關文章:

——————————————————————————

FPGA技術相關資料集綿——那些年,我們為之癲狂的FPGA設計

電子發燒友App

電子發燒友App

評論