印象中FPGA市場(chǎng)基本是Altera和Xilinx一統(tǒng)天下,他們的明爭(zhēng)暗斗決定著FPGA的未來,甚至他們各自的家族產(chǎn)品都是對(duì)著干的。Lattice、Actel、Atmel各有其小眾市場(chǎng),再有別的廠商,基本上是不太叫得上來了。

國(guó)產(chǎn)FPGA?是不是聽錯(cuò)了,沒有。記得第一次聽說FPGA前面加了個(gè)定冠詞“國(guó)產(chǎn)”應(yīng)該可以追溯到還和價(jià)格堪比年薪的軍品糾結(jié)的歲月。不過那個(gè)“國(guó)產(chǎn)”二字總感覺和“盜版”諧音,真的不是損誰(shuí),只是實(shí)事求是的說。也許這種模式也叫“中國(guó)特色”吧,好歹比那天忘了在哪位大俠博客看到的“二次包裝”的“中國(guó)制造”強(qiáng)上千百倍。Xilinx早期的XC4打頭的FPGA,也只有ISE4以前的版本支持,“低端”軍品也就這幾款了。所以國(guó)內(nèi)的XX所也很牛,居然能夠逆向設(shè)計(jì)將他們的“國(guó)產(chǎn)”FPGA做得和它完全兼容,不止是PIN2PIN,甚至連開發(fā)工具他們都不用徒手打造了,告訴我們完全替代現(xiàn)有的Xilinx器件。

有時(shí)候不得不感嘆,中國(guó)人很牛。外國(guó)人可以做到的,基本上沒有中國(guó)人做不到的。時(shí)光荏苒,已不再需要靠那些“可靠”換“性能”的片子干活了。而FPGA的成本卻越來越成為產(chǎn)品開發(fā)中揮之不去的夢(mèng)魘,于是乎,老板想盡辦法要壓榨FPGA的成本,這次找來了又一個(gè)“國(guó)產(chǎn)”準(zhǔn)備在低端低成本的應(yīng)用中大干一場(chǎng)。不過幾番觀察下來,特權(quán)同學(xué)開始對(duì)此“君”頗有好感,它也許算不上真正意義上的“國(guó)產(chǎn)”,但是多少讓人感受到了它走的是一條“正規(guī)”有“前途”的路子。

其實(shí)也只是昨天才開始正式的和這家名為Agate Logic的FPGA廠商有了一些“親密”接觸。它的開發(fā)工具,它的開發(fā)流程,它的主打芯片結(jié)構(gòu)、特點(diǎn)、性能都有所了解,但要真*實(shí)彈的用這個(gè)家伙干活,還得有更深入的嘗試和驗(yàn)證。對(duì)這些嘗試做些記錄,也許,是一次蠻有意思的嘗試。

今天先簡(jiǎn)單的沒主題的隨便扯談吧。首先,這家公司是提供了兩個(gè)系列的產(chǎn)品,其中一個(gè)系列工藝先進(jìn)些,據(jù)說性能好一些,只不過年初剛量產(chǎn),還不是主推產(chǎn)品,姑且不詳談,畢竟特權(quán)同學(xué)的DEMO板上的主角兒也不是它。另一個(gè)低端點(diǎn)的系列叫Astro,別小看它了,先羅列一下參數(shù)大家瞧瞧。

★ 硬核——可以跑到100MHz的8051硬核,標(biāo)準(zhǔn)外設(shè)IIC一個(gè)、SPI一個(gè)、USART兩個(gè)、定時(shí)器數(shù)個(gè)。

★ 1Mbit一次性可編程存儲(chǔ)(OTP)——加密的利器啊。

★ 1個(gè)PLL——3個(gè)可選輸出,相位可調(diào)。

★ 可選的內(nèi)部4Mbit FLASH。

★ 2個(gè)9Kbit可配置存儲(chǔ)器——雖然對(duì)于片內(nèi)存儲(chǔ)要求很高的特權(quán)同學(xué)有點(diǎn)“巧婦難為無(wú)米之炊”了,不過低端應(yīng)用犧牲一些“性能”還是可以接受的。

有這些東西還不算,最主要的還是它保持著傳統(tǒng)“中國(guó)特色”的“便宜”,基本上3個(gè)美金可以拿到有1024個(gè)LUT的器件了。若是要和當(dāng)前的Altera相關(guān)解決方案比比,那真得是蠻有競(jìng)爭(zhēng)力的。MAX II系列CPLD除了邏輯真得沒有別的用處了,而邏輯資源遜色不少的EPM570(EPM1270不說了)目前市場(chǎng)上估計(jì)是有缺貨的因素,居然賣到30好幾個(gè)RMB了。而如果選擇Cyclone系列最便宜的EP1C3好像也只要30多RMB,但是要跑個(gè)最經(jīng)濟(jì)的NIOS也有點(diǎn)困難。而且有個(gè)很有意思的現(xiàn)象,正規(guī)代理商會(huì)很無(wú)奈的告訴你這樣的老器件要30的數(shù)倍價(jià)格才能搞到,而外面的小商小販賣的就是30的準(zhǔn)“白菜價(jià)”(當(dāng)然不排除買到“散新貨”的可能)。而Astro卻連配置器件和外掛MCU的成本都省了,雖然它也是基于SRAM的結(jié)構(gòu)。(不行,越比發(fā)現(xiàn)這東西越好。先申明一下,這里不是推銷,只是比較,特權(quán)同學(xué)是用芯片的,不是賣芯片的。嘿嘿)

今天花了一上午把它們的開發(fā)工具Primace的Help過了一遍。再說個(gè)題外話,昨天到它們的上海辦事處,感覺上這般人對(duì)版本的管理不是很好,動(dòng)不動(dòng)來一個(gè)版本,讓我們當(dāng)時(shí)一個(gè)版本裝另一個(gè)版本卸的來回折騰好幾次才看到Primace的本來面目。還有那個(gè)USB下載線,MCU要一個(gè)JTAG,F(xiàn)PGA也要一個(gè)JTAG,如果能二合一的干活多好啊,就像咱的NIOS2。

FPGA開發(fā),確切的說硬件系統(tǒng)的開發(fā)都是有賴于Primace的,軟件是KEIL,它們提供了一套接口,用上去還算方便。這個(gè)Primace整個(gè)一ISE或者Quartus II的簡(jiǎn)化版,畢竟也是剛起步,勉強(qiáng)可以接受,怎么說咱當(dāng)年在ISE10大行其道的年代也有過被迫無(wú)奈“玩轉(zhuǎn)”ISE4的經(jīng)歷。

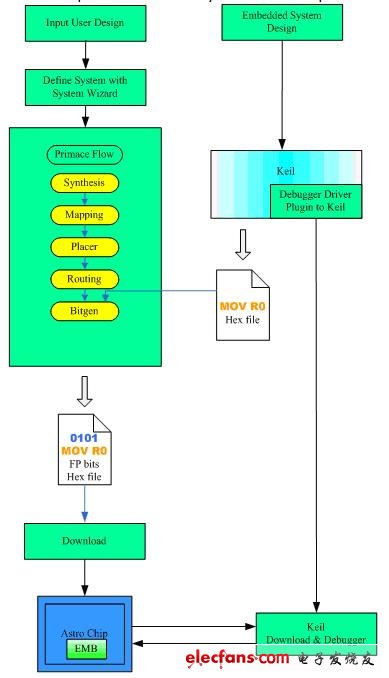

截個(gè)圖,如圖1,它們的開發(fā)流程也算是軟硬兼施,F(xiàn)PGA的流程很簡(jiǎn)化,看上去很“清爽”。最終把FPGA配置文件bitgen和KeilC的Hex一起在軟件里生成個(gè)新文件下載就行。

圖1

開發(fā)工具真的很“簡(jiǎn)陋”。時(shí)序約束和分析特權(quán)同學(xué)還沒摸懂怎么回事,就那么兩三個(gè)GUI選項(xiàng),只能說是比Classic timing analyzer還Classic,這一點(diǎn)是特權(quán)同學(xué)最擔(dān)憂的;提供的板級(jí)調(diào)試手段也很有限,好像就一個(gè)稱為Signal monitor的家伙,沒有嘗試,就不妄下定論,好在本來它的邏輯資源也不多,調(diào)試起來有沒有在線手段也無(wú)關(guān)緊要。

51硬核性能測(cè)試

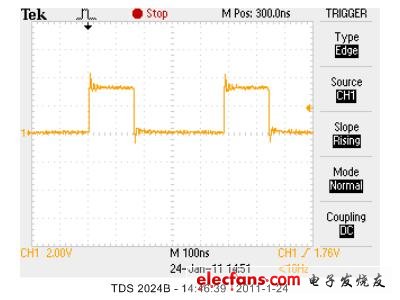

IO口速度測(cè)試,使用以下程序測(cè)試高電平脈寬。

while(1)

{

P0 = 0xf;

P0 = 0x0;

}

同等條件下與其他MCU比較:

?

|

工作頻率 |

高脈沖寬度 |

|

|

ASTRO 8051硬核 |

25MHz |

約1us |

|

ASTRO 8051硬核 |

50MHz |

約500ns |

|

ASTRO 8051硬核 |

100MHz |

約250ns |

|

STC89C516 |

11.0592MHz |

約2.16us |

|

NIOS II/e 32位軟核 |

25MHz |

約2.5us |

|

NIOS II/s 32位軟核 |

25MHz |

約160ns |

|

NIOS II/f 32位軟核 |

25MHz |

約160ns |

在兩次操作之間插入延時(shí)函數(shù),分別延時(shí)delay(1)、delay(2)、delay(3)、delay(4)。測(cè)試延時(shí)函數(shù)如下:

void delay(uchar cnt)

{

uchar i =0;

while(i 《 cnt)

{

i++;

}

}

由于delay()函數(shù)調(diào)用一次會(huì)有一些額外開銷(如賦初值等),所以我們通過不同延時(shí)值的實(shí)際延時(shí)差來看指令運(yùn)行的速度。換句話說,對(duì)前面的程序,可以通過每次delay()函數(shù)的差值來計(jì)算每多執(zhí)行一次i++和一次i

特權(quán)同學(xué)曾使用相同條件測(cè)試了51單片機(jī),通常11.0592MHz下工作的51單片機(jī)每多執(zhí)行一次i++和一次i

延時(shí)函數(shù)ASTRO 8051硬核NIOS II/s 32位軟核

50MHz100MHz25MHz50MHz

Delay(1)5.0us2.5us6.5us4us

Delay(2)6.6us3.3us9us6us

Delay(3)8.3us4.2us11.5us7.5us

Delay(4)9.9us5.0us14us9.5us

i++與i約1.63us約0.83us約2.5us約1.25us

簡(jiǎn)單的一些性能測(cè)試,發(fā)現(xiàn)這個(gè)51硬核還是有花頭的,至于穩(wěn)定性和可靠性上還需繼續(xù)驗(yàn)證和嘗試。當(dāng)然,本文的測(cè)試是使用了片內(nèi)的存儲(chǔ)器作為代碼和數(shù)據(jù)存儲(chǔ),實(shí)際速度性能和存儲(chǔ)器的性能關(guān)系非常大,是需要進(jìn)一步考核的項(xiàng)目。

?

存儲(chǔ)器

有幾點(diǎn)關(guān)于代碼和數(shù)據(jù)存儲(chǔ)區(qū)配置的一些疑問,麻煩解答一下:

問:代碼存儲(chǔ)器可以選擇OTP或者extension memory,一般在最終軟件定型后使用OTP沒有問題,而在調(diào)試過程中會(huì)選擇extension memory。extension memory里有三類:EMB、SRAM和Custom,通常代碼存儲(chǔ)器應(yīng)該是非易失存儲(chǔ)器,而你們這里列出來的EMB和SRAM都是下電易失的,這一點(diǎn)我不是很明白?難道說extension memory只是在KeilC處于debug模式時(shí)代碼運(yùn)行的存儲(chǔ)區(qū),而非代碼下電存儲(chǔ)的介質(zhì)?EMB只有1K(最大可以到2K),如果設(shè)置了這個(gè)代碼存儲(chǔ)器,是不是KEILC DEBUG時(shí)代碼不可以超過1K?

FAE:EMB和SRAM都是易失的,用EMB是最大可支持2KB的code空間,EMB初始化的信息與FPGA配置信息一起存儲(chǔ)在內(nèi)嵌SPI Flash中,上電自動(dòng)加載,用SRAM時(shí),需要使用我們提供的SRAMLoader工程,利用Astro重配置特性進(jìn)行加載。

問:與上面類似的疑問,關(guān)于數(shù)據(jù)存儲(chǔ)區(qū),兩個(gè)選項(xiàng),on-ship SRAM默認(rèn)勾選,這個(gè)沒有疑問。而FP應(yīng)該是內(nèi)部擴(kuò)展的4M Flash,應(yīng)該是非易失存儲(chǔ)器,數(shù)據(jù)存儲(chǔ)器通常沒有必要是非易失的吧?我認(rèn)為按照常規(guī),代碼存儲(chǔ)是非易失存儲(chǔ)器,數(shù)據(jù)存儲(chǔ)是易失存儲(chǔ)器,而你們的配置選項(xiàng)讓我有點(diǎn)糊涂。

FAE:Astro內(nèi)部為8051提供16KB專用SRAM,用作data空間。

問:另外,SPI燒錄應(yīng)該是將FPGA配置數(shù)據(jù)燒錄到4M FLASH中吧?而用Configuration Packer功能應(yīng)該是要將FPGA配置數(shù)據(jù)和軟件hex文件封裝成一個(gè)文件燒錄到4M flash中吧?我這么嘗試過好像下電后系統(tǒng)沒有跑起來,那么是不是在系統(tǒng)的存儲(chǔ)器配置中有所講究呢?

FAE:Configuration Packer可以讓Astro內(nèi)存儲(chǔ)多個(gè)配置文件,利用它可以在使用SRAM做code空間時(shí)打包SRAMLoader工程進(jìn)行上電自動(dòng)加載。附件中是關(guān)于Astro的幾個(gè)應(yīng)用文檔,您先看一下,寫的比較詳細(xì),相信對(duì)您理解Astro用法會(huì)很有幫助,謝謝!

昨天對(duì)Agate Logic負(fù)責(zé)硬件的FAE狂轟濫炸,對(duì)于其開發(fā)工具和器件的結(jié)構(gòu)都有更深入的了解和認(rèn)識(shí),上面的幾個(gè)問答只是關(guān)于51硬核的數(shù)據(jù)和代碼存儲(chǔ)器方面的,好一番追問之后,總算逼出了幾個(gè)像模像樣的文檔出來,消化后再做了一些實(shí)踐,然后有一點(diǎn)收獲和對(duì)后續(xù)項(xiàng)目在存儲(chǔ)器配置上的一些可行性的想法。另外,關(guān)于時(shí)序方面的一些疑問也得到了解答,不是很放心,也問出了一些真真確確的“問題”來,并且目前在用軟件版本的一些bug也被我問出來了,目前還需要等著廠商給我提供補(bǔ)丁,所以關(guān)于時(shí)序方面的博文只能暫緩進(jìn)行。

特權(quán)同學(xué)問題提得比較到位,但不是很有水準(zhǔn)。FAE回答得也不是很容易讓人明白,最后還是文檔給出了比較權(quán)威的解答。

在討論Astro系列芯片51硬核的軟件運(yùn)行模式之前,要先看看Astro系列芯片到底已經(jīng)提供了哪些片內(nèi)的存儲(chǔ)資源,不看不要緊,一看嚇一跳——可謂品種齊全,滿足各類需求。

1. 總共1Mbit的OTP型存儲(chǔ)區(qū),其中64KB用于FPGA的配置數(shù)據(jù)存儲(chǔ),另64KB用于51硬核的最終代碼存儲(chǔ)器。

2. 4Mbit(512KB)的FPGA和8051公用的SPI Flash。

3. 2塊9Kbit的可配置雙端口EMB。

4. 16KB的51硬核專用數(shù)據(jù)存儲(chǔ)器。

Astro系列芯片51硬核的軟件主要運(yùn)行模式:

小模式:

不外掛存儲(chǔ)器,使用芯片現(xiàn)有資源,F(xiàn)PGA配置數(shù)據(jù)和8051代碼(小于2KB)存儲(chǔ)于SPI Flash中。系統(tǒng)上電后,F(xiàn)PGA配置數(shù)據(jù)先從SPI Flash中導(dǎo)出并配置FPGA,也包括EMB的初始化數(shù)據(jù)(即軟件代碼從SPI FLASH搬運(yùn)到EMB中);完成后8051代碼直接從EMB中開始運(yùn)行。

內(nèi)嵌8051在無(wú)等待周期的狀態(tài)下,最快時(shí)鐘頻率可到70MHz,性能到47MIPS的性能。主要用于8051代碼較少時(shí),調(diào)試生產(chǎn)兩便,成本也比較低。

手記二中的測(cè)試就是基于該模式,性能還算可以。

調(diào)試模式:

外掛SRAM存儲(chǔ)器,F(xiàn)P Bootloader配置數(shù)據(jù)、FPGA用戶程序配置數(shù)據(jù)和8051用戶代碼分段存儲(chǔ)于SPI Flash中。系統(tǒng)上電先從SPI Flash中導(dǎo)出FP BootLoder配置數(shù)據(jù)(內(nèi)含Loader部分)。配置FP包括EMB的初始化數(shù)據(jù),完成后SRAM Loader程序?qū)徇\(yùn)8051用戶代碼到外掛SRAM中;之后再?gòu)腟PI Flash中導(dǎo)入FP用戶程序并重新配置FP,8051代碼在外掛SRAM中開始運(yùn)行。

內(nèi)嵌8051在無(wú)等待周期的狀態(tài)下,最快時(shí)鐘頻率可到35MHz,性能到23MIPS的性能。此模式主要用于8051代碼超過2KB調(diào)試時(shí)用。當(dāng)然也可用于生產(chǎn)。請(qǐng)注意外掛SRAM將增加成本。

這種模式由于不太可能使用,所以特權(quán)同學(xué)不過多研究,但這也是嵌入式系統(tǒng)中比較常見的一種BootLoder方式。

最終生產(chǎn)模式:

不外掛存儲(chǔ)器,8051代碼存儲(chǔ)于OTP存儲(chǔ)器中,F(xiàn)P配置數(shù)據(jù)存于OTP或SPI FLASH中。因?yàn)镺TP存儲(chǔ)器是一次性的,所以不能用于調(diào)試階段。一般產(chǎn)品最終定型后再使用OTP存儲(chǔ)器可以獲得最優(yōu)的性能和最低的成本。

而當(dāng)采用OTP 作為8051 代碼內(nèi)存,最高時(shí)鐘頻率可達(dá)100MHz。較理想的方法是用鎖相環(huán)PLL來產(chǎn)生8051 時(shí)鐘。CKCON SFR的低4位用來控制數(shù)據(jù)Memory 的等待周期。如果8051時(shí)鐘頻率高于45MHz,最好將value設(shè)置為大于等于2,以防止時(shí)鐘太快,數(shù)據(jù)還沒準(zhǔn)備好。

也就是說,OTP方式可以達(dá)到51硬核代碼運(yùn)行的最佳性能,甚至于性能的速度瓶頸已經(jīng)不是代碼存取,而是數(shù)據(jù)存取。

以上三種模式是比較推薦的,但是特權(quán)同學(xué)從實(shí)際工程需要來考慮,簡(jiǎn)單的說,需要一種調(diào)試模式和一種生產(chǎn)模式。生產(chǎn)模式無(wú)可厚非的選擇OTP燒錄,而調(diào)試模式有點(diǎn)棘手,如果選擇小模式,代碼運(yùn)行量太小,頂多不過2K,基本干不了什么事。而選擇外擴(kuò)SRAM,有限的IO資源不會(huì)允許的。所以,有點(diǎn)苦惱,但是還好,還有一種最次的選擇——性能低下的第四種模式。

?

當(dāng)8051的性能低于1.4MIPS時(shí),可用spi flash作為8051的代碼存儲(chǔ)器。此模式的運(yùn)行環(huán)境如下:

1. 選用片內(nèi) SPI FLASH;

2. FPGA的配置數(shù)據(jù)和8051代碼存放在同一個(gè)SPI FLASH 里;

3. 8051 與SPI FLASH 接口大約需要90 個(gè)LE cells;

4. 8051 的內(nèi)核時(shí)鐘最快為30MHz 左右, 8051 最快運(yùn)行性能大約為1.4MIPS;

5. 順序取指需要 8 個(gè)時(shí)鐘周期,跳轉(zhuǎn)取指需要40 個(gè)周期;

在嘗試SPI FLASH模式的時(shí)候,遇到了比較有意思的事。特權(quán)同學(xué)根據(jù)實(shí)例做SPI FLASH的運(yùn)行測(cè)試,結(jié)果搞不定,也找不到相關(guān)的IP核。于是求問FAE,F(xiàn)AE直接告知這個(gè)IP核還沒有集成到工具中,然后把源代碼都發(fā)過來了。呵呵,雖然工具不完善,不過服務(wù)倒是很周到。

由于基于SPI FLASH的模式是在51硬核與SPI FLASH之間使用FPGA邏輯搭建了一個(gè)FLASH讀取的模塊。所以經(jīng)過測(cè)試,確實(shí)這個(gè)FLASH讀取控制的邏輯模塊頻率不能太高,過高FLASH就要**了,理論值是30M,而特權(quán)同學(xué)用了25M。然后使用上一篇手記同樣的方法改變硬核的頻率進(jìn)行測(cè)試。

?

|

延時(shí)函數(shù) |

EMB模式 |

SPI FLASH模式 |

||

|

50MHz |

100MHz |

50MHz |

100MHz |

|

|

Delay(1) |

5.0us |

2.5us |

20us |

20us |

|

Delay(2) |

6.6us |

3.3us |

27.5us |

27.5us |

|

Delay(3) |

8.3us |

4.2us |

35us |

35us |

|

Delay(4) |

9.9us |

5.0us |

42.5us |

42.5us |

|

i++與i |

約1.63us |

約0.83us |

約7.5us |

約7.5us |

結(jié)果證明,51硬核的頻率受制于指令的讀取速度,那么在SPI FLASH模式下速度性能確實(shí)大打折扣。

時(shí)序工具

關(guān)于時(shí)序工具的一些FAE解答:

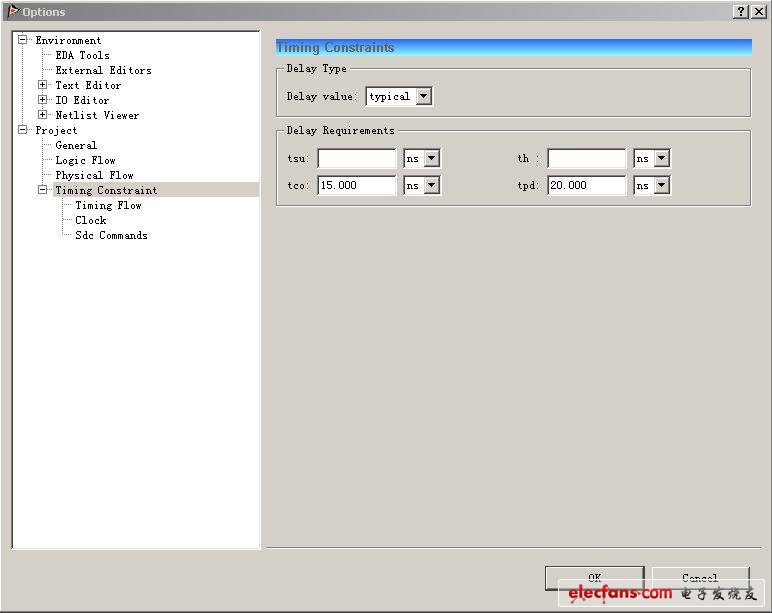

問:你們的工具是否只提供所有輸入輸出管腳完全一致的時(shí)序約束?如tsu,th,tco,tpd的約束?如果不同管腳可以有不 同約束值,如何設(shè)置?

FAE:我們的工具提供的是時(shí)序分析功能,尚未提供時(shí)序約束功能,也就是說可以根據(jù)您輸入的值作為參考,計(jì)算出當(dāng)前實(shí)現(xiàn)的各種時(shí)序信息與參考值的差距,但并不會(huì)根據(jù)輸入的值去做優(yōu)化,所以也就不存在對(duì)不同管腳分別設(shè)置約束的功能了。

問:tco是指reg2pin的延時(shí)約束,tpd是指pin2pin的約束。而輸入管腳約束tsu和th值,具體含義我不是很 明白?比如說我希望輸入管腳的pin2reg延時(shí)為0-10ns,那么tsu和th如何設(shè)置?

FAE:tsu就可以理解為pin2reg的延時(shí),它是信號(hào)從pin到FPGA內(nèi)部第一個(gè)reg相對(duì)于這個(gè)reg的clock的setup time,而th就是相對(duì)這個(gè)clock的hold time,th一般不會(huì)有問題,需要關(guān)注的是tsu。

問:我嘗試用GUI做了一些時(shí)序約束,然后每次做時(shí)序分析都報(bào)錯(cuò):Error: T2000: (ice_run_sta) Run sta failed. 這是什么問題?

FAE:您的這個(gè)錯(cuò)誤一般是sta設(shè)置上有什么問題,得具體分析工程。

今天終于拿到了最新3.2版本的軟件,安裝后,進(jìn)行編譯,長(zhǎng)達(dá)近10分鐘的placement讓我眉頭緊皺。后來從FAE處得知我拿到的是還未release出來的中間版本,有問題在所難免。不說這個(gè),回到主題上來,其實(shí)總感覺有些遺憾。FAE在之前的回答其實(shí)已經(jīng)預(yù)示著這個(gè)國(guó)產(chǎn)FPGA與特權(quán)同學(xué)緣分已到盡頭。

WHY?他們提供的時(shí)序分析工具根本算不上真正的時(shí)序分析工具,或者這么說,這個(gè)所謂的時(shí)序分析工具只能提供分析,而無(wú)法進(jìn)行時(shí)序的約束和優(yōu)化。即便他們的工程設(shè)置中也提供了如圖1的恐怕可以稱得上是最簡(jiǎn)單的“時(shí)序約束”,但這個(gè)所謂的“時(shí)序約束”其實(shí)并沒有任何“約束”的作用。安裝“官方”的說法,它不能夠?qū)C合乃至布局布線起到任何影響,而不過是給報(bào)告中的路徑劃了一條水平線,報(bào)告中確實(shí)能夠體現(xiàn)出水平線上或下的狀態(tài)。

圖1

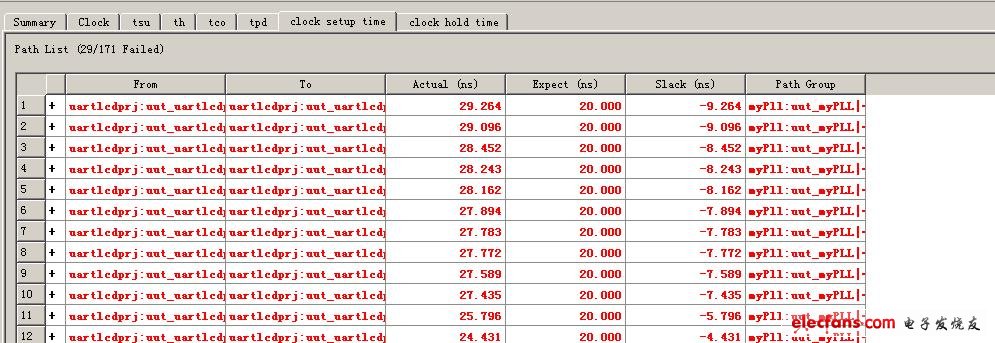

如圖2所示,很無(wú)奈的只是移植了一個(gè)SDRAM控制器外加一些其它邏輯,占去了總共1000個(gè)LE中80%的資源,然后只是約束了一個(gè)50MHz的工作時(shí)鐘,結(jié)果出來了20條false路徑。即便嘗試去試試用提供的僅有幾個(gè)對(duì)mapping或palcement&routing設(shè)置的優(yōu)化,結(jié)果換來了更多的false。FAE也坦言,目前只能做些簡(jiǎn)單的邏輯,跑個(gè)SDRAM等稍復(fù)雜的邏輯也就只能跑個(gè)二三十兆的樣子。

圖2

幾天的試用,雖然以國(guó)產(chǎn)FPGA的性能問題而告夭折。雖然還顯稚嫩的開發(fā)工具、差強(qiáng)人意的器件性能多少讓人有些失望,但至少?gòu)哪撤N程度上讓特權(quán)同學(xué)改變了對(duì)國(guó)產(chǎn)的一些偏見。其實(shí),如果Agate Logic能夠持續(xù)這種開發(fā)熱情,不斷的改進(jìn),假以時(shí)日,相信他們會(huì)成為“中國(guó)的Altera”、“中國(guó)的Xilinx”。

外擴(kuò)SFR使用

本以為這個(gè)國(guó)產(chǎn)FPGA的就此夭折,沒想到權(quán)衡之后,在性能打些折扣的情況下還是重新?lián)炱饋砹恕膭偨佑|這個(gè)器件的時(shí)候特權(quán)同學(xué)就很關(guān)心它的硬核可擴(kuò)展性,Avalone接口用上手了,當(dāng)然很希望這個(gè)51硬核也能夠提供類似的強(qiáng)大擴(kuò)展接口。不過話說回來,畢竟是個(gè)8位的核,再?gòu)?qiáng)大也不到哪去,但在花了點(diǎn)心思琢磨了這個(gè)小玩意的擴(kuò)展方式后,多少覺得還是有點(diǎn)花頭的。

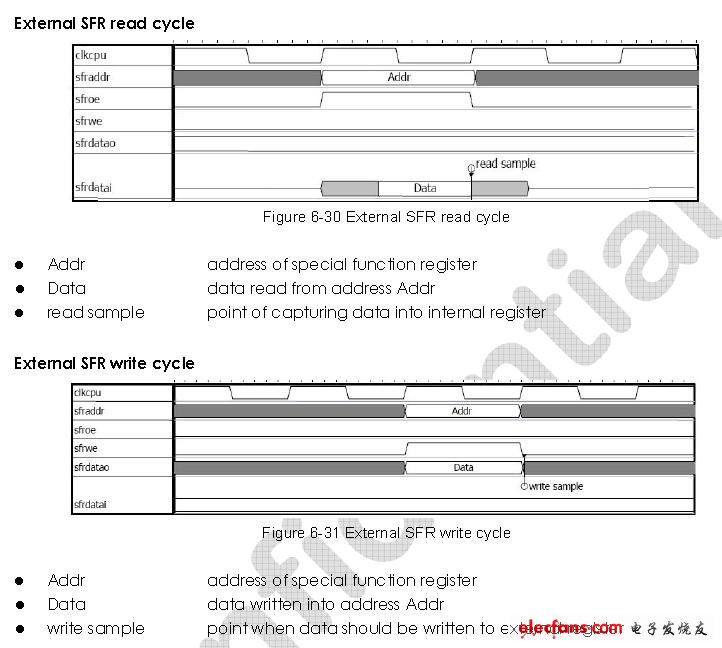

SFR,即特殊功能寄存器。SFR是8051單片機(jī)內(nèi)部用于訪問控制各種片上集成外設(shè)的主要寄存器,如常見的IO口(P0/P1/P2/P3)讀寫、IO中斷配置、定時(shí)器配置、串口外設(shè)等。因此,對(duì)一般用戶而言,玩轉(zhuǎn)8051就是玩轉(zhuǎn)SFR的過程。一般的單芯片8051單片機(jī)的SFR接口不對(duì)外開放,除了部分寄存器內(nèi)部使用外,余下地址空間保留。而Astro器件的這顆8051硬核將空置的SFR地址空間開放給用戶,提供了專門的對(duì)外接口時(shí)序。

特權(quán)同學(xué)將關(guān)于Astro器件SFR相關(guān)的特性整理如下:

● 可尋址空間0x80~0xff。

● 部分地址空間已被8051內(nèi)部使用。

● 16個(gè)地址空間(能被8整除的地址如0x80、0x88、0x90、…0xf8等)可位尋址。

● 最多支持49個(gè)8051核外可用SFRs,除核內(nèi)已占用的地址,余下地址空間均為用戶可用的核外SFRs。

● 外部SFR接口含有等待狀態(tài)寄存器(主要由sfack信號(hào)控制實(shí)現(xiàn)),允許8051內(nèi)核與較慢的外設(shè)連接。

● 外部SFR讀寫時(shí)序如圖3所示。

圖3

為了簡(jiǎn)單的評(píng)估8051硬核的SFR擴(kuò)展功能的性能,特權(quán)同學(xué)做了一些測(cè)試。

測(cè)試1:SFR可用性測(cè)試

簡(jiǎn)單的用邏輯模擬一個(gè)SFR可訪問的外部寄存器,該寄存器只使用低四位,對(duì)應(yīng)控制4個(gè)外部LED的亮暗。以此驗(yàn)證核外SFR的可用性。

對(duì)于8051硬核而言,如果開啟核外SFR功能,提供了如下接口(與前面給出的波形圖對(duì)應(yīng)):

// External Special Function Registers interface

output[7:0] sfrdatao; //8051寫數(shù)據(jù)

output [6:0] sfraddr; //8051訪問地址

input [7:0] sfrdatai; //8051讀數(shù)據(jù)

output sfrwe; //8051寫SFR使能信號(hào),高電平有效

output sfroe; //8051讀SFR使能信號(hào),高電平有效

SFR從機(jī)的邏輯接口代碼如下:

reg[3:0] ledr; //LED指示燈對(duì)應(yīng)的SFR

always @(posedge clk_50m or negedge rst_n) begin

if(!rst_n) ledr 《= 4‘h0;

else if(sfrwe && (sfraddr == 7’h78)) ledr 《= sfrdatao[3:0];

//8051往地址為0xf8的SFR寫數(shù)據(jù),將數(shù)據(jù)鎖存到ledr寄存器中

end

assign {led3,led2,led1,led0} = ledr;

軟件編程時(shí),需要在工程中做一個(gè)新的sfr定義:

//自定義SFR

sfr LED = 0xf8; //低4bit控制LED亮暗

編寫函數(shù)實(shí)現(xiàn)SFR控制的流水燈:

void main(void)

{

while(1)

{

LED = 0x1;

delay(500);

LED = 0x2;

delay(500);

LED = 0x4;

delay(500);

LED = 0x8;

delay(500);

}

}

實(shí)驗(yàn)結(jié)果證明功能可行,達(dá)到預(yù)期。這個(gè)SFR功能的使用還是蠻簡(jiǎn)單的。

為了驗(yàn)證寫功能,基本思路是想針對(duì)板載4個(gè)按鍵做一個(gè)SFR寄存器,專供8051內(nèi)核讀取當(dāng)前按鍵值,然后把該值分別賦給4個(gè)LED(在前面測(cè)試的基礎(chǔ)上執(zhí)行)。添加的邏輯代碼:

reg[3:0] keyr;

always @(posedge clk_50m or negedge rst_n) begin

if(!rst_n) keyr 《= 4‘hz;

else if(sfroe && (sfraddr == 7’h79)) keyr 《= {key4,key3,key2,key1}; //8051從地址為0xf9的SFR讀出數(shù)據(jù)

else keyr 《= 4‘hz;

end

assign sfrdatai = keyr;

讀時(shí)序這個(gè)時(shí)鐘clkcpu應(yīng)該是8051工作的指令時(shí)鐘,即8051外部輸入時(shí)鐘的12分頻。這個(gè)時(shí)序圖好像不太準(zhǔn)確,實(shí)際讀或?qū)戇x通高脈沖不會(huì)保持一整個(gè)指令周期。特權(quán)同學(xué)測(cè)試下來發(fā)現(xiàn)用50MHz時(shí)鐘做從接口,早一個(gè)時(shí)鐘或是晚一個(gè)時(shí)鐘周期送數(shù)據(jù)都無(wú)法使8051讀走數(shù)據(jù),只有上面給出的代碼下時(shí)鐘送數(shù)據(jù)才能正常保證8051鎖存數(shù)據(jù)。也就是說,數(shù)據(jù)必須在讀選通期間都保持穩(wěn)定,早一個(gè)時(shí)鐘周期撤銷或是晚一個(gè)時(shí)鐘周期撤銷都不行。因此,為了延長(zhǎng)數(shù)據(jù)有效長(zhǎng)度,改進(jìn)如下:

reg[3:0] keyr;

reg keyrden;

always @(posedge clk_50m or negedge rst_n) begin

if(!rst_n) keyrden 《= 1’b0;

else if(sfroe && (sfraddr == 7‘h79)) keyrden 《= 1’b1;

else keyrden 《= 1‘b0;

end

always @(posedge clk_50m or negedge rst_n) begin

if(!rst_n) keyr 《= 4’hz;

else if(keyrden || (sfroe && (sfraddr == 7‘h79))) keyr 《= {key4,key3,key2,key1}; //8051從地址為0xf9的SFR讀出數(shù)據(jù)

else keyr 《= 4’hz;

end

assign sfrdatai = keyr;

軟件編程也很簡(jiǎn)單:

//自定義SFR

sfr LED = 0xf8; //低4bit控制LED亮暗

sfr KEY = 0xf9; //低4bit對(duì)應(yīng)當(dāng)前按鍵值

void main(void)

{

while(1)

{

LED = KEY;

}

}

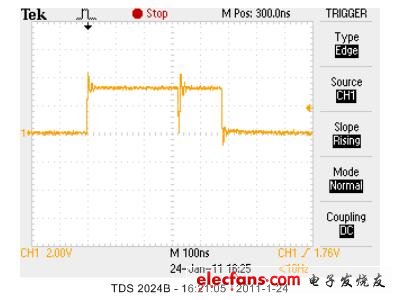

測(cè)試2:SFR性能測(cè)試

與《國(guó)產(chǎn)FPGA試用手記二(51硬核性能測(cè)試)》做了類似的測(cè)試,驗(yàn)證LED寄存器拉高拉低的速度,和之前的結(jié)果一樣。也就是說,核外的SFR在不使用等待功能的情況下與核內(nèi)SFR的操作速度是一樣的。

測(cè)試3:SFR等待功能驗(yàn)證

在50MHz的clkcpu下,沒有等待時(shí)(即assign sfrack = 1‘b1;),不斷的對(duì)核外SFR寫使能情況可以得到如圖2所示的使能信號(hào)波形。兩次上升沿之間240ns即一個(gè)指令周期(12個(gè)50MHz時(shí)鐘周期),而讀使能信號(hào)有效高脈沖為160ns,即8個(gè)時(shí)鐘周期。

圖4

Datasheet中標(biāo)明的sfrack信號(hào)其實(shí)無(wú)法直接從例化的51硬核中找到接口,于是特權(quán)同學(xué)干脆直接生成的IP核例化文件中把它手動(dòng)引出來了,在自定義邏輯中對(duì)這個(gè)信號(hào)做了一些測(cè)試,也發(fā)現(xiàn)了該信號(hào)的使用方法。

代碼如下:

reg[7:0] sfcnt; //延時(shí)等待計(jì)數(shù)器,以50MHz為時(shí)鐘單位計(jì)數(shù)

wire sfrack; //SFR 讀寫等待信號(hào)

always @(posedge clk_50m or negedge rst_n) begin

if(!rst_n) sfcnt 《= 8’d0;

else if(sfrwe) sfcnt 《= sfcnt+1‘b1;

else sfcnt 《= 8’d0;

end

assign sfrack = (sfcnt == 0) | (sfcnt 》 8‘d23);

//等待n個(gè)指令周期,則sftcnt要大于(n*12-1)

該代碼實(shí)現(xiàn)在sfrwe即SFR寄存器寫選通信號(hào)到來后,用計(jì)數(shù)器sfcnt進(jìn)行計(jì)數(shù),然后相應(yīng)的對(duì)需要延時(shí)等待的8051指令周期數(shù)通過控制sfrack為低電平實(shí)現(xiàn)。

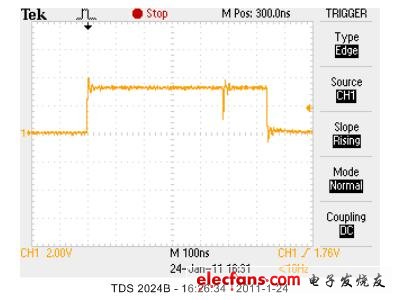

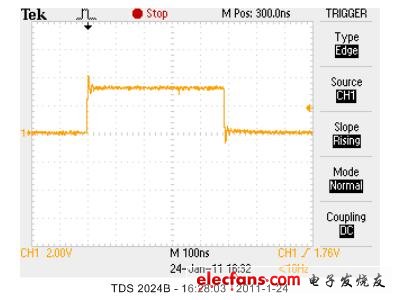

分別設(shè)置了sfcnt》8’d16、sfcnt》8’d24、sfcnt》8’d23得到sfrwe的波形如圖5、圖6、圖7所示。

圖5

圖6

圖7

由此可見,這里延時(shí)等待的時(shí)間必須剛好是指令周期。即系統(tǒng)指令周期為20ns*12=240ns,那么我們外部計(jì)數(shù)周期也是20ns的情況下,一般取等待時(shí)鐘數(shù)為12的倍數(shù)即可。否則就會(huì)出現(xiàn)圖3和圖4的“毛刺”,其中原因不好妄下定論,恐怕和器件本身的內(nèi)部處理機(jī)制有關(guān)。

兩個(gè)調(diào)試中遇到的小問題,引以為戒。

1. 畫板子的時(shí)候由于沒注意結(jié)構(gòu)上的固定邊框,不小心把一個(gè)旁路電容放在邊界上。在外部鐵殼將液晶屏固定到電路板上后,出現(xiàn)的癥狀很有意思。兩個(gè)不同的屋子(A和B),同樣的電源輸入,咱的板子在A屋子若是用手觸碰鐵殼,液晶屏就閃一下;而在B屋子就不會(huì)出現(xiàn)同樣的問題。問題出現(xiàn)后,做了一些驗(yàn)證和測(cè)試,初步將問題定位在液晶屏的外殼和鐵殼的接地。當(dāng)然,回到開始提到的旁路電容,它隨算不上是罪魁禍?zhǔn)祝緛龛F殼以及液晶屏外殼(這二者應(yīng)該是固定在一起的)與電路板的地沒有連在一起,而這里的電容裸露的焊盤導(dǎo)致了二者連接在一起了。A屋子的供電拖線板的地和大地(由人手來傳導(dǎo))沒有連在一起,而B屋子的供電拖線板的地和大地本來就是連在一起的。因此,結(jié)論也就浮出水面:在A屋子,大地和電路板的地(也就是鐵殼的地)原本沒有共在一起,當(dāng)人手觸碰鐵殼的時(shí)候,兩個(gè)地連在一起了,因此導(dǎo)致了液晶屏顯示的閃爍現(xiàn)象;B屋子相應(yīng)就不存在此問題,因?yàn)榇蟮睾丸F殼的地原本就是共在一起的,人手觸碰鐵殼也就不會(huì)有什么問題了。

2. 這是關(guān)于存儲(chǔ)器的有效管腳被懸空引發(fā)的問題。從大學(xué)里上《數(shù)字電路》開始,就聽說數(shù)字芯片不使用的管腳不可以懸空,要么接GND要么接VCC。而在實(shí)際工程中,咱可基本是“中規(guī)中矩”的照此設(shè)計(jì),然而有些問題的出現(xiàn)大都不是設(shè)計(jì)者可以“算計(jì)”到的。先看看出現(xiàn)的問題:如果不小心用手觸碰到了存儲(chǔ)器,那么液晶屏就會(huì)出現(xiàn)花屏閃爍等現(xiàn)象。特權(quán)同學(xué)的第一感覺是虛焊了,但是多次重新加錫焊過后,問題還是時(shí)不時(shí)的出現(xiàn)。最終看看存儲(chǔ)器的型號(hào),隱約感覺到了問題出在這上面:由于原本128K的存儲(chǔ)器由于庫(kù)存問題被兼容型號(hào)的256K替代了,因此就存在一條地址線在電路中處于懸空狀態(tài)。意識(shí)到這個(gè)問題后,特權(quán)同學(xué)試著用手(這是一個(gè)不好的習(xí)慣,人手的靜電很可能引發(fā)新的“血案”)靠近那個(gè)懸空管腳,根本無(wú)需接觸到,立馬現(xiàn)象復(fù)現(xiàn)。問題的解決也很簡(jiǎn)單,要么接GND要么接VCC,還有一個(gè)更簡(jiǎn)單的辦法是把這個(gè)懸空管腳和旁邊的地址線短路,總之讓他處于一個(gè)可控的固定狀態(tài)問題就能解決。

接著上圖,國(guó)產(chǎn)FPGA其實(shí)也很“給力”。當(dāng)然,這和特權(quán)同學(xué)在性能與功能折中的情況下“絞盡腦汁”最大限度的“揚(yáng)長(zhǎng)避短”不無(wú)關(guān)系,也難怪芯片銷售商看到效果后樂得合不攏嘴。但是后期是否能夠經(jīng)受住新的考驗(yàn)可就要看看它自己是否有真本事了。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論