?

以前很多人認為,半導體器件只會在太空應用中受到輻射的影響,但是隨著半導體工藝的進步,很多地面的應用也會受到輻射的影響。今天,我們會介紹不同的輻射效應和對FPGA的影響,比較不同的FPGA的耐輻射性。

輻射的影響

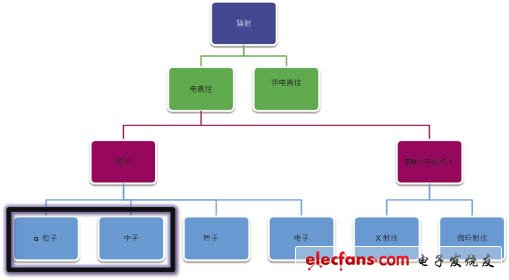

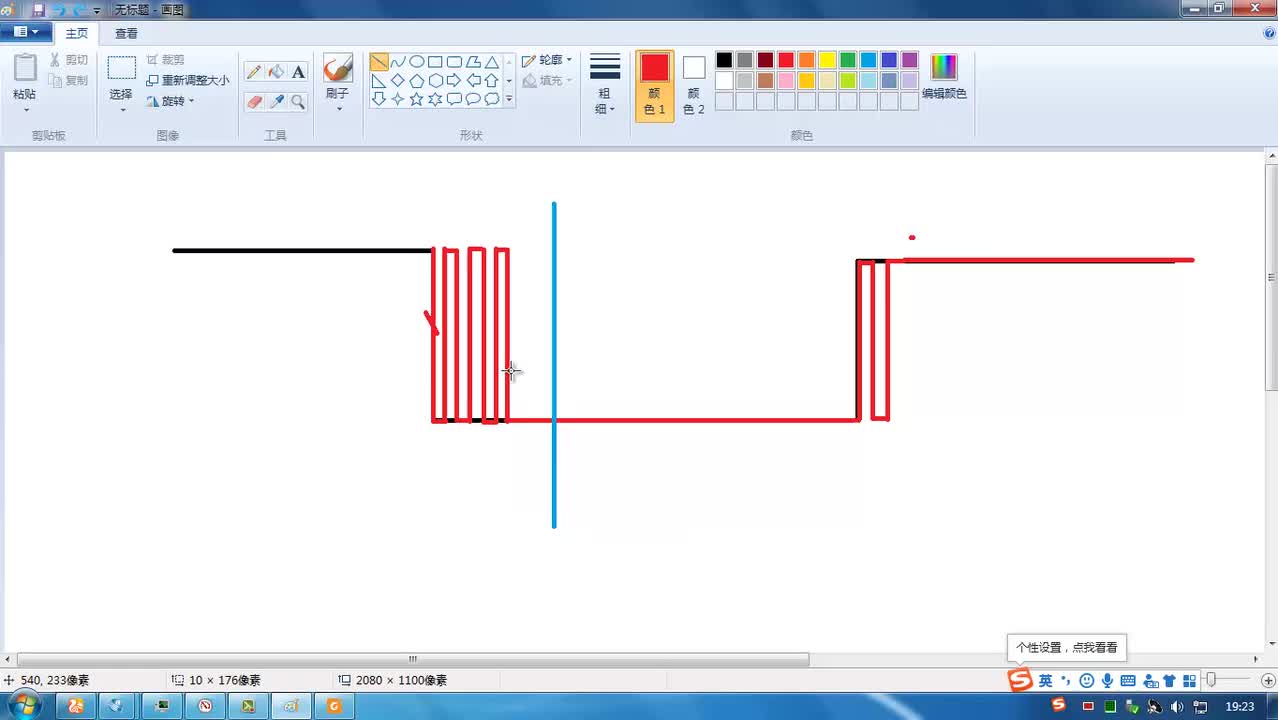

按照是否能造成原子或者分子的電子脫離,輻射主要分為電離性和非電離性兩大類,如圖1所示。高能粒子或者電磁波包括X射線和γ射線都能夠產生電離的作用。半導體器件受電離性的輻射影響較大,日常應用中以粒子引起的電離性輻射最常見,而其中,以α粒子和中子的影響力較大。

?

圖1 輻射分類

對于太空和地面的應用而言,輻射效應可以分為兩大類,單事件效應(SEE)和總離子劑量/總劑量(TID)。在對地面的應用中,單事件效應比較普遍,SEE是高能帶電粒子在器件的靈敏區內產生大量帶電粒子的現象,SEE的種類很多,尤其以單事件閉鎖(SEL)和單事件/粒子翻轉(SEU)最難處理。當輻射在器件內造成一定程度的離子化的時候,導通大電流,發生單事件閉鎖現象,即使在最輕微的情況下,這種閉鎖現象仍會引起芯片循環上電,嚴重情況下芯片會永久損壞。但是,值得高興的是,已經可以使用芯片設計和工藝技術來減少單事件閉鎖發生的幾率。

一般電子應用中遇到的輻射問題來自于天然輻射,包括由太陽和宇宙的影響造成的因素造成。星系宇宙射線(GCR)是指來自于太空的α粒子、重離子和質子,而太陽主要發射電子、質子和重離子。中子的體積非常小,能夠輕易穿過大氣層,甚至能穿透整個地球,而且由于其不帶電荷,能逃過地球的輻射帶陷阱,因此到達地面和半導體產生作用的高能粒子以中子為主。

不同的環境對產生輻射的影響是不同得,輻射通量隨著高度的上升成指數增加,在海拔330km時,是太空電子應用的所在地,海拔50km是軍用飛機所能達到的高度,這里中子和其他粒子的強度都比較高,隨著高度繼續降低,輻射的通量隨著降低,是商業飛機的應用高度。

地球上的中子來源分為天然來源和人造來源。天然來源是來自宇宙射線與大氣中的氧和氮的相互作用,中子是太陽耀斑的副產品。人造來源包括核武器、核反應堆、醫療設備等。

輻射對FPGA器件影響

單粒子翻轉 (SEU),是指當一個重離子撞擊一個電路節點,沉積足夠的電荷使該節點的狀態改變。SEU 不僅限于太空應用,也會發生在地面的應用,如醫療、航空電子、汽車、網絡和基礎設施。

軟錯誤 (soft error)指存儲器單元或寄存器中可以校正的翻轉,數據被改變,但存儲器單元沒有損壞,一般影響單一比特位,偶爾影響超過一個比特位。

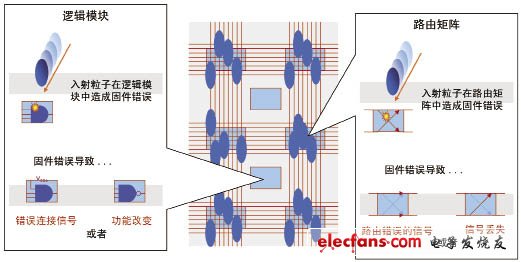

固件錯誤 (firm error)指SRAM FPGA 中配置存儲器的翻轉,它被稱為“固件”,是因為錯誤會一直存在,直到SRAM FPGA重新上電或啟動才能清除。固件錯誤多數導致功能故障,后果比軟錯誤嚴重得多,它能夠引起FPGA失效以及整個系統的故障。

FPGA 器件中的輻射影響分為兩大類:數據影響(軟錯誤)和配置影響(固件錯誤)。醫療等地面應用中的兩個重要輻射源則包括中子和α粒子。

數據影響(軟錯誤)數據影響(軟錯誤)包括觸發器、存儲器單元、組合邏輯單元中的單比特位翻轉。如果能夠校正錯誤,則問題不嚴重,非關鍵性數據可請求重新發送,對于關鍵性數據可使用 EDAC/FEC、奇偶校驗冗余手段來達到保護的目的。

配置影響(固件錯誤)是指FPGA 配置元件的單比特位翻轉,它可以引起 FPGA 故障,也可以影響數百萬比特位的數據,甚至可以引發整個系統的故障。

?

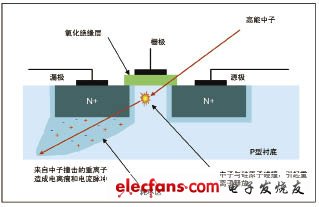

圖2 中子對集成電路的影響

中子對集成電路的影響如圖2所示,包括:

?中子可能撞擊硅原子,放出重離子

?會改變存儲器單元和觸發器中的數據

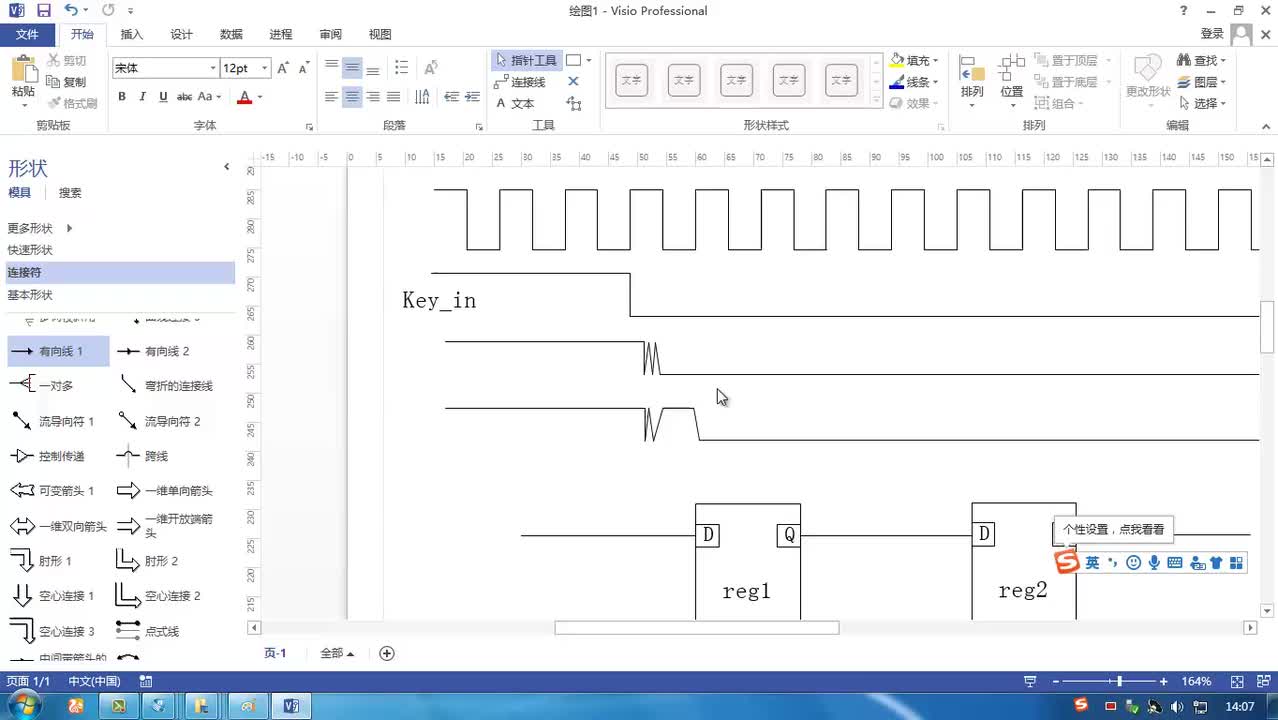

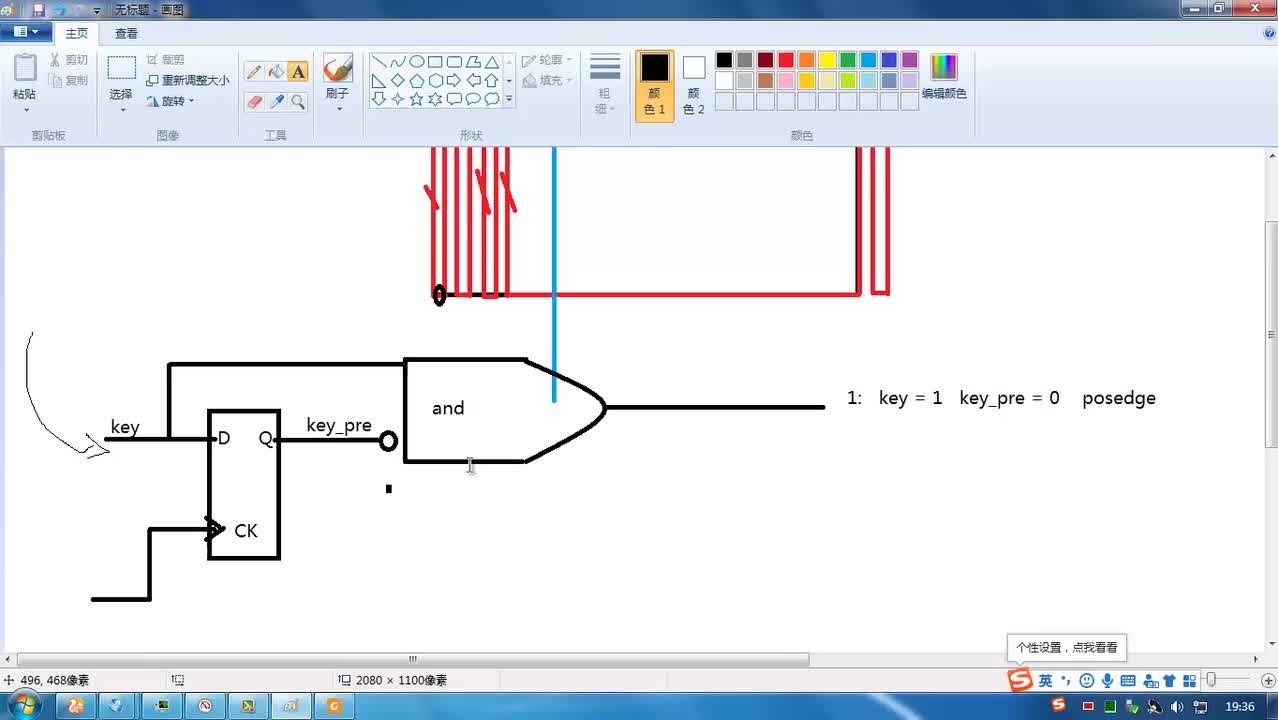

輻射如何引發 SRAM FPGA 失效,引起SRAM FPGA 中的配置翻轉呢?如圖3所示。

?

圖3 輻射引發SRAM FPGA失效

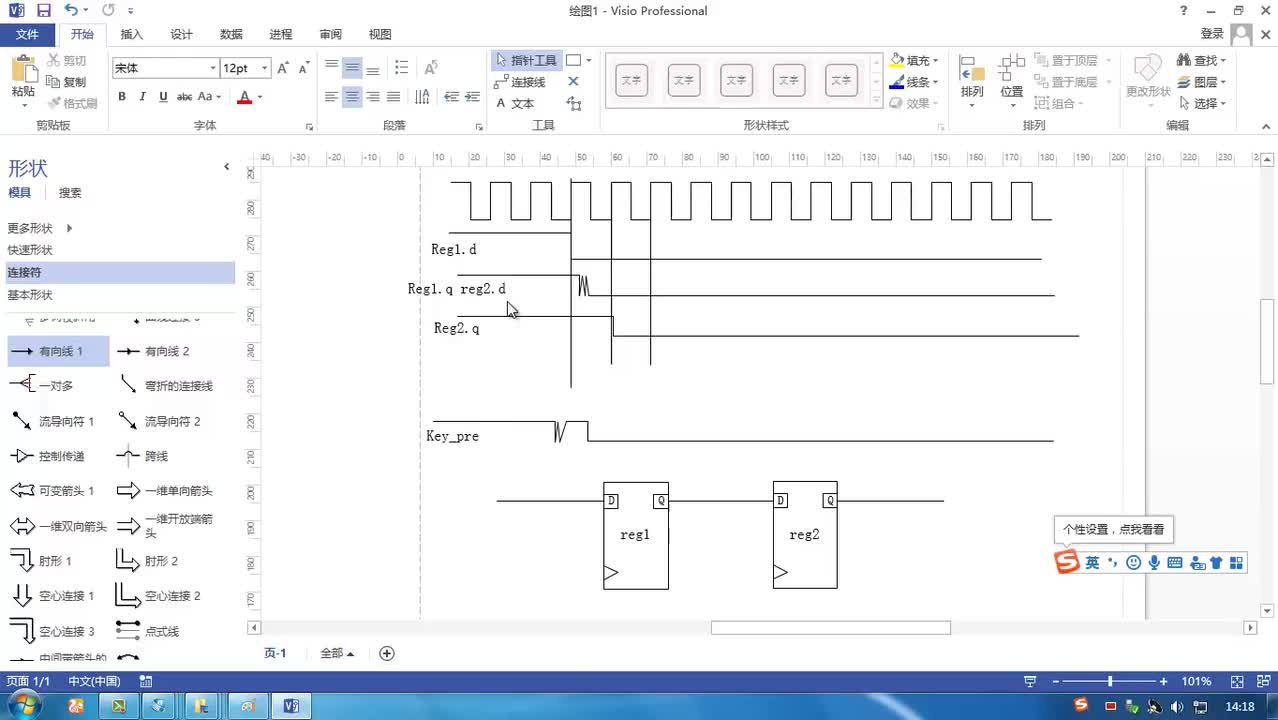

非易失性FPGA

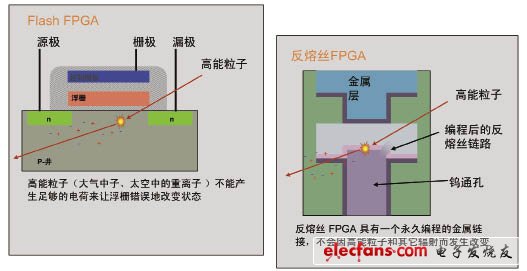

Microsemi非易失性 FPGA 具有配置翻轉免疫能力。分為Flash FPGA和反熔絲FPGA,如圖4所示。

?

圖4 Flash FPGA和反熔絲FPGA

Flash FPGA,高能粒子(大氣中子、太空中的重離子 )不能產生足夠的電荷來讓浮柵錯誤地改變狀態。

反熔絲FPGA,反熔絲 FPGA 具有一個永久編程的金屬鏈接,不會因高能粒子和其他輻射而發生改變。

中子導致的數據故障(軟錯誤),Flash FPGA 和 SRAM FPGA 的數據翻轉率相似,這是基于第三方機構 iROC Technologies 所做的分析。

翻轉率是以每一億小時,每百萬個觸發器計算,每個故障等于一個D型觸發器數據的翻轉,可以用EDAC/FEC、奇偶校驗、CRC等方法輕易校正。

中子導致的配置故障(固件錯誤),每個故障等于FPGA器件的失效,而越先進的工藝通常故障率越高。

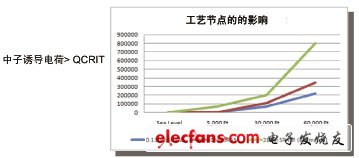

深亞微米技術增加了固件錯誤發生的概率,半導體的工藝越現金使得由輻射引起的故障率越高,隨著CMOS技術工藝尺寸繼續縮小,這對固件錯誤帶來實質性影響。如果器件發生翻轉所需的臨界電荷為QCRIT,QCRIT~VCC×CNODE。更低的電源電壓(VCC)增加了固件錯誤的易感性,使得單粒子翻轉更為普遍;更小的柵極面積 (CNODE)使得電容更小,相關的臨界電荷也會減少,因此也增加了固件錯誤的易感性。在CMOS技術中,工藝尺寸的縮小,使得柵極面積減小,并使電源電壓降低,這兩個因素都會讓單粒子翻轉變得更容易。

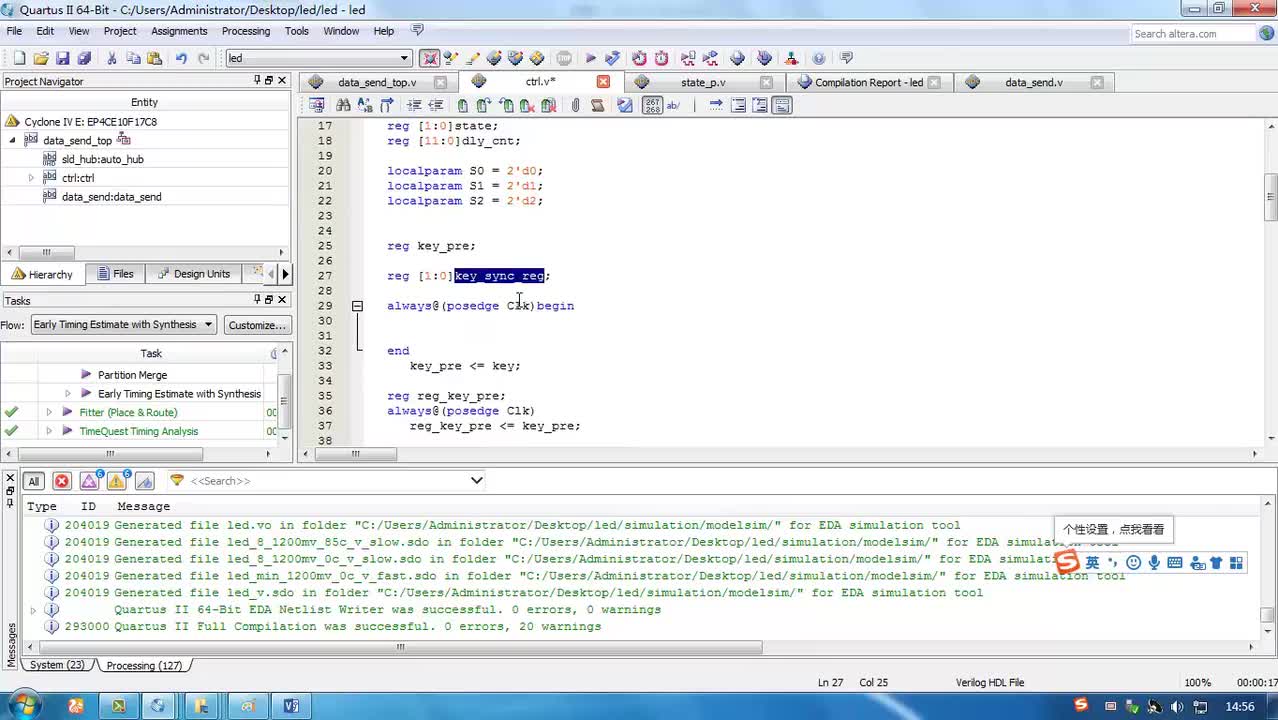

Microsemi下一代的Flash FPGA仍將具有固件錯誤免疫能力,由于Flash工藝的特點,下一代的Flash FPGA能保持足夠大的浮柵電荷QCRIT可以免受大氣中子的影響。QCRIT與工藝節點的影響如圖5所示。

高能中子在SRAM FPGA中會產生配置翻轉和數據翻轉兩種效應。

配置翻轉導致 FPGA 喪失功能,后果十分嚴重,緩減方式1:三芯片( Triple-Chip )冗余,是把同樣的電路復制到三個一樣的芯片中,通過表決的方式,當其中一個芯片輻射失效,其余的兩個芯片加起來可以仍然可以把正確的結果算出來。但是這種方式消耗過多的電路板空間及功率,而且需要外部元件進行控制和表決。緩減方式2:配置重讀和重載,這種方式不斷重新配置SRAM FPGA把已有的錯誤糾正,但是FPGA有機會在重載時再次被中子擊中,在高可用系統中是不可接受的。

數據翻轉導致單一比特位數據錯誤,后果取決于數據特性。緩減方式簡單,通過FEC、EDAC、數據清除,使用容錯性設計技術。

整體而言,緩減方式對SRAM FPGA沒有太多作用,因為配置翻轉占主導地位,而配置元件占SRAM FPGA的大部分面積。

反熔絲和Flash FPGA不存在配置翻轉, Micorsemi FPGA 器件的配置經第三方獨立實驗室的驗證能夠耐受中子、質子、γ射線、X 射線以及重離子的影響。反熔絲、Flash 及 SRAM FPGA 出現數據翻轉的比率相似,導致單一比特位數據錯誤,后果取決于數據特性。緩減方式簡單,FEC、EDAC、數據清除,使用容錯性設計技術,Micorsemi則已經驗證了消除數據錯誤的緩減技術。

隨著醫療設備變得越來越現金,在醫療設備中的電子元件含量不斷增加,使得SEU變得越來越重要,使用輻射源的應用很重視SEU免疫力。其中包括

?腫瘤科(使用 X 射線/質子源)

?牙科設備,整形設備

? CT掃描,透視,乳房X射線攝影設備

以上這些應用的需求需要可靠的劑量、快速和精確的治療、III類/ IV型設備需要有最小的停機時間,關鍵部分的功能不能中斷,不能承受功能性錯誤等。

在網絡和基礎設施中的 SEU,在大型的網絡中往往用到大量的FPGA,特別是一些跨地域的網絡,通常會用到成千上萬的FPGA,其中一個FPGA若發生問題,也可能會造成整個網絡的通信影響,特別是一些高海拔的地區,SEU的效應更為明顯。根據統計,在一些大型跨地域的網絡中,因為SEU的引起的通信中斷每幾個小時可能發生一次,思科公司內部也針對SEU提出專門的調試方案和工作條款。

SEU 的免疫力在航空電子中是非常重要的,例如:飛行計算機,駕駛艙顯示器;引擎控制和監控,制動;座艙增壓和空調;電源控制和分配,飛行表面驅動等。而這些功能如果因為SEU而喪失則是不能接受的。

在在汽車電子中的SEU方面,和醫療應用中非常類似,在汽車設計中,半導體器件的使用越來越普遍,甚至在關鍵器件中也能看到FPGA的蹤影,在汽車行業中,新版本的 AEC-Q100 規范提出 SER(軟錯誤率)的測試需求,使得它成為基于 SRAM 技術的強制性規定。

?

圖5 QCRIT與工藝節點的影響問答選編

總結

輻射對于 FPGA 的影響不局限于太空應用,SRAM FPGA 器件易于發生中子引發的配置錯誤 (固件錯誤),即便在海平面上亦然。

電子發燒友App

電子發燒友App

評論