FPGA概述

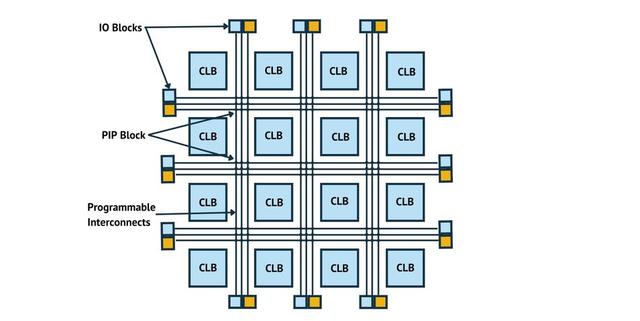

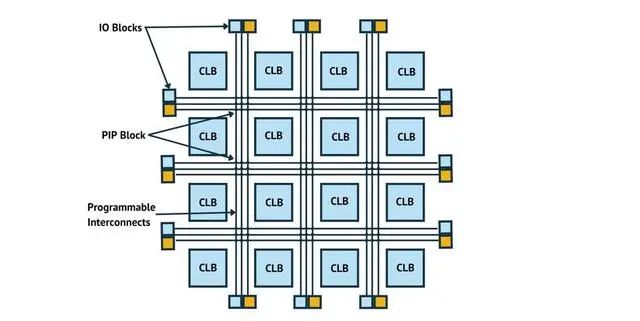

現(xiàn)場可編程門陣列(FPGA)是一種可編程邏輯器件,由成千上萬個完全相同的可編程邏輯單元組成,周圍是輸入/輸出單元構(gòu)成的外設(shè)。制造完成后,F(xiàn)PGA可以在工作現(xiàn)場編程,以便實現(xiàn)特定的設(shè)計功能。典型設(shè)計工作包括指定各單元的簡單邏輯功能,并選擇性地閉合互連矩陣中的一些開關(guān)。為確保正常工作,F(xiàn)PGA必須運用適當(dāng)?shù)?a target="_blank">電源管理技術(shù)。FPGA最初用于系統(tǒng)原型制作,最終量產(chǎn)時會用高速IC或ASIC代替。不過,近年來FPGA的性能有很大改善,成本則不斷下降,因此FPGA現(xiàn)已廣泛用于生產(chǎn)設(shè)計。

FPGA的功耗取決于許多不同因素,與設(shè)計密切相關(guān)。必須運用精確的功耗估算方法,才能確保電源系統(tǒng)符合FPGA要求。FPGA制造商會提供網(wǎng)絡(luò)工具,用于功耗計算。為了估算FPGA的功耗,計算程序需考慮設(shè)計資源運用、切換速率、工作時鐘頻率、I/O使用及其它許多因素。

FPGA主要有三種可配置元件:可配置邏輯模塊(CLB)、I/O模塊(IOB)和互連。其中,CLB提供功能邏輯元件,IOB提供封裝引腳與內(nèi)部信號線之間的接口,可編程互連資源提供路由路徑,將CLB和IOB的輸入和輸出與適合的網(wǎng)絡(luò)相連。CLB(或內(nèi)核)上施加的電壓稱為VCCINT。VCCO是IOB的電源電壓。一些FPGA還有其它電壓輸入,稱為VCCAUX。VCCINT(用于CLB)的典型值為1.0V、1.2V、1.5V、1.8V、2.5V和3V,電流可達(dá)10A或更高。CLB數(shù)量越多,則電壓越低,電流越高。啟動時,VCCINT必須單調(diào)上升,不得下跌。最常用的VCCO電壓(用于IOB)為1.2V、1.5V、1.8V、2.5V、3.3V或傳統(tǒng)系統(tǒng)中的5V。電流范圍為1A至20A。輔助電壓(VCCAUX)典型值為3.3V或2.5V。它為FPGA中的時間關(guān)鍵資源供電,因此易受電源噪聲影響。VCCAUX可以與VCCO共用一個電源層,但前提是VCCO不會產(chǎn)生過大的噪聲。

FPGA使用的電源類型

FPGA電源要求輸出電壓范圍從1.2V到5V,輸出電流范圍從數(shù)十毫安到數(shù)安培。可用三種電源:低壓差(LDO)線性穩(wěn)壓器、開關(guān)式DC-DC穩(wěn)壓器和開關(guān)式電源模塊。最終選擇何種電源取決于系統(tǒng)、系統(tǒng)預(yù)算和上市時間要求。

如果電路板空間是首要考慮因素,低輸出噪聲十分重要,或者系統(tǒng)要求對輸入電壓變化和負(fù)載瞬變做出快速響應(yīng),則應(yīng)使用LDO穩(wěn)壓器。LDO功效比較低(因為是線性穩(wěn)壓器),只能提供中低輸出電流。輸入電容通常可以降低LDO輸入端的電感和噪聲。LDO輸出端也需要電容,用來處理系統(tǒng)瞬變,并保持系統(tǒng)穩(wěn)定性。也可以使用雙輸出LDO,同時為VCCINT和VCCO供電。

如果在設(shè)計中效率至關(guān)重要,并且系統(tǒng)要求高輸出電流,則開關(guān)式穩(wěn)壓器占優(yōu)勢。開關(guān)電源的功效比高于LDO,但其開關(guān)電路會增加輸出噪聲。與LDO不同,開關(guān)式穩(wěn)壓器需利用電感來實現(xiàn)DC-DC轉(zhuǎn)換。

FPGA的特殊電源要求

為確保正確上電,內(nèi)核電壓VCCINT的緩升時間必須在制造商規(guī)定的范圍內(nèi)。對于一些FPGA,由于VCCINT會在晶體管閾值導(dǎo)通前停留更多時間,因此過長的緩升時間可能會導(dǎo)致啟動電流持續(xù)較長時間。如果電源向FPGA提供大電流,則較長的上電緩升時間會引起熱應(yīng)力。ADI公司的DC-DC穩(wěn)壓器提供可調(diào)軟啟動,緩升時間可以通過外部電容進(jìn)行控制。緩升時間典型值在20ms至100ms范圍內(nèi)。

許多FPGA沒有時序控制要求,因此VCCINT、VCCO和VCCAUX可以同時上電。如果這一點無法實現(xiàn),上電電流可以稍高。時序要求依具體FPGA而異。對于一些FPGA,必須同時給VCCINT和VCCO供電。對于另一些FPGA,這些電源可按任何順序接通。多數(shù)情況下,先給VCCINT后給VCCO供電是一種較好的做法。

當(dāng)VCCINT在0.6V至0.8V范圍內(nèi)時,某些FPGA系列會產(chǎn)生上電涌入電流。在此期間,電源轉(zhuǎn)換器持續(xù)供電。這種應(yīng)用中,因為器件需通過降低輸出電壓來限制電流,所以不推薦使用返送電流限制。但在限流電源解決方案中,一旦限流電源所供電的電路電流超過設(shè)定的額定電流,電源就會將該電流限制在額定值以下。

FPGA配電結(jié)構(gòu)

對于高速、高密度FPGA器件,保持良好的信號完整性對于實現(xiàn)可靠、可重復(fù)的設(shè)計十分關(guān)鍵。適當(dāng)?shù)碾娫磁月泛腿ヱ羁梢愿纳普w信號完整性。如果去耦不充分,邏輯轉(zhuǎn)換將會影響電源和地電壓,導(dǎo)致器件工作不正常。此外,采用分布式電源結(jié)構(gòu)也是一種主要解決方案,給FPGA供電時可以將電源電壓偏移降至最低。

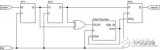

在傳統(tǒng)電源結(jié)構(gòu)中,AC/DC或DC/DC轉(zhuǎn)換器位于一個地方,并提供多個輸出電壓,在整個系統(tǒng)內(nèi)分配。這種設(shè)計稱為集中式電源結(jié)構(gòu)(CPA),見圖1。以高電流分配低電壓時,銅線或PCB軌道會產(chǎn)生嚴(yán)重的電阻損耗,CPA就會發(fā)生問題。

CPA的替代方案是分布式電源結(jié)構(gòu)(DPA),見圖2。采用DPA時,整個系統(tǒng)內(nèi)僅分配一個半穩(wěn)壓的DC電壓,各DC/DC轉(zhuǎn)換器(線性或開關(guān)式)與各負(fù)載相鄰。DPA中,DC/DC轉(zhuǎn)換器與負(fù)載(例如FPGA)之間的距離近得多,因而線路電阻和配線電感引起的電壓下降得以減小。這種為負(fù)載提供本地電源的方法稱為負(fù)載點(POL)。

圖1 集中式電源結(jié)構(gòu)

圖2 分布式電源結(jié)構(gòu)

當(dāng)一個邏輯器件從邏輯1切換到邏輯0時,或者從邏輯0切換到邏輯1時,包括電源的輸出結(jié)構(gòu)暫時變?yōu)榈妥杩範(fàn)顟B(tài)。每次轉(zhuǎn)換均要求對信號線進(jìn)行充電或放電,這就需要能量。旁路電容的功能是在本地儲存能量,以提供轉(zhuǎn)換所需的能量。

本地儲存能量必須在較寬的頻率范圍內(nèi)可用。低串聯(lián)電感的非常小的電容用來為高頻轉(zhuǎn)換提供快速電流。高頻電容能量耗盡之后,較大、較慢的電容繼續(xù)提供電流。FPGA技術(shù)要求三種頻率范圍內(nèi)的電容,即高、中、低頻率范圍。這些頻率的跨度為1kHz至500MHz。

正確放置對于高頻電容(1nF至100nF低電感陶瓷片式電容)非常重要;對于中頻電容(10μF至100μF鉭電容或陶瓷電容)和低頻電容(>470μF),這種重要性依次降低。之所以與放置有關(guān),原因很簡單:從電容引腳到FPGA電源引腳的路徑電感必須盡可能低。這意味著該路徑必須盡可能短,哪怕要穿過實體接地層或電源層。1英寸實心銅層的電感約為1nH,因此距離極為重要。旁路電容過孔必須直接下行至接地層或VCC層。

高頻旁路電容,無論是在VCCINT還是VCCIO上,均應(yīng)安裝在相關(guān)VCC引腳的1厘米范圍內(nèi);中頻旁路電容則應(yīng)安裝在VCC引腳的3厘米范圍內(nèi)。低頻旁路電容可以安裝在合理范圍內(nèi)的電路板上任意位置。當(dāng)然,離FPGA越近越好。

較新的FPGA有輸入/輸出旁路要求,因此以前用于低速或低密度設(shè)計的電容類型可能無效。根據(jù)所用材料、結(jié)構(gòu)和值的不同,旁路電容在整個頻率范圍內(nèi)有不同的串聯(lián)電抗。通過查看各種系列的數(shù)據(jù)手冊,可以得知某些電容更適合當(dāng)前所考慮的應(yīng)用。

圖3中顯示了電容阻抗隨頻率的變化曲線。阻抗最小值位于電容的自諧振頻率;超過此頻率后,寄生引線電感在“電容”的電抗特性中占據(jù)主導(dǎo)地位。圖中,業(yè)界標(biāo)準(zhǔn)型X7R單芯片、10nF陶瓷1206片式電容在50MHz時的阻抗為0.2Ω。然而,在500MHz時,該電容的阻抗約為3Ω。當(dāng)有效阻抗增大,負(fù)載無法使用電容所儲存的能量時,電容即無效。同時還必須考慮溫度范圍和老化效應(yīng)。一些電容在室溫時阻抗較低,但在極端溫度時則表現(xiàn)不佳。當(dāng)電容值較大(100nF至330nF)時,Z5U電容在高頻時的ESR可能較低。不過,這種電容不宜在10℃以下使用。作為+20%、–80%額定器件,這種電容要求幾乎兩倍的設(shè)計值才能安全使用。選擇旁路電容系列時,最好查看電容制造商的數(shù)據(jù)手冊。

FPGA電源設(shè)計可能會涉及5A、10A甚至更高的電流在PCB走線中流動。當(dāng)這種大電流存在并以開關(guān)模式(邊沿陡峭)隨時間變化時,顯而易見,噪聲、感應(yīng)電壓和電磁輻射(EMI)很可能出現(xiàn),并可能導(dǎo)致電源工作異常。與配線電感相關(guān)的快速開關(guān)電流也可能會產(chǎn)生電壓瞬變,并導(dǎo)致其它問題。為使電感和接地環(huán)路最小,傳導(dǎo)高電流的PCB走線應(yīng)盡可能短。應(yīng)采用接地層結(jié)構(gòu)或單點接地,使外部元件盡可能靠近DC/DC轉(zhuǎn)換器,以實現(xiàn)最佳效果。使用開口鐵芯電感時,必須特別注意這種電感的位置和定位,避免電感通量與敏感的反饋接地路徑和COUT配線相交。使用具有可調(diào)輸出的開關(guān)穩(wěn)壓器或控制器時,應(yīng)將反饋電阻和相關(guān)配線置于IC附近,并遠(yuǎn)離電感布置配線,尤其是開口鐵芯式電感。鐵氧體繞軸或鐵棒電感具有從繞軸一端經(jīng)空氣到達(dá)另一端的磁力線。這些磁力線會在電感磁場范圍內(nèi)的所有導(dǎo)線或PC板銅走線中產(chǎn)生感應(yīng)電壓。銅走線中產(chǎn)生的電壓量由以下因素決定:磁場強(qiáng)度、PC銅走線相對于磁場的方向和位置,以及銅走線與電感之間的距離。

FPGA和穩(wěn)壓器的可靠性取決于散熱問題。這些器件的溫度主要受待機(jī)功耗和總功耗、外部容性負(fù)載(僅FPGA)、熱阻、環(huán)境溫度以及氣流等因素控制。必須有效管理這些因素,使結(jié)溫(Tj)始終低于制造商規(guī)定的最高溫度。

ADP2114同步降壓開關(guān)穩(wěn)壓器???ADP2114,pdf datasheet (Synchronous Step-Down DC-to-DC Regulator)

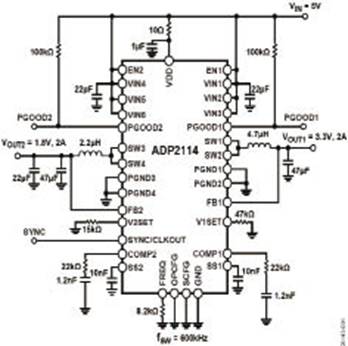

ADP2114(圖4)是一款功能多樣的同步降壓開關(guān)穩(wěn)壓器,可滿足各種客戶負(fù)載點要求。兩個PWM通道既可以配置為分別提供2A和2A(或3A/1A)電流的兩路獨立輸出,也可以配置為提供4A電流的單路交錯式輸出。ADP2114可提供高功效,開關(guān)頻率最高可達(dá)2MHz。在輕負(fù)載時,該器件可以設(shè)置為脈沖跳躍模式工作,以便提高功效,或者設(shè)置為強(qiáng)制PWM模式工作,以便降低電磁干擾(EMI)。ADP2114還具有欠壓閉鎖(UVLO)、遲滯、軟啟動和電源正常輸出指示等特性;保護(hù)特性有輸出短路保護(hù)和熱關(guān)斷等。可以利用極小電阻和電容對輸出電壓、電流限制、開關(guān)頻率、脈沖跳躍工作模式和軟啟動時間進(jìn)行外部編程。

圖3 電容阻抗隨頻率的變化曲線

圖4 ADP2114同步降壓開關(guān)穩(wěn)壓器

該器件可用于多個終端市場,例如通信基礎(chǔ)設(shè)施、工業(yè)和儀器儀表、醫(yī)療保健以及高端消費電子市場。在這些終端市場的主要應(yīng)用是分布式電源系統(tǒng)中的負(fù)載點穩(wěn)壓器。

雖然DC-DC穩(wěn)壓器的功效遠(yuǎn)高于LDO,但通常認(rèn)為其噪聲太高,無法在不顯著降低其它參數(shù)性能的情況下,直接為高性能模數(shù)轉(zhuǎn)換器供電。模數(shù)轉(zhuǎn)換器的噪聲至少有兩個來源:通過電源紋波直接耦合至轉(zhuǎn)換器中的噪聲,以及磁耦合效益引起的噪聲。

圖5所示為一種實驗室設(shè)置,針對采用低噪聲LDO供電和采用開關(guān)穩(wěn)壓器ADP2114供電兩種情況,比較一個16位、125MSPS模數(shù)轉(zhuǎn)換器的性能。評估所用的AD9268可實現(xiàn)非常低的噪聲,信噪比(SNR)為78dB。DC-DC轉(zhuǎn)換器貢獻(xiàn)的額外噪聲或雜散成分很容易反映在該模數(shù)轉(zhuǎn)換器的輸出頻譜中,因此-152dBm/Hz的低本底噪聲使它非常適合評估開關(guān)電源。

圖5 開關(guān)電源供電測試

我們將ADP2114與低噪聲LDO穩(wěn)壓器進(jìn)行比較。高性能、16位、125MSPS AD轉(zhuǎn)換器AD9268的評估結(jié)果表明:采用開關(guān)穩(wěn)壓器ADP2114供電與采用低噪聲LDO穩(wěn)壓器供電相比,性能未受影響。

因此,ADP2114可以為用戶提供可配置能力、多樣化功能和靈活性,并且具有低噪聲特性和高轉(zhuǎn)換效率。同時能夠滿足各種客戶負(fù)載點電源要求,性價比高,是FPGA、ASIC、DSP和微處理器供電的理想選擇。ADI公司提供網(wǎng)絡(luò)工具可方便設(shè)計導(dǎo)入,同時提供評估板,有助于實現(xiàn)快速導(dǎo)入。

更多詳細(xì)內(nèi)容,敬請登陸中電網(wǎng)在線座談網(wǎng)址:http://seminar.eccn.com

問答選編

問:印刷電路板中大電流供電,除加寬導(dǎo)電銅箔外,是否需要進(jìn)一步采取鍍錫等措施?

答:加鍍錫一定程度上可以加大散熱面積,但是效果不一定特別明顯,最好還是加寬加厚導(dǎo)電銅箔。

問:在供電時,如果沒考慮上電順序,對整個系統(tǒng)的運行會有什么影響?

答:這個問題要針對系統(tǒng)的各個功能模塊對上電的要求,如果系統(tǒng)中的某些電路對上電有嚴(yán)格的順序,沒有考慮到的話,很可能導(dǎo)致系統(tǒng)不工作。

問:電源紋波對FPGA性能有何影響?

答:工作時期的電源紋波要求、供電系統(tǒng)的壓降、電源通路的等效阻抗設(shè)計等參數(shù)都是用戶要特別留意的。建議在做大設(shè)計的時候一定要做電源完整性仿真,且要嚴(yán)格滿足設(shè)計約束。

問:在IPTV系統(tǒng)中的FPGA供電電源有什么要求嗎?

答:IPTV系統(tǒng)中FPGA的電源需求比較復(fù)雜,多達(dá)三種供電要求:內(nèi)核電壓、I/O電壓和輔助電壓。為了實現(xiàn)可靠的系統(tǒng)性,必須對這些排序,需要用電壓管理芯片。

問:I/O是否可以承受5V電壓?

答:這個取決于I/O的供電電壓。如果數(shù)字部分是5V供電,那么就可以。

問:ADP2118的輸出電感和電容如何選擇?它和負(fù)載電流、緩升時間有多大關(guān)系?

答:ADP2118為內(nèi)部補(bǔ)償器件,因此對輸出電感電容有一定的限制,輸出電容一般不能小于47uF,輸出電感建議為0.8~3.3uH(針對頻率設(shè)置為1.4MHz)、1.5~3.3uH(針對頻率設(shè)置為700kHz)。輸出電感電容的選擇和負(fù)載電流、軟啟動時間并無太大關(guān)系。

問:ADP2114的PWM頻率是多大?都有什么封裝形式的?

答:有三種頻率可以選擇:300kH、600kHz、1.2MHz。封裝只有一種,即LFCSP,CP-32-2。

問:ADP2114強(qiáng)制PWM工作是如何降低EMI的?

答:ADP2114強(qiáng)制PWM工作時,將使芯片在整個負(fù)載范圍內(nèi)始終工作在同一個恒定頻率,因此相比較PFM/PWM自動模式(開關(guān)頻率會在輕載時自動變化)來說,PWM工作能夠降低系統(tǒng)EMI以及系統(tǒng)噪聲。

問:FPGA電源的斜升時間(ramp-time)有哪些要求?

答:為確保供電,核心電壓VCCINT校正時間必須在一定范圍內(nèi)。對于一些FPGA,過大的校正時間會產(chǎn)生更長時間的供電電流,由于在變壓器啟動treashold中VCCINT需要更長時間。開啟校正時間長會引起熱壓力,如果電源向FPGA提供大電流。一些DC/DC變壓器提供可調(diào)節(jié)軟啟動,允許通過一個外部電容器控制校正時間。校正時間取決于FPGA制造商,典型取值為50ms~100ms。

問:FPGA供電電源的電壓功耗如何估計?電源功耗取決于哪些因素?

答:可以根據(jù)公式:Pd=(Vin-Vout)(IL)+(VIn)(Iground),其中IL是負(fù)載電流,根據(jù)公式可以看出與輸入、輸出電壓、負(fù)載電流、對地電流有關(guān)。

問:電路如何設(shè)計才能得到低紋波、低EMI、低噪聲電源?

答:首先選擇的電源應(yīng)該是低紋波、低噪聲的電源,其次就是布局布線要參考芯片資料給出的建議。

在線座談(Online Seminar)是中電網(wǎng)于2000年推出的創(chuàng)新服務(wù),通過“視頻演示+專家解說+在線問答”三位一體相結(jié)合的形式,充分發(fā)揮網(wǎng)絡(luò)平臺的便捷性,實現(xiàn)了先進(jìn)半導(dǎo)體技術(shù)提供商與系統(tǒng)設(shè)計工程師的實時互動交流,其形式和內(nèi)容都廣受電子行業(yè)工程師的好評。本刊每期將挑選一些精華內(nèi)容整理成文,以饗讀者

現(xiàn)場可編程門陣列的供電原理及應(yīng)用

- 可編程門陣列(7736)

相關(guān)推薦

五大優(yōu)勢凸顯 可編程邏輯或?qū)⒊尸F(xiàn)快速增長

可編程邏輯器件的兩種類型是現(xiàn)場可編程門陣列(FPGA)和復(fù)雜可編程邏輯器件(CPLD)。在這兩類可編程邏輯器件中,F(xiàn)PGA是在PAL、GAL、EPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。

2016-01-04 17:55:08 1404

1404

1404

1404如何使用可編程邏輯為按鈕輸入消抖:一個有效的消抖邏輯電路

可編程邏輯具有傳統(tǒng)分立 IC 無法提供的靈活性。 借助現(xiàn)成的開發(fā)工具,可輕松使用現(xiàn)場可編程門陣列和復(fù)雜可編程邏輯器件創(chuàng)建應(yīng)用特定型功能。 按鈕開關(guān)輸入消抖便是此類功能的一個例子

2017-09-06 16:15:51 9262

9262

9262

9262

用于下一代汽車專用集成電路(ASIC)的嵌入式現(xiàn)場可編程邏輯門陣列(eFPGA)

用于下一代汽車專用集成電路(ASIC)的嵌入式現(xiàn)場可編程邏輯門陣列(eFPGA)

2020-07-24 11:26:52 1234

1234

1234

123410M04SCM153C8G現(xiàn)場可編程門陣列

`類別集成電路(IC)嵌入式 - FPGA(現(xiàn)場可編程門陣列)制造商Intel系列MAX? 10包裝托盤零件狀態(tài)在售電壓 - 供電2.85V ~ 3.465V安裝類型表面貼裝型工作溫度0°C

2021-04-28 15:40:58

10M40DAF484C8G現(xiàn)場可編程門陣列

`類別集成電路(IC)嵌入式 - FPGA(現(xiàn)場可編程門陣列)制造商Intel系列MAX? 10包裝托盤零件狀態(tài)在售電壓 - 供電1.15V ~ 1.25V安裝類型表面貼裝型工作溫度0°C ~ 85

2021-04-28 15:37:46

5AGXFA7H4F35I5G現(xiàn)場可編程門陣列

`類別集成電路(IC)嵌入式 - FPGA(現(xiàn)場可編程門陣列)制造商Intel系列Arria V GX包裝托盤零件狀態(tài)在售電壓 - 供電1.07V ~ 1.13V安裝類型表面貼裝型工作溫度-40°C

2021-04-28 15:32:26

可編程技術(shù)的引爆點

25年前,賽靈思(Xilinx)公司發(fā)明了FPGA(現(xiàn)場可編程門陣列)。如今,以FPGA為代表的可編程芯片應(yīng)用已經(jīng)成為勢不可擋的發(fā)展趨勢,尤其在ASSP和傳統(tǒng)ASIC之間出現(xiàn)的市場缺口上,F(xiàn)PGA將開辟出新的領(lǐng)域,而目前席卷全球的金融危機(jī)更是成為FPGA迅速發(fā)展的催化劑。

2019-07-25 08:05:19

可編程模擬的各種架構(gòu)

是今天FPGA(現(xiàn)場可編程門陣列)流的混合信號版。可配置模擬IC已經(jīng)出現(xiàn)了多年,表面看來對市場的影響不及其數(shù)字同胞FPGA(現(xiàn)場可編程門陣列)。不過,當(dāng)前的經(jīng)濟(jì)形勢卻使可編程模擬標(biāo)準(zhǔn)產(chǎn)品的概念突然顯現(xiàn)出

2019-07-05 07:51:19

可編程邏輯器件

完成乘法,實現(xiàn)3×4,只要通過寫程序讓3連續(xù)加4次就可以完成了。而可編程邏輯器件的兩種主要類型是現(xiàn)場可編程門陣列(FPGA)和復(fù)雜可編程邏輯器件(CPLD)。 在這兩類可編程邏輯器件中,F(xiàn)PGA提供了

2014-04-15 10:02:54

可編程邏輯器件和ASIC,兩者有什么不同區(qū)別?

ASIC。PLD的種類較多,目前廣泛使用的PLD器件主要是復(fù)雜可編程邏輯器件CPLD(Complex Programmable Logic Device)和現(xiàn)場可編程門陣列FPGA(Field

2021-07-13 08:00:00

現(xiàn)場可編程門陣列是...??

解答一些常見問題(FAQ)。問題1:什么是現(xiàn)場可編程門陣列??詳細(xì)解答如下:顧名思義,有人推斷它是可編程的邏輯門結(jié)構(gòu)。這種解釋很接近,但又不太準(zhǔn)確,因為內(nèi)部邏輯陣列實際并不是利用門來實現(xiàn)的。相反,我們將

2019-08-08 09:13:00

現(xiàn)場可編程門陣列有哪些應(yīng)用?

現(xiàn)場可編程門陣列(FPGA)是一種可編程邏輯器件,由成千上萬個完全相同的可編程邏輯單元組成,周圍是輸入/輸出單元構(gòu)成的外設(shè)。制造完成后,F(xiàn)PGA可以在工作現(xiàn)場編程,以便實現(xiàn)特定的設(shè)計功能。典型設(shè)計工

2019-08-06 08:27:36

ARM Mps3現(xiàn)場可編程門陣列原型板技術(shù)參考手冊

MPS3板是一款現(xiàn)場可編程門陣列物聯(lián)網(wǎng)(IoT)開發(fā)平臺。

該主板旨在支持ARM Cortex-M類和中小型ARM Cortex-A和Cortex-R類處理器,或?qū)S枚ㄖ圃O(shè)計。

MPS3主板

2023-08-18 06:15:13

EP4CE30F23I7N現(xiàn)場可編程門陣列

`類別集成電路(IC)嵌入式 - FPGA(現(xiàn)場可編程門陣列)制造商Intel系列Cyclone? IV E包裝托盤零件狀態(tài)在售電壓 - 供電1.15V ~ 1.25V安裝類型表面貼裝型工作溫度

2021-04-28 15:29:01

FPGA-現(xiàn)場可編程門陣列

1.FPGA-現(xiàn)場可編程門陣列 每一塊FPGA芯片都是由有限多個帶有可編程連接的預(yù)定義源組成來實現(xiàn)一種可重構(gòu)數(shù)字電路。 圖1.FPGA不同構(gòu)成 FPGA芯片說明書中,包含了可編程邏輯模...

2021-07-30 07:23:42

FPGA現(xiàn)場可編程門陣列重點知識記錄

由于菜菜想要多拿點分,就在學(xué)STC的同時也選修了FPGA,今天剛開始接觸,那就記下一些重點吧FPGA現(xiàn)場可編程門陣列 (Field Programmable Gata Array)FPGA板說明

2021-12-10 07:13:09

FPGA為現(xiàn)場可編程門陣列,通過編程改變硬件的結(jié)構(gòu)

FPGA為現(xiàn)場可編程門陣列,通過編程改變硬件的結(jié)構(gòu)(電路)來實現(xiàn)不同功能,這句話應(yīng)該怎么理解,是說用verilog HDL編程完后,F(xiàn)PGA只能實現(xiàn)程序的功能還是什么,它與stm32單片機(jī)的程序有什么不同,除了語種不同外。還有要在verilog程序中分配引腳又是為什么?

2013-10-05 19:08:02

XA6SLX25-3CSG324Q現(xiàn)場可編程門陣列

XA6SLX25-3CSG324Q現(xiàn)場可編程門陣列XC3S400-4FG456C現(xiàn)場可編程門陣列XC3S400-4FG320I現(xiàn)場可編程門陣列XC3S400-5FG320C現(xiàn)場可編程門陣列XC3S500E-4FG320I現(xiàn)場可編程

2021-04-26 15:00:16

XC3SD1800A-4CSG484LI現(xiàn)場可編程門陣列

`Spartan-3ADSP現(xiàn)場可編程門陣列系列(FPGA)解決了大多數(shù)高容量的設(shè)計難題,成本敏感的高性能DSP應(yīng)用。這兩人家庭提供的密度從1.8到3.4百萬系統(tǒng)門,如表1所示。Spartan-3A

2021-04-26 15:07:49

XC5VLX85-1FF676C現(xiàn)場可編程門陣列

和FXT平臺包括高級高速串行連接和鏈接/事務(wù)層功能。XC5VLX50T-3FF665C現(xiàn)場可編程門陣列XC5VLX50T-3FFG665C現(xiàn)場可編程門陣列XC5VLX85-1FF676C現(xiàn)場可編程門陣列

2021-04-26 15:41:14

XC6SLX16-2FTG256C現(xiàn)場可編程門陣列

XC6SLX16-2FTG256C現(xiàn)場可編程門陣列XC6SLX16-2CPG196I現(xiàn)場可編程門陣列XC7A15T-1FTG256C現(xiàn)場可編程門陣列XC6SLX16-2CSG225I現(xiàn)場可編程門陣列

2021-04-13 14:30:31

XC6SLX75T-2CSG484I現(xiàn)場可編程門陣列

電壓和結(jié)溫指標(biāo)均代表最壞情況。參數(shù)包含在流行的設(shè)計和典型應(yīng)用中。XC6SLX75T-2CSG484I現(xiàn)場可編程門陣列XC6SLX75T-2FGG484I現(xiàn)場可編程門陣列

2021-04-26 15:46:35

XC7A200T-2FFV1156I現(xiàn)場可編程門陣列

FPGA。所有電源電壓和結(jié)溫規(guī)格是最壞情況的代表。參數(shù)包含在流行設(shè)計中常見且典型應(yīng)用程序。XC4VSX25-10FFG668C現(xiàn)場可編程門陣列XC7A200T-2FFV1156I現(xiàn)場可編程門陣列

2021-04-26 16:00:59

XC7K325T-2FFG900I現(xiàn)場可編程門陣列

,HPL工藝,1.0V核心電壓工藝技術(shù)和0.9V內(nèi)核電壓選項可實現(xiàn)更低的功耗。XC7K160T-2FFG676I現(xiàn)場可編程門陣列XCKU035-1FFVA1156C現(xiàn)場可編程門陣列

2021-04-13 14:27:32

不同CPU架構(gòu)以及現(xiàn)場可編程門陣列FPGA芯片區(qū)別與聯(lián)系

本文主要針對不同CPU架構(gòu)以及現(xiàn)場可編程門陣列FPGA芯片區(qū)別與聯(lián)系做一個介紹。MCU(Micro Controller Unit),又稱單片微型計算機(jī)(Single Chip

2021-11-24 06:03:37

如何利用現(xiàn)場可編程邏輯門陣列FPGA實現(xiàn)實現(xiàn)DDS技術(shù)?

介紹了利用現(xiàn)場可編程邏輯門陣列FPGA實現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法。重點介紹了DDS技術(shù)在FPGA中的實現(xiàn)方法,給出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC進(jìn)行直接數(shù)字頻率合成的VHDL源程序。

2021-04-30 06:29:00

如何利用FPGA保護(hù)IP?

什么是FPGA (現(xiàn)場可編程門陣列)?如何保護(hù)系統(tǒng)的關(guān)鍵功能和知識產(chǎn)權(quán)(IP)?

2019-08-26 08:25:51

如何利用FPGA設(shè)計可編程電壓源系統(tǒng)?

可編程電源指某些功能或參數(shù)可以通過計算機(jī)軟件編程進(jìn)行控制的電源。可編程電源的實現(xiàn)方法有很多種。其中,現(xiàn)場可編程門陣列(Field ProgrammableGate Array,F(xiàn)PGA)具有

2019-08-07 08:03:09

如何設(shè)計基于FPGA的可編程電壓源系統(tǒng)?

可編程電源指某些功能或參數(shù)可以通過計算機(jī)軟件編程進(jìn)行控制的電源。可編程電源的實現(xiàn)方法有很多種。其中,現(xiàn)場可編程門陣列(Field ProgrammableGate Array,F(xiàn)PGA)具有性能好,規(guī)模大,可重復(fù)編程,開發(fā)投資小等優(yōu)點。

2019-11-04 06:26:07

如何采用現(xiàn)場可編輯門陣列FPGA來實現(xiàn)對直流電機(jī)的控制?

如何采用現(xiàn)場可編輯門陣列FPGA來實現(xiàn)對直流電機(jī)的控制?

2021-10-19 09:08:30

怎么利用FPGA設(shè)計可編程電壓源系統(tǒng)?

可編程電源指某些功能或參數(shù)可以通過計算機(jī)軟件編程進(jìn)行控制的電源。可編程電源的實現(xiàn)方法有很多種。其中,現(xiàn)場可編程門陣列(Field ProgrammableGate Array,F(xiàn)PGA)具有

2019-08-19 06:54:51

能用單片機(jī)或者可編程邏輯門陣列控制焚燒爐的閥門、風(fēng)機(jī)、真空泵之類的嗎

能用單片機(jī)或者可編程邏輯門陣列控制焚燒爐的閥門、風(fēng)機(jī)、真空泵之類的嗎?

2023-03-27 18:02:59

請問可編程應(yīng)用的引爆點在哪里?

25年前,賽靈思(Xilinx)公司發(fā)明了FPGA(現(xiàn)場可編程門陣列)。如今,以FPGA為代表的可編程芯片應(yīng)用已經(jīng)成為勢不可擋的發(fā)展趨勢,尤其在ASSP和傳統(tǒng)ASIC之間出現(xiàn)的市場缺口上,F(xiàn)PGA將開辟出新的領(lǐng)域,而目前席卷全球的金融危機(jī)更是成為FPGA迅速發(fā)展的催化劑。

2019-10-31 06:30:27

請問什么是現(xiàn)場可編程門陣列?為什么會需要FPGA?

如果您是二元思維的人,那么不要錯過第 1 到 4 部分內(nèi)容。在這篇博客中,我將簡單介紹我最感興趣的電子器件:現(xiàn)場可編程門陣列 (FPGA)。當(dāng)我和人們談起 FPGA 時,我聽到很多人說:“我不知道

2018-10-31 11:33:29

10M02SCE144C8G FPGA - 現(xiàn)場可編程門陣列

制造商:Intel 產(chǎn)品種類:FPGA - 現(xiàn)場可編程門陣列 RoHS: 產(chǎn)品:Max 10 系列:MAX 10 10M02 邏輯元件

2021-11-25 17:36:40

LFE5U-25F-6BG256I 封裝 256-LFBGA 萊迪思 FPGA-現(xiàn)場可編程門陣列IC

嵌入式IC - FPGA(現(xiàn)場可編程門陣列), 197 I/O 256CABGA

2022-06-16 14:09:08

10M08系列 現(xiàn)場可編程門陣列 庫存現(xiàn)貨

FPGA - 現(xiàn)場可編程門陣列 non-volatile FPGA, 101 I/O, 144EQFP品牌:intel 批次:20+ 數(shù)量:63

2022-07-05 16:40:27

XC7A200T-1FBG676C FPGA可編程邏輯器件 XILINX 賽靈思 電子元器件

FBGA-672 FPGA - 現(xiàn)場可編程門陣列 , 206 I/O FPGA - 現(xiàn)場可編程門陣列 , Virtex-5 FPGA - 現(xiàn)場可編程門陣列 , - 40 C FPGA - 現(xiàn)場可編程

2022-08-04 11:25:44

XC6SLX100-3FGG484C FPGA現(xiàn)場可編程邏輯器件 XILINX 現(xiàn)場可編程門陣列

XC6SLX100-3FGG484C FPGA現(xiàn)場可編程邏輯器件 XILINX 現(xiàn)場可編程門陣列

2022-08-04 11:37:16

現(xiàn)場可編程門陣列在逆變器控制系統(tǒng)中的應(yīng)用

現(xiàn)場可編程門陣列在逆變器控制系統(tǒng)中的應(yīng)用::介紹了現(xiàn)場可編程門陣列(FPGA)器件的內(nèi)部結(jié)構(gòu)特點及其在三點式逆變器控制電路上的應(yīng)用,縮出了該設(shè)計的仿真渡形,最后分析了

2009-09-20 18:01:03 24

24

24

24LFE5U-25F-6BG256C,F(xiàn)PGA - 現(xiàn)場可編程門陣列 Lattice ECP5; 24.3K LUTs; 1.1V

LFE5U-25F-6BG256C,F(xiàn)PGA - 現(xiàn)場可編程門陣列 Lattice ECP5; 24.3K LUTs; 1.1VLFE5U-25F-6BG256C,F(xiàn)PGA - 現(xiàn)場可編程門陣列

2023-02-20 16:43:09

用現(xiàn)場可編程門陣列設(shè)計前向神經(jīng)網(wǎng)絡(luò)

本文給出了利用現(xiàn)場可編程門陣列來實現(xiàn)多層前向神經(jīng)網(wǎng)絡(luò)(反向傳播-BP 網(wǎng)絡(luò))的方法。首先利用了相關(guān)軟件在理論上作了算法上的仿真,在此基礎(chǔ)上構(gòu)建了前向神經(jīng)網(wǎng)絡(luò)的硬

2010-01-25 11:56:13 6

6

6

6基于現(xiàn)場可編程門陣列(FPGA)技術(shù)的射頻讀卡器設(shè)計

基于現(xiàn)場可編程門陣列(FPGA)技術(shù)的射頻讀卡器設(shè)計:與其他常用的自動識別技術(shù)如條形碼和磁條一樣,無線射頻識別(RFID)技術(shù)也是一種自動識別技術(shù)。每一個目標(biāo)對象在射頻讀卡

2010-03-04 09:30:22 26

26

26

26開關(guān)電容器現(xiàn)場可編程模擬陣列的頻域SPICE仿真

1 引言美國Anadigm公司的現(xiàn)場可編程模擬陣列(FPAA)采用開關(guān)電容技術(shù),將現(xiàn)場可編程邏輯陣列FPGA設(shè)計方法的優(yōu)點引入到模擬電

2006-05-26 21:46:58 1568

1568

1568

1568

什么是PLD(可編程邏輯器件)

什么是PLD(可編程邏輯器件)

PLD是可編程邏輯器件(Programable Logic Device)的簡稱,F(xiàn)PGA是現(xiàn)場可編程門陣列(Field Programable Gate Array)

2009-06-20 10:32:32 14283

14283

14283

14283

大規(guī)模現(xiàn)場可編程門陣列(FPGA)開發(fā)系統(tǒng)電源設(shè)計研究

大規(guī)模現(xiàn)場可編程門陣列(FPGA)開發(fā)系統(tǒng)電源設(shè)計研究

摘要:以Xilinx的FPGA為例,介紹了FPGA開發(fā)系統(tǒng)的電源要求和功耗,并

2009-07-06 13:38:30 665

665

665

665

現(xiàn)場可編程門陣列的結(jié)構(gòu)與設(shè)計

現(xiàn)場可編程門陣列的結(jié)構(gòu)與設(shè)計

摘要:現(xiàn)場可編程門陣列(FPGA——Field Programmable Gate Array)是上世紀(jì)80年代末發(fā)展起

2009-07-07 10:59:17 1349

1349

1349

1349

可編程陣列邏輯(Programmable Array Log

可編程陣列邏輯(Programmable Array Logic)

可編程陣列邏輯(PAL)是一種與項可編程、或項固定結(jié)構(gòu)的可編程結(jié)構(gòu),為能方便實現(xiàn)各種邏輯功能,其輸出結(jié)構(gòu)通常

2010-09-18 09:13:11 1788

1788

1788

1788基于現(xiàn)場可編程門陣列的數(shù)字調(diào)節(jié)器設(shè)計

根據(jù)磁鐵穩(wěn)流電源閉環(huán)控制的基本原理,將模擬調(diào)節(jié)器及相關(guān)的外圍控制電路采用全數(shù)字化控制技術(shù),并通過嵌入數(shù)字信號處理模塊的現(xiàn)場可編程門陣列(FPGA)來實現(xiàn),設(shè)計了數(shù)字調(diào)節(jié)

2011-04-06 14:12:17 36

36

36

36現(xiàn)場可編程門陣列(FPGA)——知識專題

FPGA(Field-Programmable Gate Array),即現(xiàn)場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。在專用集成電路(ASIC)領(lǐng)域發(fā)揮著巨大的作用。基于此電子發(fā)燒友網(wǎng)為大家提供了詳細(xì)的FPGA知識及相關(guān)資料供大家學(xué)習(xí)

2011-09-08 16:34:19

可編程邏輯陣列(PLA)簡介

電子發(fā)燒友網(wǎng)核心提示 :PLA,ProgrammableLogicArray的簡稱,意為可編程邏輯陣列。本文將著重介紹可編程邏輯陣列PLA的一些基本概念、類型以及基礎(chǔ)應(yīng)用。 一 . PLA的基本概念 可編程邏輯陣

2012-10-12 16:01:15 17896

17896

17896

17896基于龍格庫塔算法和可編程門陣列技術(shù)的混沌系統(tǒng)實現(xiàn)

提出了使用硬件描述語言 (HDL)在現(xiàn)場可編程邏輯 門陣列 器件 (FPGA)上實現(xiàn) 二階龍 格庫塔 法產(chǎn)生 混沌信

號 的一種新 方法.首先 ,根據(jù) 二階

2016-03-16 15:56:56 0

0

0

0基于現(xiàn)場可編程門陣列永磁同步電機(jī)模型的硬件在環(huán)實時仿真測試技術(shù)_

電機(jī)驅(qū)動基于現(xiàn)場可編程門陣列永磁同步電機(jī)模型的硬件在環(huán)實時仿真測試技術(shù)_黃蘇融基于現(xiàn)場可編程門陣列永磁同步電機(jī)模型的硬件在環(huán)實時仿真測試技術(shù)_黃蘇融

2016-08-03 18:36:25 21

21

21

21基于現(xiàn)場可編程門陣列的圖像調(diào)焦系統(tǒng)

基于現(xiàn)場可編程門陣列的圖像調(diào)焦系統(tǒng),感興趣的小伙伴們可以瞧一瞧。

2016-09-22 12:04:45 5

5

5

5現(xiàn)場可編程邏輯門陣列器件 FPGA原理及應(yīng)用設(shè)計

現(xiàn)場可編程邏輯門陣列器件 FPGA原理及應(yīng)用設(shè)計

2017-09-19 11:26:26 17

17

17

17現(xiàn)場可編程門陣列(FPGA)電源設(shè)計的基本方法

現(xiàn)場可編程門陣列(FPGA)被發(fā)現(xiàn)在眾多的原型和低到中等批量產(chǎn)品的心臟。 FPGA的主要優(yōu)點是在開發(fā)過程中的靈活性,簡單的升級路徑,更快地將產(chǎn)品推向市場,并且成本相對較低。一個主要缺點是復(fù)雜

2017-10-10 17:43:38 10

10

10

10FPGA(現(xiàn)場可編程門陣列)的基礎(chǔ)知識及其工作原理

高端設(shè)計工具為少有甚是沒有硬件設(shè)計技術(shù)的工程師和科學(xué)家提供現(xiàn)場可編程門陣列(FPGA)。無論你使用圖形化設(shè)計程序,ANSI C語言還是VHDL語言,如此復(fù)雜的合成工藝會不禁讓人去想FPGA真實的運作

2017-11-18 07:10:51 16860

16860

16860

16860

淺談現(xiàn)場可編程門陣列發(fā)展三個階段的驅(qū)動壓力和基本特征

自引入以來,現(xiàn)場可編程門陣列(FPGA)的容量增加了10000倍以上, 性能增加了100倍。 單位功能的成本和功耗都減少了超過1000倍。 這些進(jìn)步是由工藝縮放技術(shù)所推動的, 但是 FPGA 的故事

2018-01-22 16:55:01 1729

1729

1729

1729

英特爾Cyclone 10系列現(xiàn)場可編程門陣列,意在支持日益增多的物聯(lián)網(wǎng)應(yīng)用

為支持日益增多的物聯(lián)網(wǎng)(IoT)應(yīng)用,英特爾公司今天發(fā)布了英特爾 Cyclone 10 系列現(xiàn)場可編程門陣列(FPGA)。該系列旨在提供快速、節(jié)能的處理能力,可用于廣泛領(lǐng)域,包括汽車、工業(yè)自動化、專業(yè)視聽和視覺系統(tǒng)等。

2018-07-22 12:51:00 1363

1363

1363

1363英特爾FPGA可編程門陣列解決方案集合的詳細(xì)資料免費下載

現(xiàn)場可編程門陣列(FPGA)是集成電路,使設(shè)計人員能夠編程定制的數(shù)字邏輯在現(xiàn)場。FPGA自20世紀(jì)80年代以來一直存在,并且最初被設(shè)想為給所有設(shè)計團(tuán)隊創(chuàng)造定制邏輯的能力。在早期,在設(shè)計中使用FPGA

2018-09-20 08:00:00 10

10

10

10電子技術(shù)基礎(chǔ)知識存儲器、復(fù)雜可編程器件和現(xiàn)場可編程門陣列的介紹

本文檔的詳細(xì)介紹的是電子技術(shù)基礎(chǔ)知識存儲器、復(fù)雜可編程器件和現(xiàn)場可編程門陣列的介紹主要內(nèi)容包括了: 1 只讀存儲器,2 隨機(jī)存取存儲器,3 復(fù)雜可編程邏輯器件,4 現(xiàn)場可編程門陣列,5 用EDA技術(shù)和可編程器件的設(shè)計例題

2019-02-22 08:00:00 28

28

28

28Spartan-6現(xiàn)場可編程門陣列的直流和開關(guān)特性數(shù)據(jù)表免費下載

Spartan-6型現(xiàn)場可編程門陣列的直流和交流特性適用于商業(yè)和工業(yè)級。除工作溫度范圍或另有說明外,所有直流和交流電參數(shù)在特定速度級下均相同(即-2速度級工業(yè)設(shè)備的定時特性與a-2相同速度等級商用設(shè)備)。但是,工業(yè)范圍內(nèi)可能只有選定的速度等級和/或設(shè)備可用。

2020-01-10 15:28:55 6

6

6

6Spartan-6現(xiàn)場可編程門陣列的直流和開關(guān)特性數(shù)據(jù)手冊

Spartan-6型現(xiàn)場可編程門陣列電特性Spartan-6 lx和LXT FPGAs有各種速度等級,其中-3具有最高性能。除另有說明外,XASpartan-6型車用FPGAs和Spartan-6Q

2020-01-14 10:09:10 12

12

12

12現(xiàn)場可編程門陣列FPGA器件選型應(yīng)該考慮那些問題

現(xiàn)場可編程門陣列FPGA有集成度高、體積小、靈活可重配置、實驗風(fēng)險小等優(yōu)點,在復(fù)雜數(shù)字系統(tǒng)中得到了越來越廣泛的應(yīng)用。

2020-07-24 14:21:00 1035

1035

1035

1035

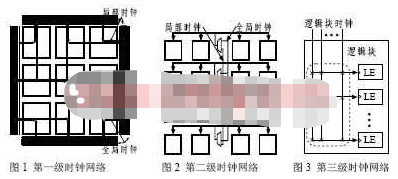

基于現(xiàn)場可編程門陣列技術(shù)設(shè)計時鐘分配網(wǎng)絡(luò)的應(yīng)用方案

自產(chǎn)生到現(xiàn)在,現(xiàn)場可編程門陣列(FPGA)以其獨特的優(yōu)點被成功應(yīng)用在工業(yè)控制、數(shù)據(jù)通信、計算機(jī)硬件等領(lǐng)域,也成功應(yīng)用在保密通信和多種先進(jìn)的武器系統(tǒng)中。

2020-08-06 17:17:14 597

597

597

597

如何使用現(xiàn)場可編程門陣列實現(xiàn)圖像調(diào)焦系統(tǒng)

數(shù)字圖像自動調(diào)焦技術(shù),不僅能提高調(diào)焦精度,而且能降低對成像系統(tǒng)加工和裝配精度的要求。采用基于功率譜的評價函數(shù)對成像系統(tǒng)的聚焦位置進(jìn)行識別,提出了基于現(xiàn)場可編程門陣列(FPGA)的自動調(diào)焦系統(tǒng)實現(xiàn)方案

2021-03-30 11:28:51 4

4

4

4現(xiàn)場可編程門陣列簡介

FPGA業(yè)界的可編程只讀存儲器(PROM)和可編程邏輯器件(PLD)萌芽。可編程只讀存儲器(PROM)和可編程邏輯器件(PLD)都可以分批在工廠或在現(xiàn)場(現(xiàn)場可編程)編程,然而,可編程邏輯被硬線連接在邏輯門之間。

2021-04-07 10:14:02 76

76

76

76采用現(xiàn)場可編程門陣列實現(xiàn)多生理參數(shù)測量系統(tǒng)的設(shè)計

隨著醫(yī)療儀器設(shè)備向智能化、微型化、系列化、數(shù)字化和多功能方向的發(fā)展,醫(yī)療設(shè)備中邏輯控制器件也由采用中、小規(guī)模的集成芯片發(fā)展到應(yīng)用現(xiàn)場可編程門陣列FPGA(Field Programmable Gate Array)

2021-04-14 11:20:09 2067

2067

2067

2067

現(xiàn)場可編程門陣列FPGA片內(nèi)的程序儲存方式

雖然現(xiàn)場可優(yōu)化CPLD和FPGA都包含大量的可編程邏輯單元,但它們的系統(tǒng)結(jié)構(gòu)存在很大的差別。與CPLD相比,F(xiàn)PGA的連接單元更多,雖然靈活卻也更加復(fù)雜;而CPLD的連接單元較少,延遲時間更加方便估計。

2022-08-17 15:39:51 1556

1556

1556

1556現(xiàn)場可編程門陣列FPGA設(shè)計驗證的主流技術(shù)是什么

現(xiàn)場可編程門陣列(Field Programmable Gate Array,F(xiàn)PGA)是在PAL、GAL、CPLD的基礎(chǔ)上產(chǎn)生的。它屬于一種半定制電路,與全定制電路相比,開發(fā)成本較低,功能可擴(kuò)展,同時又提供了較多的邏輯單元。

2022-08-22 18:07:13 415

415

415

415可編程邏輯器件測試方法

可編程邏輯器件 (Programmable Loeie Device,PLD)是一種用戶編程實現(xiàn)某種邏輯功能的邏輯器件,主要由可編程的與陣列、或陣列、門陣列等組成,可通過編程來實現(xiàn)一定的邏輯功能

2023-06-06 15:35:59 659

659

659

659

可編程邏輯器件測試

可編程邏輯器件 (Programmable Loeie Device,PLD)是一種用戶編程實現(xiàn)某種邏輯功能的邏輯器件,主要由可編程的與陣列、或陣列、門陣列等組成,可通過編程來實現(xiàn)一定的邏輯功能。

2023-06-06 15:37:45 405

405

405

405

可編程邏輯器件有哪幾種 fpga和cpld的特點

可編程邏輯陣列(Programmable Logic Array, PLA):PLA是最早的可編程邏輯器件之一,由與非門陣列和或門陣列組成,通過編程配置來實現(xiàn)特定的邏輯功能。

2023-07-04 15:28:22 1360

1360

1360

1360可編程芯片:拼合成一個模擬解決方案

可配置模擬IC已經(jīng)出現(xiàn)了多年,表面看來對市場的影響不及其數(shù)字同胞FPGA(現(xiàn)場可編程門陣列)。不過,當(dāng)前的經(jīng)濟(jì)形勢卻使可編程模擬標(biāo)準(zhǔn)產(chǎn)品的概念突然顯現(xiàn)出吸引力。

2023-10-27 17:29:59 371

371

371

371什么是FPGA?FPGA現(xiàn)場可編程門陣列的綜合指南

現(xiàn)場可編程門陣列 (FPGA) 是可以在制造后進(jìn)行編程和重新編程以實現(xiàn)數(shù)字邏輯功能的半導(dǎo)體器件。

2023-09-14 16:30:57 668

668

668

668

簡單認(rèn)識現(xiàn)場可編程門陣列

現(xiàn)場可編程門陣列 (Field Programmable Gate Array, FPGA)也稱為現(xiàn)場可編程器件,是在 PROM ( Programmable Read Only Memory

2023-12-01 09:25:15 318

318

318

318FPGA現(xiàn)場可編程門陣列的綜合指南

現(xiàn)場可編程門陣列 (FPGA) 是可以在制造后進(jìn)行編程和重新編程以實現(xiàn)數(shù)字邏輯功能的半導(dǎo)體器件。

2023-12-07 17:15:02 244

244

244

244

現(xiàn)場可編程門陣列是什么

現(xiàn)場可編程門陣列(Field Programmable Gate Array,簡稱FPGA)是一種超大規(guī)模可編程邏輯器件,由可編程邏輯資源、可編程互連資源和可編程輸入輸出資源組成。FPGA的主要功能是實現(xiàn)以狀態(tài)機(jī)為主要特征的時序邏輯電路,被廣泛應(yīng)用于計算機(jī)科學(xué)技術(shù)、計算機(jī)硬件以及計算機(jī)邏輯部件等領(lǐng)域。

2024-03-16 16:38:04 1515

1515

1515

1515現(xiàn)場可編程門陣列設(shè)計流程

現(xiàn)場可編程門陣列(FPGA)設(shè)計流程是一個綜合性的過程,它涵蓋了從需求分析到最終實現(xiàn)的各個環(huán)節(jié)。下面將詳細(xì)介紹FPGA設(shè)計流程的主要步驟。

2024-03-16 16:38:28 1555

1555

1555

1555 電子發(fā)燒友App

電子發(fā)燒友App

評論