3 軟件設計

首先編寫CPLD程序對ADG726及ADS7805進行地址譯碼,然后對CPLD在線編程生成譯碼電路。

/*--adc mux--*/

assign mux_wr=~((addr==4'h3)&(~is)&(~dsp_wr));//ADG726映射到I/O空間的地址0x3000~0x3FFF,得到寫使能信號

assign mux_en=0;//ADG726的使能引腳始終有效

/*--adc--*/

assign buffer_cs=(~(addr==4'h0))|is;//ADC映射到I/O空間的地址0x0000~0x0FFF,得到緩沖器的片選信號

assign adc_cs=~((addr==4'h0)&(~is)&dsp_rdwr);//得到ADC的片選信號

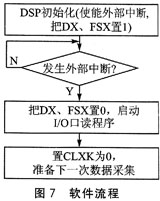

在DSP程序中,對0x3000~0x3FFF的任意地址執行一個讀操作,由DSP選擇的通道就被選通,信號由ADG726輸出到運放AD620,差分轉單端后輸出到ADC。通過寫數字I/O的控制寄存器,先將R//C拉低,再對I/O空間的0x0000~0x0FFF執行一個讀操作,然后將R//C拉高,就啟動了ADC。讀0x0000~0x0FFF 其中任一個地址產生低電平的CS信號,該信號保持的時間由訪問I/O空間的等待時間決定,通過設置等待狀態寄存器來保證獲得有效的延時時間。

/*--設置等待狀態寄存器--*/

WSGR = 0x01C0;//bit8-6=111,訪問I/O空間時插入7個等待狀態

ADC轉換完成置BUSY為高電平,向DSP申請中斷,相應中斷被使能之后DSP開始處理中斷服務程序,完成數據的讀取與其他處理。

/*--初始化ADC字程序--*/

*MCRA &= 0xFC3F;//配置4個I/O引腳bit9-6為通用功能用于ADG726通道選擇

*MCRB &= 0xFF7F;//bit7對應的I/O引腳控制R//C??

*PADATDIR |= 0xC000;//bit7-6配置為輸出,對應通道選擇的兩個引腳

*PBDATDIR |= 0x0300;//bit1-0配置為輸出,對應通道選擇的另兩個引腳

*PCDATDIR |= 0xC000;//bit6配置為輸出,對應R//C

*XINT1CR |= 0x7;//上升沿有效,低優先級,使能外部中斷

*IMR |= 0x20;//使能內核對應的中斷??

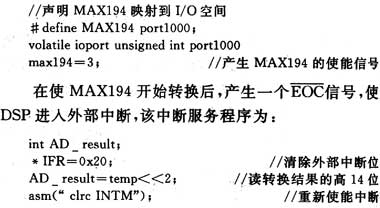

/*--聲明ADG726,ADC映射到的存儲單元--*/

#define???? AD_Output?? port0000

volatile??? ioport????? unsigned int??? port0000;

#define???? mux_ad????? port3000

volatile??? ioport????? unsigned int??? port3000;

/*--ADG726通道選擇函數--*/

*PADATDIR &= 0xFF3F;//bit7,bit6清0

*PBDATDIR &= 0xFFFC;//bit1,bit0 清0

*PADATDIR |= ( nChlNum & 0x3 ) << 6;//設置bit7,bit6

*PBDATDIR |= ( nChlNum & 0xC ) >> 2;//設置bit1,bit0

mux_ad = 0;//產生寫使能信號

/*--主程序--*/

int temp;

……

AD_Init();//初始化

ADC_MUX(13);//選擇通道13

/*--啟動ADC--*/

*PCDATDIR &= 0xFF7F;//使AD_R/C*變低

temp=AD_Output;//產生有效的AD_CS*

*PCDATDIR |= 0x80;// 使AD_R/C*變高?

for(;;);//等待ADC中斷

......

/*--中斷服務程序--*/

int???? AD_result;

*IFR = 0x20; //清除中斷標志位,以響應后續中斷

AD_result = AD_Output;//讀轉換結果

asm(“? clrc INTM”);//重新使能中斷,因為一進服務程序中斷就被禁止了

4 結束語

本文設計了基于TMS320LF2407A與EPM3032A的ADS7805多通道采集系統,介紹了系統的工作原理,詳細描述了ADS7805、DSP及CPLD之間接口的硬件與軟件設計,該方案已在筆者參與研制的嵌入式實時控制系統中得到了成功應用。

電子發燒友App

電子發燒友App

評論