引言

前面漫談車規(guī)MCU系列的首篇文章《漫談車規(guī)MCU國(guó)產(chǎn)替代》發(fā)表后,受到了廣大粉絲的廣泛關(guān)注和熱烈討論。很多留言希望我能夠介紹一下何為車規(guī)芯片,什么樣的芯片才能算是真正的車規(guī)芯片? ? 為此,我特意撰寫了本文,結(jié)合我在車規(guī)芯片行業(yè)的多年從業(yè)經(jīng)驗(yàn)和對(duì)車規(guī)MCU行業(yè)的深入洞察,較為全面的展開(kāi)“何為車規(guī)”這個(gè)話題的介紹和分析。 ?

車規(guī)芯片的四大行業(yè)標(biāo)準(zhǔn)(技術(shù)壁壘)

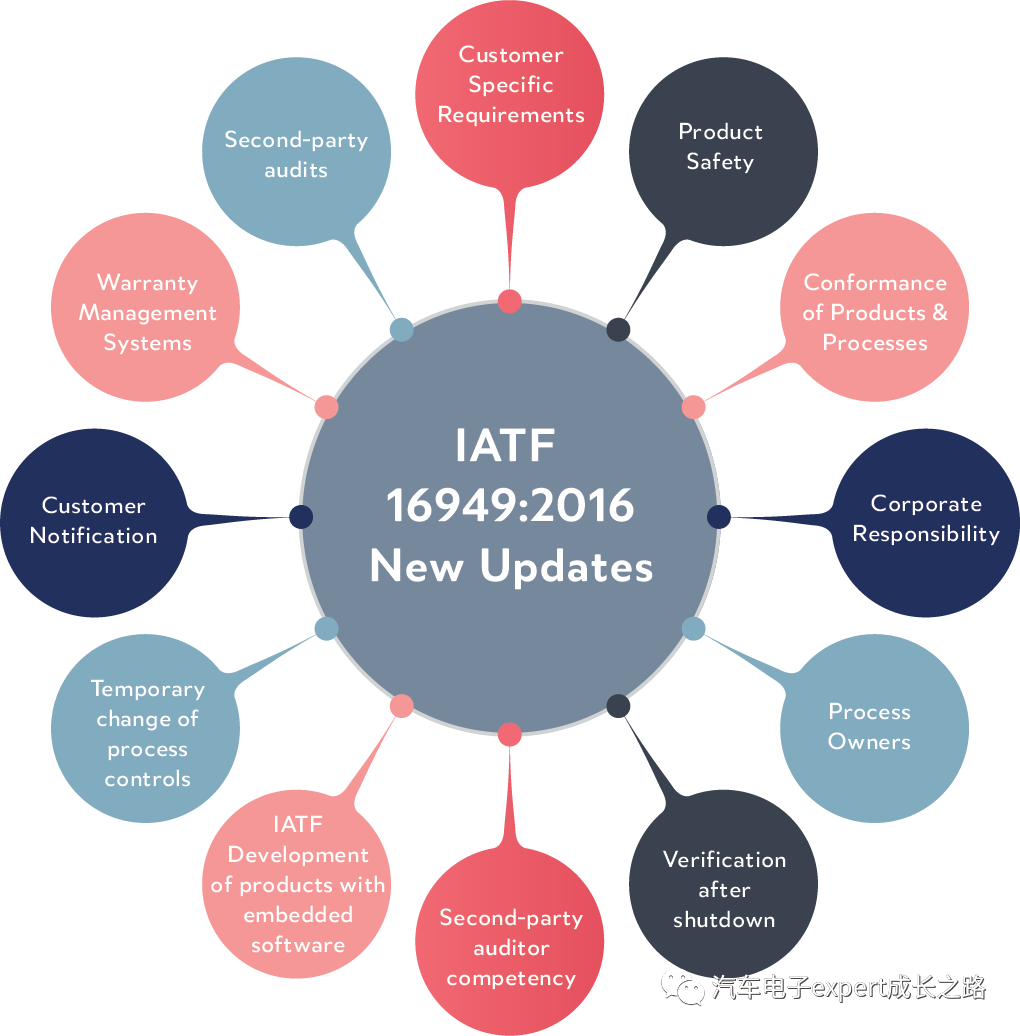

1.1 汽車行業(yè)鐵律--IATF-16949

IATF-16949是國(guó)際汽車任務(wù)組(International Automotive Task Force,簡(jiǎn)稱IATF)制定的一項(xiàng)國(guó)際標(biāo)準(zhǔn),用于質(zhì)量管理體系在汽車行業(yè)的應(yīng)用。該標(biāo)準(zhǔn)基于ISO 9001質(zhì)量管理體系標(biāo)準(zhǔn),并在此基礎(chǔ)上增加了汽車行業(yè)特定的要求和指導(dǎo),旨在提高汽車供應(yīng)鏈的質(zhì)量管理水平和產(chǎn)品質(zhì)量。

IATF的成員包括了國(guó)際標(biāo)準(zhǔn)化組織質(zhì)量管理與質(zhì)量保證技術(shù)委員會(huì)(ISO/TC176),意大利汽車工業(yè)協(xié)會(huì)(ANFIA),法國(guó)汽車制造商委員會(huì)(CCFA)和汽車裝備工業(yè)聯(lián)盟(FIEV),德國(guó)汽車工業(yè)協(xié)會(huì)(VDA),汽車制造商BMW)、Daimler Chrysler、Fiat、Ford、GM、Renault和Volkswagen等。

IATF-16949的目標(biāo)是通過(guò)建立一套規(guī)范和要求,促進(jìn)汽車制造商和供應(yīng)商之間的合作和協(xié)作,確保供應(yīng)鏈中的所有環(huán)節(jié)都符合質(zhì)量管理的最佳實(shí)踐。該標(biāo)準(zhǔn)涵蓋了從設(shè)計(jì)和開(kāi)發(fā)、生產(chǎn)、安裝和服務(wù)到產(chǎn)品退役的全生命周期,要求組織建立和實(shí)施一套完整的質(zhì)量管理體系。

? IATF-16949的要求包括質(zhì)量目標(biāo)的設(shè)定和追蹤、過(guò)程管理、產(chǎn)品和過(guò)程驗(yàn)證、供應(yīng)商管理、不良品管理、持續(xù)改進(jìn)等。它還強(qiáng)調(diào)了風(fēng)險(xiǎn)管理、員工培訓(xùn)和參與、測(cè)量和分析數(shù)據(jù)等方面的重要性。 ? 通過(guò)實(shí)施IATF-16949,組織可以提高產(chǎn)品質(zhì)量和可靠性,減少缺陷和客戶投訴,提高生產(chǎn)效率和交付能力。此外,符合IATF-16949的組織還可以獲得國(guó)際認(rèn)可,增加在汽車行業(yè)中的競(jìng)爭(zhēng)力和市場(chǎng)份額。 ?

IATF-16949最為人所知的五大工具如下: ?

統(tǒng)計(jì)過(guò)程控制(SPC)

測(cè)量系統(tǒng)分析(MSA)

產(chǎn)品質(zhì)量先期策劃(APQP)

潛在失效模式和效果分析(FMEA)

生產(chǎn)件批準(zhǔn)程序(PPAP) ?

其中,PPAP報(bào)告是汽車產(chǎn)業(yè)鏈供應(yīng)商逐級(jí)提供的,由晶圓廠和封測(cè)廠提供的PPAP被整合到車規(guī)芯片的PPAP中,然后提供給零部件設(shè)計(jì)生成商(Tier-1),最后由Tier-1整合ECU系統(tǒng)軟硬件設(shè)計(jì)和生產(chǎn)的流程數(shù)據(jù)提供給整車廠。

1.2 車規(guī)芯片可靠性驗(yàn)證標(biāo)準(zhǔn)--AEC-Q100

AEC-Q100是由汽車電子委員會(huì)(Automotive Electronics Council,簡(jiǎn)稱AEC, 最初是由克萊斯勒、福特和通用汽車于 1990 年代成立 的組織,目的是建立通用的零件鑒定和質(zhì)量體系標(biāo)準(zhǔn))制定的一項(xiàng)汽車電子元器件可靠性標(biāo)準(zhǔn)。該標(biāo)準(zhǔn)旨在確保在汽車電子系統(tǒng)中使用的元器件具有足夠的可靠性和耐久性,以滿足汽車行業(yè)的嚴(yán)格要求。 ? AEC 是建立可靠、高質(zhì)量電子組件標(biāo)準(zhǔn)的標(biāo)準(zhǔn)化機(jī)構(gòu)。符合這些規(guī)格的組件適用于惡劣的汽車環(huán)境,無(wú)需額外的組件級(jí)鑒定測(cè)試。包括: ?

AEC-Q100:集成電路(IC)器件,比如MCU、ADC、PMIC, CAN/LIN收發(fā)器等;

AEC-Q101:分離(Discrete)器件,比如三極管、二極管、MOSFET, SiC等;

AEC-Q102:分離光電(Discrete Optoelectronic )器件,比如LED等;

AEC-Q103:分離傳感器(Sensor)器件,比如MEMS壓力/加速度計(jì)、溫度傳感器等;

AEC-Q104:分離多芯片模塊(MCM)器件,除Q100/101/102/103和Q200不能覆蓋的多芯片模塊;

AEC-Q200:無(wú)源器件,比如電容、電阻、電感等;

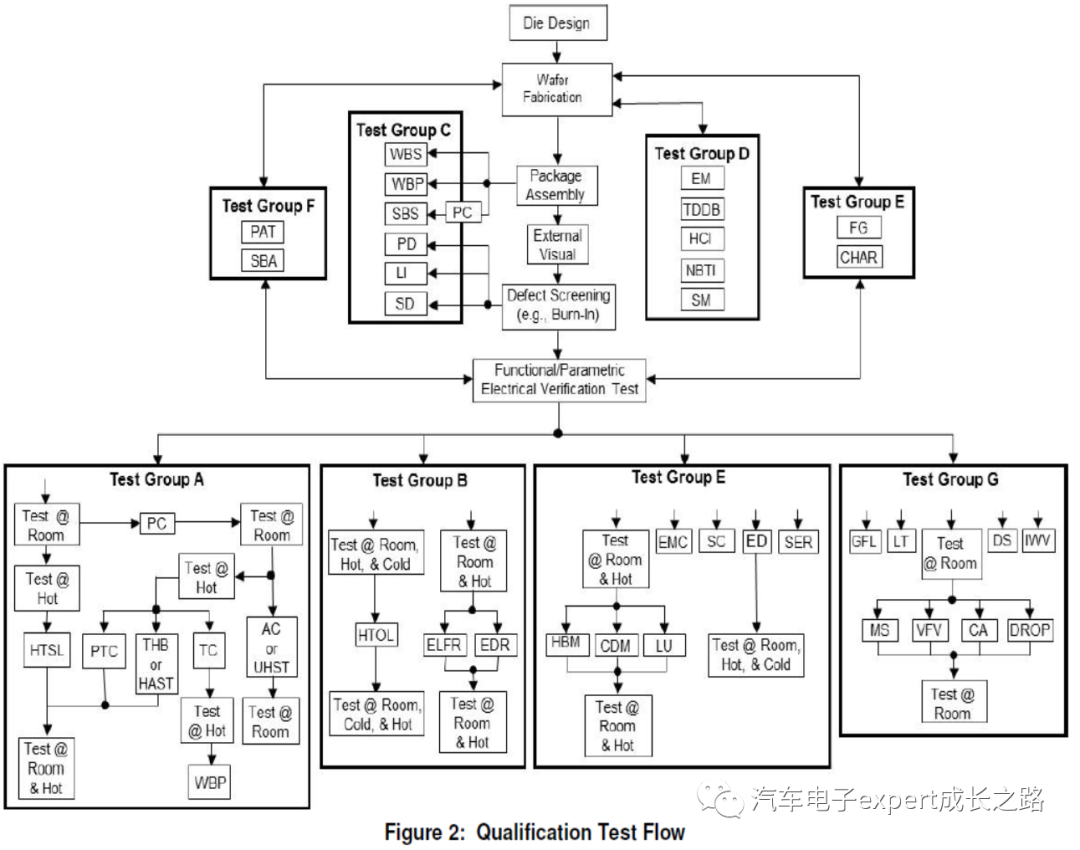

AEC-Q100標(biāo)準(zhǔn)主要適用于集成電路(IC)和半導(dǎo)體器件,對(duì)其進(jìn)行了一系列的可靠性測(cè)試和評(píng)估,其測(cè)試驗(yàn)證項(xiàng)目最多最復(fù)雜,周期也是最長(zhǎng)的(以IC芯片功能的規(guī)模和復(fù)雜度而定)。這些測(cè)試和評(píng)估包括溫度循環(huán)測(cè)試、濕熱循環(huán)測(cè)試、可靠性評(píng)估、可靠性預(yù)測(cè)等。通過(guò)這些測(cè)試,可以評(píng)估元器件在不同環(huán)境條件下的可靠性和性能。

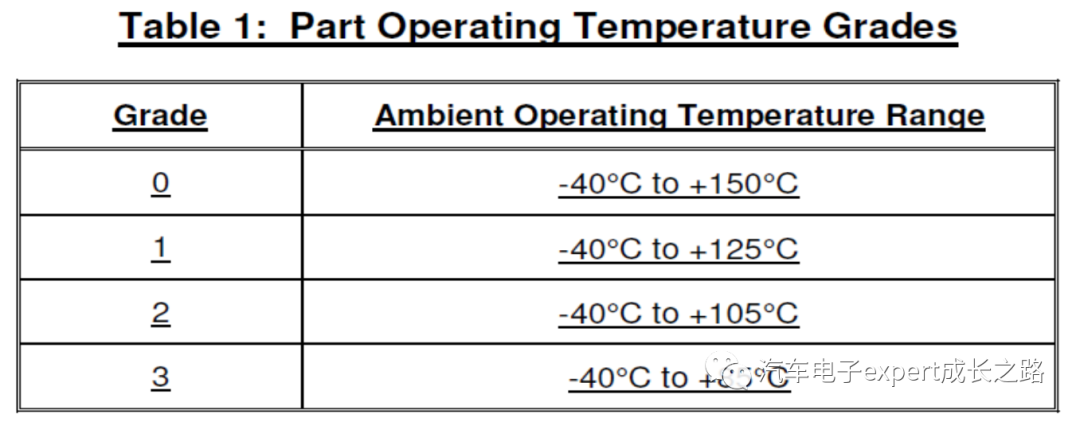

AEC-Q100標(biāo)準(zhǔn)分為幾個(gè)等級(jí),包括Grade 0到Grade 3,每個(gè)等級(jí)代表了不同的可靠性要求和測(cè)試條件。Grade 0是最高等級(jí),適用于在高溫環(huán)境下工作的關(guān)鍵應(yīng)用,而Grade 3適用于一般的汽車電子應(yīng)用。

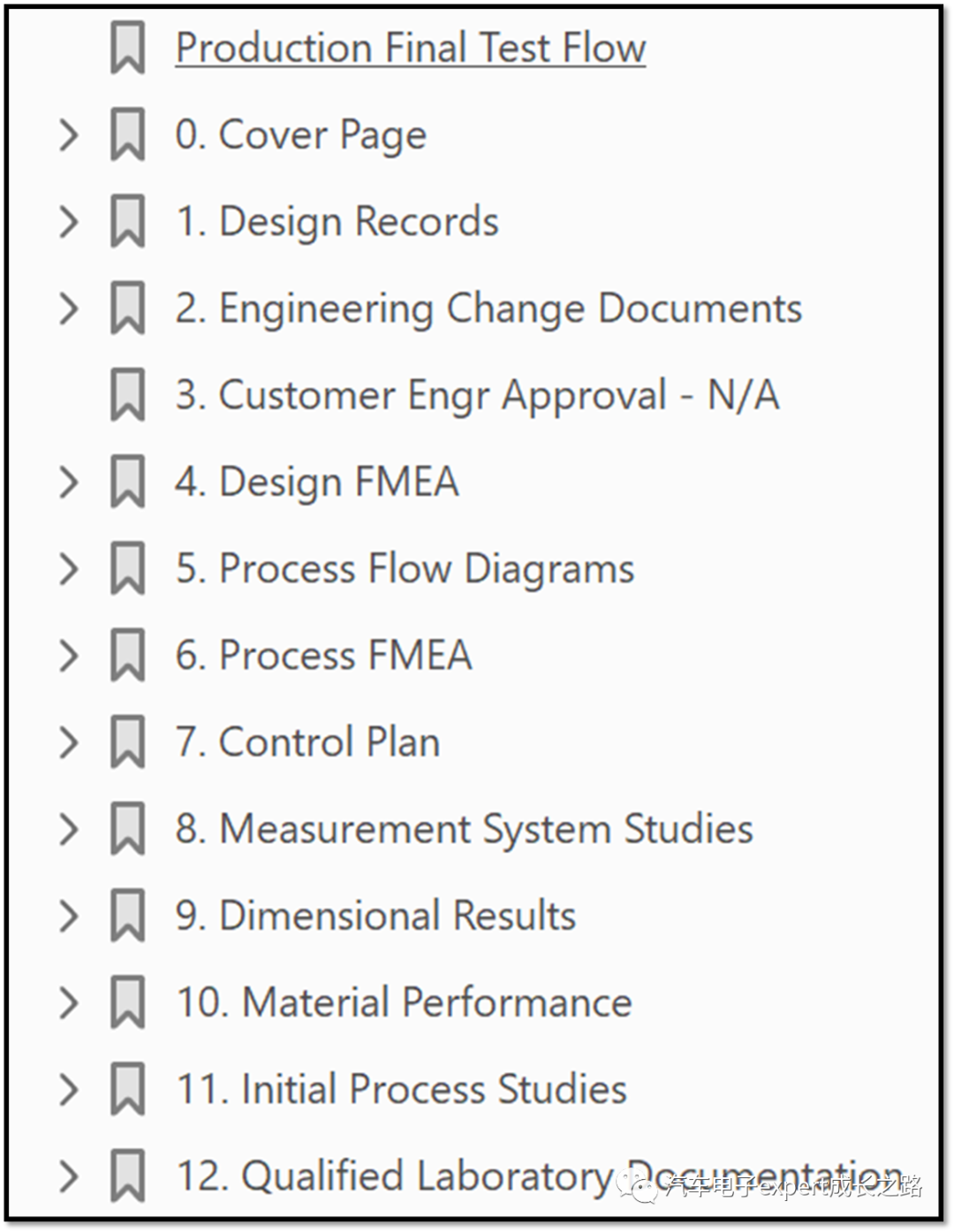

符合AEC-Q100標(biāo)準(zhǔn)的元器件可以獲得汽車制造商的認(rèn)可,并被廣泛應(yīng)用于汽車電子系統(tǒng)中,如發(fā)動(dòng)機(jī)控制單元、車身控制模塊、安全氣囊系統(tǒng)等。這些元器件經(jīng)過(guò)嚴(yán)格的可靠性測(cè)試和評(píng)估,能夠在惡劣的汽車環(huán)境下穩(wěn)定運(yùn)行,確保汽車的安全性和可靠性。 ? AEC-Q100包含測(cè)試結(jié)果將包含在一份量產(chǎn)器件審批流程報(bào)告(PPAP report)中給到客戶(Tier-1/Car OEM),其中還包括芯片的設(shè)計(jì)和流程失效模式與影響分析(Design FMEA & Process FMEA),如下是一份完整的量產(chǎn)車規(guī)MCU芯片的PPAP報(bào)告目錄:

1.3 車規(guī)芯片功能安全標(biāo)準(zhǔn)--ISO 26262

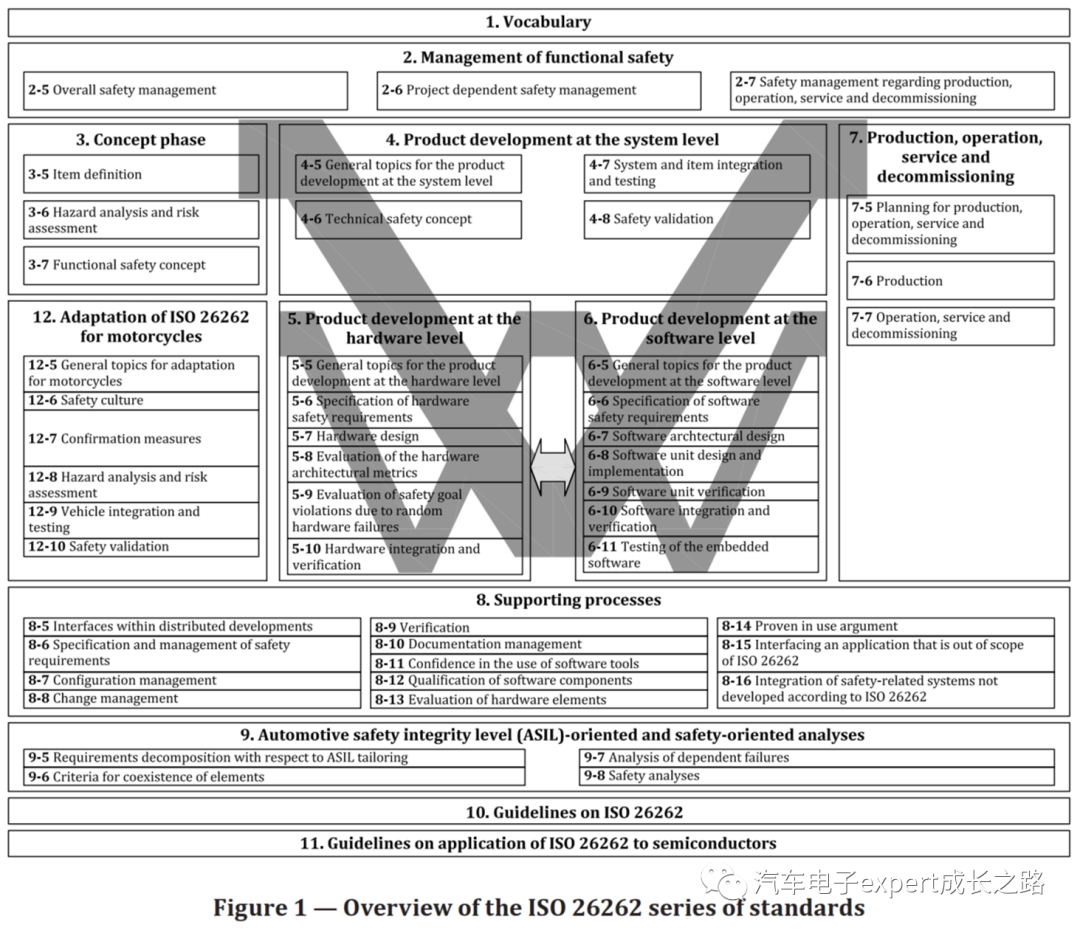

功能安全I(xiàn)SO-26262是IEC61508 對(duì)電子電氣(E/E )系統(tǒng)在道路車輛方面的功能安全要求的具體應(yīng)用。 ? ISO 26262是一項(xiàng)國(guó)際標(biāo)準(zhǔn),用于汽車行業(yè)中的功能安全管理系統(tǒng)。該標(biāo)準(zhǔn)于2011年發(fā)布初版,2018年再版,新增了兩個(gè)章節(jié)--第12章:ISO26262對(duì)摩托車的適用性和第11章:ISO26262對(duì)半導(dǎo)體器件的應(yīng)用指南,旨在確保在車輛電子和電氣系統(tǒng)中的功能安全性,以減少由于系統(tǒng)故障引起的事故和傷害。 ? ISO 26262標(biāo)準(zhǔn)適用于汽車電子和電氣系統(tǒng)的整個(gè)生命周期,包括設(shè)計(jì)、開(kāi)發(fā)、生產(chǎn)、操作、維護(hù)和退役階段。它提供了一套方法和要求,幫助汽車制造商和供應(yīng)商在設(shè)計(jì)和開(kāi)發(fā)過(guò)程中識(shí)別和管理潛在的安全風(fēng)險(xiǎn)。

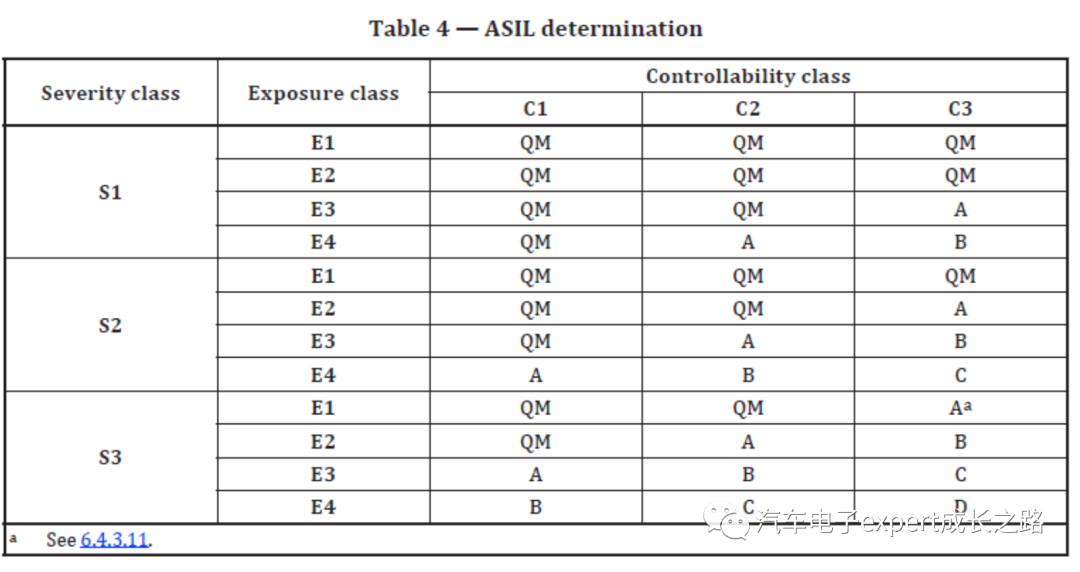

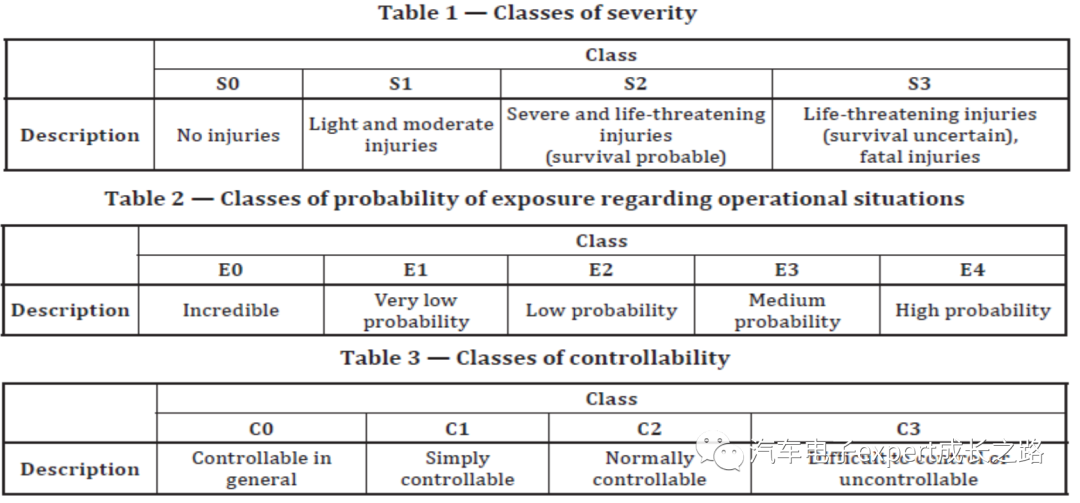

ISO 26262標(biāo)準(zhǔn)的關(guān)鍵概念包括安全性管理、安全性生命周期、安全性驗(yàn)證和確認(rèn),以及安全性要求的定義和評(píng)估。它要求組織進(jìn)行安全風(fēng)險(xiǎn)評(píng)估和安全性目標(biāo)的設(shè)定,采取適當(dāng)?shù)陌踩O(shè)計(jì)措施,并進(jìn)行系統(tǒng)安全驗(yàn)證和確認(rèn)。 ISO-26262提供了決定風(fēng)險(xiǎn)等級(jí)的具體風(fēng)險(xiǎn)評(píng)估方法HARA(SEC(嚴(yán)重度(S)、暴露率(E)、和可控性(C)三個(gè)指標(biāo) à ASIL- A/B/C/D or QM)等級(jí);

?

ISO-26262通過(guò)分析系統(tǒng)需求,關(guān)注具體的功能安全目標(biāo)(SG), 通過(guò)系統(tǒng)實(shí)現(xiàn)軟硬件評(píng)估/分解/驗(yàn)證,使用有效的功能安全機(jī)制(SM)保證單點(diǎn)失效(SPFM)和潛在失效(LFM)的目標(biāo)診斷覆蓋率(DC),同時(shí)滿足隨機(jī)硬件故障概率(PMHF, 單位為FIT(Failure In Time),1FIT = 1/10(-9)h, 即1000,000,000小時(shí)內(nèi)失效僅1次)要求;

通過(guò)遵循ISO 26262標(biāo)準(zhǔn),汽車制造商和供應(yīng)商可以確保其電子和電氣系統(tǒng)滿足功能安全的要求,減少系統(tǒng)故障導(dǎo)致的潛在風(fēng)險(xiǎn)。這有助于提高汽車的安全性和可靠性,并滿足法規(guī)和客戶的要求。同時(shí),符合ISO 26262的組織還能夠提高其在汽車行業(yè)中的競(jìng)爭(zhēng)力和市場(chǎng)份額。 ?

1.4 車規(guī)芯片信息安全標(biāo)準(zhǔn)--ISO 21434

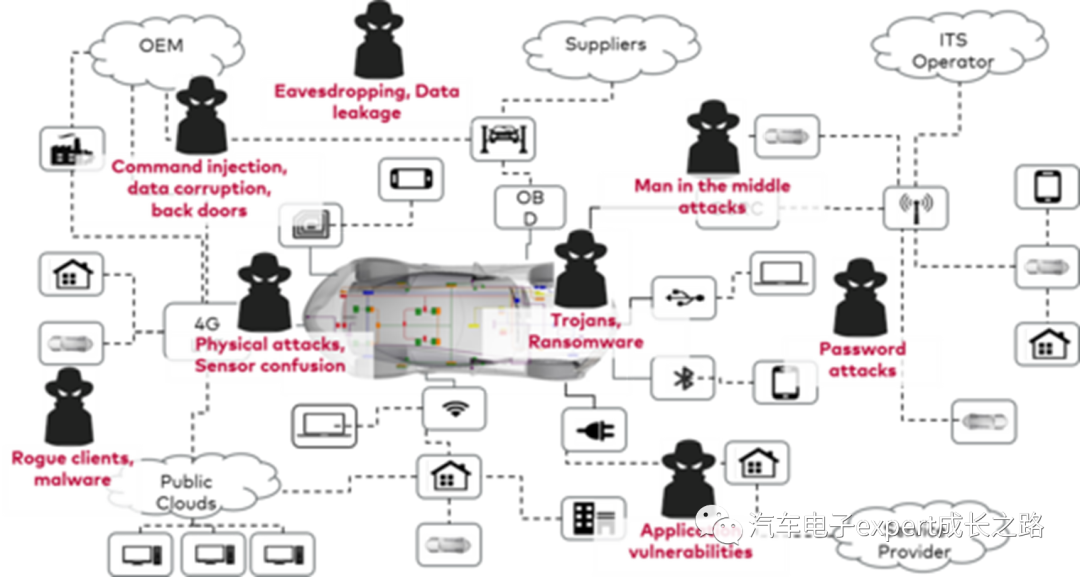

隨著車聯(lián)網(wǎng)應(yīng)用的日益普及,針對(duì)汽車的網(wǎng)絡(luò)攻擊風(fēng)險(xiǎn)越來(lái)越高:作為汽車的空中編程(OTA)、車隊(duì)管理系統(tǒng)、車輛和其他設(shè)備通訊(V2X / V2V)等功能的基礎(chǔ)架構(gòu),汽車也出現(xiàn)了新的攻擊面。基于開(kāi)發(fā)的考量,需要在標(biāo)準(zhǔn)上有對(duì)應(yīng)的措施。 ? ISO 21434是一項(xiàng)新的國(guó)際標(biāo)準(zhǔn),專門針對(duì)汽車行業(yè)中的信息安全進(jìn)行管理和保護(hù)。該標(biāo)準(zhǔn)于2021年發(fā)布,旨在幫助汽車制造商和供應(yīng)商建立和維護(hù)安全的汽車電子和軟件系統(tǒng)。

ISO 21434標(biāo)準(zhǔn)的目標(biāo)是確保汽車電子和軟件系統(tǒng)在設(shè)計(jì)、開(kāi)發(fā)、生產(chǎn)、操作和維護(hù)的整個(gè)生命周期中具備適當(dāng)?shù)男畔踩刂拼胧K峁┝艘惶追椒ê鸵螅詭椭M織識(shí)別和管理潛在的信息安全風(fēng)險(xiǎn),保護(hù)車輛免受惡意攻擊和未經(jīng)授權(quán)的訪問(wèn)。

ISO 21434標(biāo)準(zhǔn)涵蓋了許多關(guān)鍵方面,包括安全風(fēng)險(xiǎn)評(píng)估、安全需求分析、安全設(shè)計(jì)、安全驗(yàn)證和確認(rèn)、安全生命周期管理等。它要求組織在設(shè)計(jì)和開(kāi)發(fā)過(guò)程中采取適當(dāng)?shù)陌踩胧缟矸蒡?yàn)證、訪問(wèn)控制、數(shù)據(jù)保護(hù)、通信安全等。 ISO/SAE 21434的核心是威脅分析以及風(fēng)險(xiǎn)評(píng)估。其基于威脅分析與風(fēng)險(xiǎn)評(píng)估(TARA)方法,定義了類似于 ISO 26262 中的 ASIL的網(wǎng)絡(luò)安全保證級(jí)別(CAL)。 ? 通過(guò)遵循ISO 21434標(biāo)準(zhǔn),汽車制造商和供應(yīng)商可以提高其車輛和系統(tǒng)的信息安全性,減少被黑客攻擊和未經(jīng)授權(quán)訪問(wèn)的風(fēng)險(xiǎn)。這有助于保護(hù)車輛中的關(guān)鍵功能和數(shù)據(jù),確保駕駛員和乘客的安全和隱私。 ? ISO 21434標(biāo)準(zhǔn)的實(shí)施還可以幫助汽車行業(yè)滿足法規(guī)和客戶對(duì)信息安全的要求,并提高組織在市場(chǎng)競(jìng)爭(zhēng)中的信譽(yù)和競(jìng)爭(zhēng)力。同時(shí),它也促進(jìn)了汽車行業(yè)對(duì)信息安全的重視和持續(xù)改進(jìn)。 ?

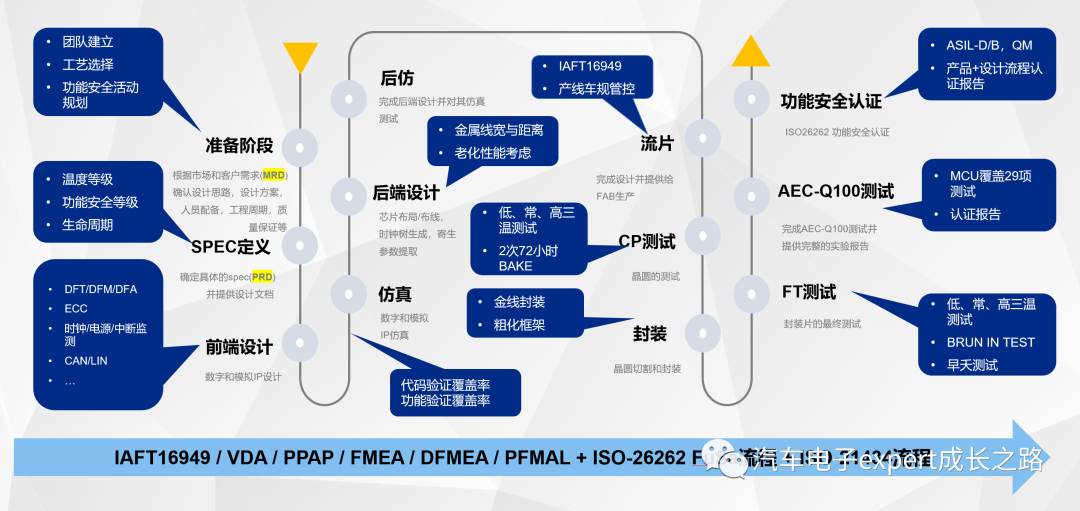

完整的車規(guī)芯片研發(fā)流程

為了保證車規(guī)芯片的高性能和高可靠性,必須掌握和使用符合IATF-16949并結(jié)合汽車功能安全和信息安全流程的完整的車規(guī)芯片研發(fā)流程。

為了幫助大家更好的理解相關(guān)概念,這里有必要介紹一下芯片設(shè)計(jì)的各環(huán)節(jié)和流程要求要點(diǎn)及意義。 ?

2.1 需求定義(MRD和PRD)

芯片的需求定義主要包括市場(chǎng)需求文檔(Market Requirements Document,MRD)和產(chǎn)品需求文檔(Product Requirements Document,PRD)。 ? 市場(chǎng)需求文檔(MRD)是在芯片設(shè)計(jì)之前制定的,它主要描述了市場(chǎng)對(duì)芯片產(chǎn)品的需求和期望。MRD通常由市場(chǎng)營(yíng)銷團(tuán)隊(duì)或產(chǎn)品管理團(tuán)隊(duì)編寫,包括以下內(nèi)容: ?

市場(chǎng)背景:描述芯片產(chǎn)品所處的市場(chǎng)環(huán)境和競(jìng)爭(zhēng)情況,包括市場(chǎng)規(guī)模、增長(zhǎng)趨勢(shì)、競(jìng)爭(zhēng)對(duì)手等。

目標(biāo)市場(chǎng)和用戶:明確芯片產(chǎn)品的目標(biāo)市場(chǎng)和目標(biāo)用戶,包括行業(yè)、應(yīng)用領(lǐng)域、用戶需求等。

產(chǎn)品定位:定義芯片產(chǎn)品在市場(chǎng)中的定位和差異化特點(diǎn),包括產(chǎn)品的主要功能、性能要求、價(jià)格范圍等。

功能需求:列出芯片產(chǎn)品的主要功能需求,包括支持的通信協(xié)議、數(shù)據(jù)處理能力、接口要求等。

性能需求:定義芯片產(chǎn)品的性能指標(biāo),包括速度、功耗、可靠性等。

市場(chǎng)需求優(yōu)先級(jí):根據(jù)市場(chǎng)需求的重要性和緊迫性,對(duì)各項(xiàng)需求進(jìn)行優(yōu)先級(jí)排序。

產(chǎn)品需求文檔(PRD)是在MRD的基礎(chǔ)上進(jìn)一步細(xì)化和詳細(xì)描述芯片產(chǎn)品的具體功能和電氣參數(shù)規(guī)格(spec.),它主要由產(chǎn)品經(jīng)理或系統(tǒng)工程師編寫,包括以下內(nèi)容: ?

產(chǎn)品概述:對(duì)芯片產(chǎn)品的整體概述和目標(biāo)進(jìn)行描述,包括產(chǎn)品的主要特點(diǎn)和優(yōu)勢(shì)。

功能需求:詳細(xì)說(shuō)明芯片產(chǎn)品的各項(xiàng)功能需求,包括功能模塊、接口要求、數(shù)據(jù)處理能力等。

性能需求:具體定義芯片產(chǎn)品的性能指標(biāo),包括速度、功耗、時(shí)延、抗干擾能力等。

通信接口需求:描述芯片產(chǎn)品與外部設(shè)備的接口和通信協(xié)議要求,包括物理接口、電氣特性、數(shù)據(jù)格式等。

可靠性需求:定義芯片產(chǎn)品的可靠性要求,包括壽命、穩(wěn)定性、故障率等。

安全性需求:列出芯片產(chǎn)品的安全性要求,包括數(shù)據(jù)保護(hù)、身份認(rèn)證、防篡改等。

限制和約束:說(shuō)明芯片設(shè)計(jì)中的限制和約束條件,包括成本、尺寸、供電要求等。

MRD和PRD是芯片設(shè)計(jì)的基礎(chǔ),它們明確了芯片產(chǎn)品的需求和目標(biāo),為后續(xù)的芯片設(shè)計(jì)和開(kāi)發(fā)工作提供了指導(dǎo)和依據(jù)。同時(shí),MRD和PRD也是與客戶和合作伙伴進(jìn)行溝通和協(xié)調(diào)的重要文檔。 ?

2.2 前端設(shè)計(jì)(數(shù)字外設(shè)和模擬外設(shè)IP設(shè)計(jì))

芯片的前端設(shè)計(jì)包括數(shù)字外設(shè)和模擬外設(shè)IP設(shè)計(jì),是芯片設(shè)計(jì)中的重要組成部分,它們提供了與外部設(shè)備進(jìn)行通信和交互的接口和功能。下面是數(shù)字外設(shè)和模擬外設(shè)IP設(shè)計(jì)的一般流程: ?

外設(shè)需求分析:在開(kāi)始設(shè)計(jì)之前,需要明確外設(shè)的功能需求和接口要求。這包括外設(shè)的數(shù)據(jù)傳輸速率、通信協(xié)議、數(shù)據(jù)格式等方面的要求。同時(shí),還需要考慮外設(shè)與芯片的連接方式和電氣特性等。

IP架構(gòu)設(shè)計(jì):根據(jù)外設(shè)需求分析,設(shè)計(jì)IP的整體架構(gòu)。這包括確定IP的功能模塊、接口和數(shù)據(jù)路徑等。在數(shù)字外設(shè)IP設(shè)計(jì)中,常見(jiàn)的功能模塊包括數(shù)據(jù)緩沖、時(shí)鐘管理、數(shù)據(jù)處理等。在模擬外設(shè)IP設(shè)計(jì)中,常見(jiàn)的功能模塊包括模擬信號(hào)輸入輸出接口、信號(hào)處理電路等。

IP設(shè)計(jì)和驗(yàn)證:根據(jù)IP架構(gòu)設(shè)計(jì),進(jìn)行IP的詳細(xì)設(shè)計(jì)和驗(yàn)證。在數(shù)字外設(shè)IP設(shè)計(jì)中,使用硬件描述語(yǔ)言(如Verilog或VHDL)來(lái)描述IP的邏輯結(jié)構(gòu)和功能。在模擬外設(shè)IP設(shè)計(jì)中,使用模擬電路設(shè)計(jì)工具進(jìn)行電路設(shè)計(jì)和仿真驗(yàn)證。

IP集成和驗(yàn)證:將設(shè)計(jì)好的IP集成到芯片的整體設(shè)計(jì)中,并進(jìn)行驗(yàn)證。在數(shù)字外設(shè)IP設(shè)計(jì)中,需要進(jìn)行邏輯仿真和時(shí)序仿真,驗(yàn)證IP的功能和時(shí)序性能是否符合設(shè)計(jì)要求。在模擬外設(shè)IP設(shè)計(jì)中,需要進(jìn)行電路仿真和電路驗(yàn)證,驗(yàn)證IP的模擬性能是否符合設(shè)計(jì)要求。

物理設(shè)計(jì)和布局:對(duì)IP進(jìn)行物理設(shè)計(jì)和布局,將IP的電路結(jié)構(gòu)和布局規(guī)則與芯片的其他部分進(jìn)行整合。物理設(shè)計(jì)包括IP的布局、布線、時(shí)鐘樹(shù)設(shè)計(jì)等。通過(guò)物理設(shè)計(jì)和布局,可以優(yōu)化IP的面積、功耗和性能等。

物理驗(yàn)證:對(duì)IP進(jìn)行最終的物理驗(yàn)證,確保IP的物理設(shè)計(jì)滿足設(shè)計(jì)要求和約束。物理驗(yàn)證包括電氣規(guī)則檢查(DRC)、布局規(guī)則檢查(LVS)等。

IP文檔和測(cè)試:最后,根據(jù)IP設(shè)計(jì)和驗(yàn)證的結(jié)果,生成IP的設(shè)計(jì)文檔和測(cè)試文檔。設(shè)計(jì)文檔包括IP的規(guī)格說(shuō)明、設(shè)計(jì)原理和接口定義等。測(cè)試文檔包括IP的測(cè)試計(jì)劃、測(cè)試用例和測(cè)試結(jié)果等。

數(shù)字外設(shè)和模擬外設(shè)IP設(shè)計(jì)在芯片設(shè)計(jì)中起著重要的作用,它們提供了與外部設(shè)備進(jìn)行通信和交互的接口和功能。通過(guò)設(shè)計(jì)和驗(yàn)證IP,可以確保芯片與外部設(shè)備的兼容性和可靠性,提高芯片的功能和性能。同時(shí),IP設(shè)計(jì)的模塊化和可重用性也可以提高芯片設(shè)計(jì)的效率和可靠性。 ?

2.3 邏輯仿真和數(shù)字驗(yàn)證

芯片設(shè)計(jì)的邏輯仿真和數(shù)字驗(yàn)證是芯片設(shè)計(jì)流程中非常重要的一環(huán),它主要用于驗(yàn)證芯片的功能和時(shí)序等方面的正確性。下面是邏輯仿真和數(shù)字驗(yàn)證的一般流程: ?

設(shè)計(jì)規(guī)格和功能驗(yàn)證:在開(kāi)始邏輯仿真之前,首先需要明確芯片的設(shè)計(jì)規(guī)格和功能要求。根據(jù)這些要求,制定驗(yàn)證計(jì)劃,并編寫測(cè)試用例。

邏輯仿真:邏輯仿真是通過(guò)軟件工具模擬芯片電路的行為,驗(yàn)證電路的功能是否符合設(shè)計(jì)規(guī)格。在邏輯仿真中,會(huì)使用硬件描述語(yǔ)言(如Verilog或VHDL)來(lái)描述電路的邏輯結(jié)構(gòu)和功能,并使用仿真工具進(jìn)行仿真運(yùn)行。通過(guò)仿真結(jié)果,可以檢查電路的功能是否正確。

時(shí)序仿真:時(shí)序仿真是在邏輯仿真的基礎(chǔ)上,考慮電路的時(shí)序約束,驗(yàn)證電路的時(shí)序性能是否滿足設(shè)計(jì)要求。時(shí)序仿真可以檢查電路的時(shí)鐘頻率、時(shí)序路徑、時(shí)序敏感性等方面的性能。

電源和環(huán)境仿真:除了功能和時(shí)序仿真,還需要進(jìn)行電源和環(huán)境仿真,驗(yàn)證電路在不同電源和環(huán)境條件下的工作情況。這可以幫助檢查電路對(duì)電源噪聲、溫度變化等因素的魯棒性。

仿真結(jié)果分析和調(diào)試:在仿真過(guò)程中,需要對(duì)仿真結(jié)果進(jìn)行分析和調(diào)試。如果發(fā)現(xiàn)電路的功能或時(shí)序不符合設(shè)計(jì)要求,需要進(jìn)行錯(cuò)誤定位和修復(fù)。

數(shù)字驗(yàn)證:數(shù)字驗(yàn)證是在邏輯仿真的基礎(chǔ)上,使用專門的驗(yàn)證工具進(jìn)行驗(yàn)證。數(shù)字驗(yàn)證可以通過(guò)隨機(jī)測(cè)試、形式驗(yàn)證、覆蓋率分析等方法,對(duì)電路的功能進(jìn)行全面驗(yàn)證。

仿真驗(yàn)證報(bào)告:最后,根據(jù)邏輯仿真和數(shù)字驗(yàn)證的結(jié)果,生成仿真驗(yàn)證報(bào)告。報(bào)告中包括了驗(yàn)證計(jì)劃、測(cè)試用例、仿真結(jié)果和分析等內(nèi)容,用于記錄和交流驗(yàn)證過(guò)程和結(jié)果。

邏輯仿真和數(shù)字驗(yàn)證在芯片設(shè)計(jì)中起著至關(guān)重要的作用,它可以幫助設(shè)計(jì)人員發(fā)現(xiàn)和解決電路設(shè)計(jì)中的問(wèn)題,確保芯片的功能和性能滿足設(shè)計(jì)要求。通過(guò)邏輯仿真和數(shù)字驗(yàn)證,可以提高芯片設(shè)計(jì)的可靠性和效率,減少后續(xù)芯片制造和測(cè)試的成本和風(fēng)險(xiǎn)。 ?

2.4 后端設(shè)計(jì)與仿真

芯片的后端設(shè)計(jì)與仿真是指在芯片設(shè)計(jì)流程中,將前端設(shè)計(jì)完成的電路布局、布線和物理實(shí)現(xiàn)等工作。這個(gè)階段主要包括以下幾個(gè)步驟: ?

物理設(shè)計(jì)規(guī)劃:根據(jù)設(shè)計(jì)需求和約束,制定物理設(shè)計(jì)規(guī)劃,確定芯片的布局和布線風(fēng)格,以及各個(gè)模塊的位置和大小等。

布局設(shè)計(jì):將電路的邏輯元件按照物理規(guī)劃的要求進(jìn)行布局,確定各個(gè)模塊的相對(duì)位置和大小。布局設(shè)計(jì)要考慮電路的性能、功耗、面積和可靠性等因素。

布線設(shè)計(jì):根據(jù)布局設(shè)計(jì)結(jié)果,進(jìn)行電路的布線,將各個(gè)邏輯元件之間的連線完成。布線設(shè)計(jì)要考慮信號(hào)延遲、功耗、電磁兼容性等因素。

物理驗(yàn)證:對(duì)布局和布線進(jìn)行物理驗(yàn)證,確保電路的布局和布線滿足設(shè)計(jì)規(guī)范和約束。物理驗(yàn)證包括電氣規(guī)則檢查(DRC)、布局規(guī)則檢查(LVS)等。

時(shí)序分析:對(duì)芯片進(jìn)行時(shí)序分析,確保電路的時(shí)序滿足設(shè)計(jì)要求。時(shí)序分析包括時(shí)序約束的制定和時(shí)序模擬等。

功耗分析:對(duì)芯片進(jìn)行功耗分析,評(píng)估芯片的功耗性能,并進(jìn)行功耗優(yōu)化。功耗分析包括靜態(tài)功耗和動(dòng)態(tài)功耗的評(píng)估。

仿真驗(yàn)證:對(duì)芯片進(jìn)行各種仿真,驗(yàn)證電路的功能和性能。仿真驗(yàn)證包括功能仿真、時(shí)序仿真、功耗仿真等。

物理優(yōu)化:根據(jù)仿真和驗(yàn)證結(jié)果,對(duì)芯片進(jìn)行物理優(yōu)化,改進(jìn)電路的性能、功耗和面積等。物理優(yōu)化包括布局優(yōu)化和布線優(yōu)化等。

芯片的后端設(shè)計(jì)與仿真是芯片設(shè)計(jì)流程中非常重要的一環(huán),它確保了芯片的物理實(shí)現(xiàn)滿足設(shè)計(jì)要求和約束。通過(guò)物理設(shè)計(jì)和仿真驗(yàn)證,可以評(píng)估和改進(jìn)芯片的性能、功耗和可靠性等,最終實(shí)現(xiàn)高質(zhì)量的芯片產(chǎn)品。

2.5 流片與ECO設(shè)計(jì)修改

芯片設(shè)計(jì)的流片是指將芯片設(shè)計(jì)轉(zhuǎn)化為實(shí)際的物理布局和連線,生成布局圖和掩膜數(shù)據(jù),以便進(jìn)行芯片制造。流片的過(guò)程包括以下幾個(gè)主要步驟: ?

物理設(shè)計(jì)規(guī)劃:確定芯片的布局約束和分區(qū),包括芯片的核心區(qū)域、輸入輸出引腳位置、電源和地線分布等。

布局設(shè)計(jì):根據(jù)物理設(shè)計(jì)規(guī)劃,將芯片的各個(gè)功能模塊進(jìn)行布局,包括放置模塊、調(diào)整模塊間的距離和相對(duì)位置,以滿足性能和功耗要求。

連線設(shè)計(jì):在布局的基礎(chǔ)上,進(jìn)行模塊間的連線設(shè)計(jì),包括信號(hào)線和電源線的布線,以及時(shí)鐘網(wǎng)絡(luò)的布線,以滿足信號(hào)完整性和時(shí)序要求。

特殊設(shè)計(jì):針對(duì)特殊模塊和特殊要求,進(jìn)行特殊設(shè)計(jì),如模擬電路的布局和連線、高速接口的布線等。

布局優(yōu)化:對(duì)布局進(jìn)行優(yōu)化,包括減小面積、減小功耗、減小時(shí)延等,以提高芯片的性能和可靠性。

掩膜生成:根據(jù)布局和連線設(shè)計(jì),生成掩膜數(shù)據(jù),用于芯片制造。

ECO(Engineering Change Order)設(shè)計(jì)修改是在芯片設(shè)計(jì)流片后,發(fā)現(xiàn)需要進(jìn)行修改或修正的情況下進(jìn)行的設(shè)計(jì)調(diào)整。ECO設(shè)計(jì)修改的目的是解決芯片設(shè)計(jì)中的問(wèn)題或改進(jìn)設(shè)計(jì)的性能和功能。ECO設(shè)計(jì)修改的步驟包括以下幾個(gè)主要過(guò)程: ?

問(wèn)題分析:分析芯片設(shè)計(jì)中的問(wèn)題或需要改進(jìn)的地方,確定需要進(jìn)行的設(shè)計(jì)修改。

設(shè)計(jì)調(diào)整:根據(jù)問(wèn)題分析的結(jié)果,進(jìn)行相應(yīng)的設(shè)計(jì)調(diào)整,包括修改布局、優(yōu)化連線、調(diào)整電源和地線等。

驗(yàn)證和仿真:對(duì)設(shè)計(jì)修改后的芯片進(jìn)行驗(yàn)證和仿真,以確保修改后的設(shè)計(jì)滿足要求,并解決之前的問(wèn)題。

評(píng)估和驗(yàn)證:對(duì)修改后的設(shè)計(jì)進(jìn)行評(píng)估和驗(yàn)證,包括性能評(píng)估、功耗評(píng)估、時(shí)序驗(yàn)證等。

掩膜生成:根據(jù)修改后的設(shè)計(jì),生成新的掩膜數(shù)據(jù),用于芯片制造。

ECO設(shè)計(jì)修改是芯片設(shè)計(jì)的一個(gè)重要環(huán)節(jié),它可以解決設(shè)計(jì)中的問(wèn)題和改進(jìn)設(shè)計(jì)的性能和功能,提高芯片的質(zhì)量和可靠性。同時(shí),ECO設(shè)計(jì)修改也需要考慮成本和時(shí)間的因素,以確保設(shè)計(jì)的修改是可行和有效的。

2.6 回片測(cè)試與EVB功能驗(yàn)證

芯片的回片測(cè)試是指在芯片制造完成后,對(duì)芯片進(jìn)行測(cè)試和驗(yàn)證的過(guò)程。回片測(cè)試的目的是檢測(cè)芯片的功能、性能和可靠性,以確保芯片符合設(shè)計(jì)規(guī)格和要求。回片測(cè)試的步驟包括以下幾個(gè)主要過(guò)程: ?

芯片封裝:將芯片進(jìn)行封裝,即將芯片芯片和引腳連接封裝在封裝材料中,以便進(jìn)行測(cè)試和使用。

測(cè)試計(jì)劃制定:根據(jù)芯片的設(shè)計(jì)規(guī)格和要求,制定測(cè)試計(jì)劃,確定測(cè)試的目標(biāo)、方法和流程。

芯片測(cè)試:使用測(cè)試設(shè)備和工具,對(duì)芯片進(jìn)行各種測(cè)試,包括功能測(cè)試、性能測(cè)試、電氣特性測(cè)試等。

數(shù)據(jù)分析:對(duì)測(cè)試結(jié)果進(jìn)行數(shù)據(jù)分析和處理,評(píng)估芯片的性能和可靠性,檢測(cè)是否存在缺陷或問(wèn)題。

故障排除:如果在測(cè)試中發(fā)現(xiàn)問(wèn)題或故障,進(jìn)行故障排除,確定問(wèn)題的原因,并進(jìn)行修復(fù)或調(diào)整。

測(cè)試報(bào)告:根據(jù)測(cè)試結(jié)果,生成測(cè)試報(bào)告,記錄芯片的測(cè)試情況和結(jié)果,以便后續(xù)的評(píng)估和驗(yàn)證。

EVB(Evaluation Board)功能驗(yàn)證是在芯片設(shè)計(jì)完成后,使用評(píng)估板對(duì)芯片的功能進(jìn)行驗(yàn)證和評(píng)估的過(guò)程。EVB是一個(gè)包含芯片和相關(guān)電路的開(kāi)發(fā)板,可以提供電源、時(shí)鐘和接口等功能,以便進(jìn)行芯片的功能驗(yàn)證和性能評(píng)估。EVB功能驗(yàn)證的步驟包括以下幾個(gè)主要過(guò)程: ?

硬件連接:將芯片連接到評(píng)估板上,包括電源連接、引腳連接、信號(hào)線連接等。

軟件配置:根據(jù)芯片的設(shè)計(jì)規(guī)格和要求,配置評(píng)估板的軟件,包括時(shí)鐘配置、寄存器設(shè)置等。

功能驗(yàn)證:使用評(píng)估板提供的接口和功能,對(duì)芯片的各個(gè)功能進(jìn)行驗(yàn)證,包括輸入輸出功能、通信功能、存儲(chǔ)功能等。

性能評(píng)估:通過(guò)評(píng)估板的測(cè)試和測(cè)量,對(duì)芯片的性能進(jìn)行評(píng)估,包括功耗、速度、時(shí)延等。

數(shù)據(jù)分析:對(duì)功能驗(yàn)證和性能評(píng)估的結(jié)果進(jìn)行數(shù)據(jù)分析和處理,評(píng)估芯片的功能和性能是否滿足設(shè)計(jì)要求。

驗(yàn)證報(bào)告:根據(jù)功能驗(yàn)證和性能評(píng)估的結(jié)果,生成驗(yàn)證報(bào)告,記錄芯片的驗(yàn)證情況和結(jié)果,以便后續(xù)的評(píng)估和驗(yàn)證。

EVB功能驗(yàn)證是在芯片設(shè)計(jì)完成后,對(duì)芯片的功能和性能進(jìn)行初步驗(yàn)證和評(píng)估的重要環(huán)節(jié),它可以幫助設(shè)計(jì)團(tuán)隊(duì)了解芯片的工作情況和性能表現(xiàn),為后續(xù)的調(diào)整和優(yōu)化提供指導(dǎo)和依據(jù)。 ?

2.7 CP測(cè)試

CP測(cè)試是指芯片的Chip Probe測(cè)試,也稱為芯片探針測(cè)試。它是在芯片制造過(guò)程中的一個(gè)關(guān)鍵步驟,用于驗(yàn)證芯片的電氣特性和功能是否符合設(shè)計(jì)規(guī)格和要求。 ? CP測(cè)試通常在芯片封裝之前進(jìn)行,它涉及以下主要步驟: ?

芯片準(zhǔn)備:在CP測(cè)試之前,需要對(duì)芯片進(jìn)行準(zhǔn)備工作,包括去除芯片表面的污染物和氧化物,以確保良好的接觸性能。

探針制備:制備用于探測(cè)芯片引腳的探針。探針通常由細(xì)小的金屬針組成,可以與芯片引腳接觸并傳遞信號(hào)。

探針安裝:將探針安裝在探針卡上,探針卡是一個(gè)具有多個(gè)探針位置的載體,用于將探針與芯片引腳對(duì)齊。

探針測(cè)試:將芯片放置在測(cè)試臺(tái)上,將探針卡與芯片引腳對(duì)齊,并施加適當(dāng)?shù)膲毫Γ固结樑c芯片引腳接觸。然后,通過(guò)測(cè)試設(shè)備向芯片引腳發(fā)送測(cè)試信號(hào),并讀取響應(yīng)信號(hào),以驗(yàn)證芯片的電氣特性和功能。

數(shù)據(jù)分析:對(duì)探針測(cè)試的結(jié)果進(jìn)行數(shù)據(jù)分析和處理,評(píng)估芯片的電氣特性和功能是否符合設(shè)計(jì)規(guī)格和要求。

CP測(cè)試是芯片制造過(guò)程中的一個(gè)重要環(huán)節(jié),它可以幫助檢測(cè)和排除芯片制造過(guò)程中的缺陷和問(wèn)題,確保芯片的質(zhì)量和可靠性。同時(shí),CP測(cè)試也可以提供有關(guān)芯片的電氣特性和功能的重要信息,為后續(xù)的封裝和測(cè)試工作提供指導(dǎo)和依據(jù)。 ?

2.8 Bonding與封裝

Bonding是指將芯片與封裝基板之間進(jìn)行電連接的過(guò)程。它是將芯片的引腳與封裝基板上的金屬線(或稱為焊線)相連接的關(guān)鍵步驟。芯片bonding通常使用微焊接技術(shù),可以分為以下幾種常見(jiàn)的類型: ?

焊線鍵合(Wire Bonding):這是最常見(jiàn)的芯片bonding技術(shù)。它使用金屬線(通常是金或鋁)將芯片的引腳與封裝基板上的焊盤連接起來(lái)。焊線鍵合可以分為球形焊線鍵合(Ball Bonding)和楔形焊線鍵合(Wedge Bonding)兩種。

無(wú)線鍵合(Wireless Bonding):與焊線鍵合不同,無(wú)線鍵合使用無(wú)線連接器(Wireless Interconnects)將芯片的引腳與封裝基板上的焊盤連接起來(lái)。無(wú)線鍵合通常使用微彈簧或彈性接觸器來(lái)實(shí)現(xiàn)。

直接焊接(Flip Chip Bonding):這種bonding技術(shù)將芯片的引腳直接與封裝基板上的焊盤相連接。芯片被翻轉(zhuǎn)放置,使其引腳與焊盤對(duì)齊,并使用焊料將其連接起來(lái)。直接焊接可以提供更短的信號(hào)路徑和更好的電氣性能。

涂覆鍵合(Underfill Bonding):這是一種在焊線鍵合或直接焊接后使用的補(bǔ)充技術(shù)。涂覆鍵合使用特殊的填充材料(通常是環(huán)氧樹(shù)脂)填充芯片和封裝基板之間的空隙,以提供額外的機(jī)械支撐和保護(hù)。

Bonding是芯片封裝過(guò)程中非常重要的一步,它確保芯片能夠與封裝基板之間進(jìn)行可靠的電連接。不同的bonding技術(shù)適用于不同的應(yīng)用和封裝類型,選擇適合的bonding技術(shù)可以提高芯片的可靠性和性能。 ? 芯片封裝是將芯片封裝在外殼中,以保護(hù)芯片、提供引腳連接和散熱等功能的過(guò)程。封裝可以將芯片連接到外部電路和系統(tǒng)中,使其能夠正常工作。 ? 芯片封裝的主要目的包括以下幾個(gè)方面: ?

保護(hù)芯片:封裝可以提供物理保護(hù),防止芯片受到機(jī)械損傷、濕氣、灰塵等外部環(huán)境的影響。

引腳連接:封裝提供了芯片引腳與外部電路的連接接口,使芯片能夠與其他器件和系統(tǒng)進(jìn)行通信和交互。

散熱:封裝通常包含散熱結(jié)構(gòu),可以有效地散發(fā)芯片產(chǎn)生的熱量,保持芯片的溫度在安全范圍內(nèi)。

尺寸調(diào)整:封裝可以根據(jù)芯片的尺寸和要求進(jìn)行調(diào)整,使芯片適應(yīng)不同的應(yīng)用場(chǎng)景和設(shè)備。

標(biāo)識(shí)和標(biāo)簽:封裝可以在外部標(biāo)注芯片的型號(hào)、序列號(hào)和其他重要信息,方便識(shí)別和管理。

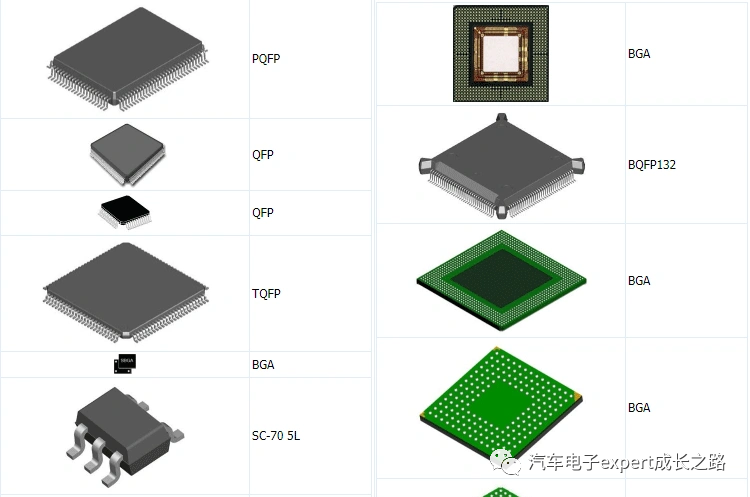

常見(jiàn)的芯片封裝類型包括: ?

DIP封裝(Dual Inline Package):雙列直插封裝,引腳通過(guò)兩行排列在封裝底部,適用于插入式安裝。

QFP封裝(Quad Flat Package):四邊平封裝,引腳通過(guò)四個(gè)邊緣排列,適用于表面貼裝安裝。

BGA封裝(Ball Grid Array):球柵陣列封裝,引腳通過(guò)底部的球形焊球排列,適用于高密度連接和散熱要求較高的芯片。

CSP封裝(Chip Scale Package):芯片尺寸封裝,封裝尺寸與芯片尺寸相近,適用于小型化和高集成度的芯片。

LGA封裝(Land Grid Array):焊盤陣列封裝,引腳通過(guò)底部的焊盤排列,適用于高密度連接和散熱要求較高的芯片。

不同的芯片封裝類型適用于不同的應(yīng)用場(chǎng)景和需求,選擇適合的封裝類型對(duì)于芯片的性能、可靠性和生產(chǎn)成本都有重要影響。 ?

2.9 FT測(cè)試與老化測(cè)試(Burn-In)

芯片的FT測(cè)試(Final Test)是在芯片制造完成后的最后階段進(jìn)行的測(cè)試,通常由ATE設(shè)備完成,用于驗(yàn)證芯片的電氣特性和功能是否符合設(shè)計(jì)規(guī)格和要求。FT測(cè)試通常包括以下幾個(gè)方面:

電氣特性測(cè)試:通過(guò)向芯片引腳發(fā)送測(cè)試信號(hào),并讀取響應(yīng)信號(hào),來(lái)檢測(cè)芯片的電氣特性,如電壓、電流、頻率等。

功能測(cè)試:通過(guò)向芯片發(fā)送不同的輸入信號(hào),檢測(cè)芯片的各個(gè)功能模塊是否正常工作,如邏輯門、存儲(chǔ)器、模擬電路等。

時(shí)序測(cè)試:測(cè)試芯片的時(shí)序特性,如時(shí)鐘頻率、信號(hào)傳輸延遲等,以確保芯片在正常工作頻率下能夠正確運(yùn)行。

溫度測(cè)試:在不同溫度條件下測(cè)試芯片的性能和可靠性,以評(píng)估芯片在各種工作環(huán)境下的表現(xiàn)。

可靠性測(cè)試:測(cè)試芯片在長(zhǎng)時(shí)間持續(xù)工作或特定工作條件下的可靠性,如溫度循環(huán)測(cè)試、濕熱循環(huán)測(cè)試等。

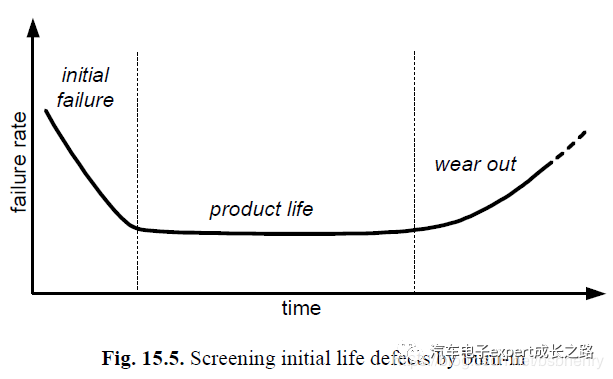

根據(jù)著名的硅基半導(dǎo)體器件使用生命周期的失效率的浴盆曲線,老化測(cè)試(Burn-In)是對(duì)芯片進(jìn)行一定時(shí)間的高溫和高負(fù)載運(yùn)行,以模擬芯片在實(shí)際使用中的工作環(huán)境,以提前篩選出潛在的故障和可靠性問(wèn)題。老化測(cè)試可以幫助排除芯片制造過(guò)程中的缺陷和問(wèn)題,提高芯片的可靠性和壽命。

老化測(cè)試通常包括以下幾個(gè)步驟: ?

加熱:將芯片放置在高溫環(huán)境中,通常溫度范圍為80℃至125℃,持續(xù)時(shí)間通常為幾十小時(shí)至幾百小時(shí)。

負(fù)載運(yùn)行:在高溫環(huán)境下,給芯片施加高負(fù)載,使其在高溫和高壓力下工作,以加速潛在故障的發(fā)生。

測(cè)試:在老化過(guò)程中,定期對(duì)芯片進(jìn)行測(cè)試,檢測(cè)是否出現(xiàn)故障或性能下降。

故障分析:如果出現(xiàn)故障或性能下降,進(jìn)行故障分析,找出問(wèn)題的原因,并進(jìn)行修復(fù)或淘汰。

老化測(cè)試對(duì)于芯片的可靠性評(píng)估和質(zhì)量控制起著重要作用,可以提前發(fā)現(xiàn)潛在的故障和可靠性問(wèn)題,降低芯片在實(shí)際使用中的故障率。 ? 對(duì)于車規(guī)芯片,特別是車規(guī)MCU芯片來(lái)說(shuō),要保證其10~15年的使用壽命,Burn-In老化測(cè)試是必須要做的。 ?

2.10 AEC-Q100可靠性測(cè)試

AEC-Q100是由汽車電子委員會(huì)(Automotive Electronics Council)制定的一項(xiàng)可靠性測(cè)試標(biāo)準(zhǔn),用于評(píng)估和驗(yàn)證汽車電子芯片的可靠性和適應(yīng)性。這項(xiàng)標(biāo)準(zhǔn)包括了多個(gè)測(cè)試項(xiàng)目和要求,以確保芯片在汽車環(huán)境中的長(zhǎng)期可靠性和穩(wěn)定性。 ? AEC-Q100可靠性測(cè)試通常包括以下幾個(gè)方面: ?

溫度循環(huán)測(cè)試(Temperature Cycling):將芯片在高溫和低溫之間循環(huán)變化,以模擬汽車在不同氣候條件下的工作環(huán)境。測(cè)試過(guò)程中,芯片需要在不同溫度下進(jìn)行正常工作,并檢測(cè)是否出現(xiàn)性能下降或故障。

濕熱循環(huán)測(cè)試(Humidity Testing):將芯片暴露在高溫和高濕度的環(huán)境中,以模擬汽車在潮濕和高溫環(huán)境下的工作條件。測(cè)試過(guò)程中,芯片需要在高濕度環(huán)境下進(jìn)行正常工作,并檢測(cè)是否出現(xiàn)性能下降或故障。

靜電放電測(cè)試(Electrostatic Discharge Testing):通過(guò)向芯片施加靜電放電,模擬人體靜電放電對(duì)芯片的影響。測(cè)試過(guò)程中,芯片需要能夠承受一定程度的靜電放電,并不出現(xiàn)性能下降或故障。

電壓波動(dòng)測(cè)試(Voltage Variation Testing):在芯片正常工作的電壓范圍內(nèi),模擬電源電壓的波動(dòng)和變化。測(cè)試過(guò)程中,芯片需要能夠正常工作,并不出現(xiàn)性能下降或故障。

機(jī)械沖擊和振動(dòng)測(cè)試(Mechanical Shock and Vibration Testing):通過(guò)施加機(jī)械沖擊和振動(dòng),模擬汽車在不同道路條件下的工作環(huán)境。測(cè)試過(guò)程中,芯片需要能夠承受一定程度的沖擊和振動(dòng),并不出現(xiàn)性能下降或故障。

可靠性評(píng)估和故障分析:對(duì)于經(jīng)過(guò)上述測(cè)試的芯片,進(jìn)行可靠性評(píng)估和故障分析,找出潛在的問(wèn)題和故障原因,并進(jìn)行修復(fù)或淘汰。

AEC-Q100可靠性測(cè)試對(duì)于汽車芯片的可靠性評(píng)估和質(zhì)量控制起著重要作用,確保芯片在汽車環(huán)境中的長(zhǎng)期可靠性和穩(wěn)定性,提高汽車電子系統(tǒng)的性能和安全性。 ?

2.11 小批量出貨(SOP)

小批量出貨(Small Volume Production)指的是以小規(guī)模的數(shù)量進(jìn)行芯片生產(chǎn)和出貨。相對(duì)于大規(guī)模生產(chǎn),小批量出貨通常適用于市場(chǎng)需求較小或新產(chǎn)品的初期階段。小批量出貨可以幫助廠商在產(chǎn)品開(kāi)發(fā)和市場(chǎng)驗(yàn)證階段進(jìn)行測(cè)試和調(diào)整,同時(shí)降低庫(kù)存風(fēng)險(xiǎn)和成本。 ? 在芯片的小批量出貨過(guò)程中,廠商會(huì)根據(jù)客戶的需求和訂單量,進(jìn)行相應(yīng)的生產(chǎn)和組裝。這包括芯片的制造、封裝、測(cè)試和質(zhì)量控制等環(huán)節(jié)。小批量出貨的周期通常較短,可以更快地滿足客戶的需求。 ? 需要注意的是,小批量出貨相對(duì)于大規(guī)模生產(chǎn)來(lái)說(shuō),成本較高。這是因?yàn)樵谛∨可a(chǎn)中,生產(chǎn)設(shè)備的利用率較低,而且沒(méi)有大規(guī)模生產(chǎn)的經(jīng)濟(jì)規(guī)模效應(yīng)。因此,小批量出貨的價(jià)格可能會(huì)較高,但可以提供更靈活和定制化的服務(wù)。 ? 芯片的小批量出貨是指以較小規(guī)模的數(shù)量進(jìn)行芯片生產(chǎn)和出貨,適用于市場(chǎng)需求較小或新產(chǎn)品的初期階段。這可以幫助廠商進(jìn)行產(chǎn)品測(cè)試和調(diào)整,同時(shí)降低庫(kù)存風(fēng)險(xiǎn)和成本。 ?

2.12 量產(chǎn)

芯片量產(chǎn)是指在經(jīng)過(guò)開(kāi)發(fā)、驗(yàn)證和小批量生產(chǎn)后,將芯片進(jìn)行大規(guī)模生產(chǎn)和出貨的過(guò)程。量產(chǎn)階段是將芯片從實(shí)驗(yàn)室和小規(guī)模生產(chǎn)轉(zhuǎn)變?yōu)樯虡I(yè)化產(chǎn)品的重要階段。 ? 在芯片量產(chǎn)之前,通常需要進(jìn)行以下幾個(gè)步驟: ?

設(shè)計(jì)驗(yàn)證和測(cè)試:在小批量生產(chǎn)之前,需要對(duì)芯片的設(shè)計(jì)進(jìn)行驗(yàn)證和測(cè)試,確保其功能和性能符合要求。這包括電氣測(cè)試、功能測(cè)試、時(shí)序測(cè)試等。

工藝開(kāi)發(fā)和優(yōu)化:在量產(chǎn)之前,需要對(duì)芯片的制造工藝進(jìn)行開(kāi)發(fā)和優(yōu)化,以確保生產(chǎn)過(guò)程的穩(wěn)定性和可靠性。這包括制造流程的優(yōu)化、工藝參數(shù)的調(diào)整等。

設(shè)備采購(gòu)和準(zhǔn)備:量產(chǎn)需要大量的生產(chǎn)設(shè)備和工具,包括芯片制造設(shè)備、封裝設(shè)備、測(cè)試設(shè)備等。在量產(chǎn)之前,需要進(jìn)行設(shè)備的采購(gòu)和準(zhǔn)備工作。

生產(chǎn)規(guī)劃和調(diào)度:在量產(chǎn)之前,需要進(jìn)行生產(chǎn)規(guī)劃和調(diào)度,包括生產(chǎn)線的布局、生產(chǎn)工藝的流程設(shè)計(jì)、生產(chǎn)資源的分配等。這有助于確保生產(chǎn)過(guò)程的高效性和穩(wěn)定性。

質(zhì)量控制和測(cè)試:在量產(chǎn)過(guò)程中,需要進(jìn)行質(zhì)量控制和測(cè)試,以確保芯片的品質(zhì)符合要求。這包括過(guò)程控制、出貨檢測(cè)、可靠性測(cè)試等。

一旦以上步驟完成,芯片就可以進(jìn)入量產(chǎn)階段。在量產(chǎn)過(guò)程中,芯片將按照客戶的需求進(jìn)行大規(guī)模生產(chǎn)和出貨。這包括芯片的制造、封裝、測(cè)試、質(zhì)量控制等環(huán)節(jié)。量產(chǎn)的周期通常較長(zhǎng),可以滿足市場(chǎng)的大規(guī)模需求。 ? 芯片量產(chǎn)是將芯片從小規(guī)模生產(chǎn)轉(zhuǎn)變?yōu)榇笠?guī)模生產(chǎn)和出貨的過(guò)程。在量產(chǎn)之前,需要進(jìn)行設(shè)計(jì)驗(yàn)證、工藝開(kāi)發(fā)、設(shè)備準(zhǔn)備、生產(chǎn)規(guī)劃和質(zhì)量控制等工作。量產(chǎn)階段將按照客戶需求進(jìn)行大規(guī)模生產(chǎn)和出貨。 ?

2.13 售后質(zhì)量分析(FA)

芯片的售后質(zhì)量分析(Failure Analysis,簡(jiǎn)稱FA)是一種通過(guò)對(duì)故障芯片進(jìn)行分析和調(diào)查,以確定故障原因并提供解決方案的過(guò)程。FA通常在芯片出現(xiàn)故障后進(jìn)行,旨在幫助廠商和客戶解決芯片質(zhì)量問(wèn)題,并改進(jìn)產(chǎn)品設(shè)計(jì)和制造過(guò)程。 ? 在進(jìn)行FA之前,通常需要進(jìn)行以下幾個(gè)步驟: ?

故障檢測(cè)和定位:首先需要對(duì)故障芯片進(jìn)行檢測(cè)和定位,以確定故障的具體位置和范圍。這可以通過(guò)電氣測(cè)試、物理分析和故障模式分析等方法來(lái)實(shí)現(xiàn)。

故障分析和調(diào)查:一旦確定了故障的位置和范圍,就需要進(jìn)行故障分析和調(diào)查,以確定故障的原因。這包括物理分析、化學(xué)分析、電路分析等方法,可以通過(guò)顯微鏡、掃描電子顯微鏡(SEM)、透射電子顯微鏡(TEM)、能譜分析儀(EDS)等儀器來(lái)支持分析。

數(shù)據(jù)分析和統(tǒng)計(jì):在進(jìn)行故障分析和調(diào)查時(shí),還需要對(duì)相關(guān)數(shù)據(jù)進(jìn)行分析和統(tǒng)計(jì),以確定故障的頻率、分布和影響范圍。這有助于了解故障的根本原因和潛在問(wèn)題。

解決方案提供:根據(jù)故障分析和調(diào)查的結(jié)果,可以提供相應(yīng)的解決方案。這可能包括產(chǎn)品設(shè)計(jì)的改進(jìn)、制造工藝的優(yōu)化、測(cè)試方法的改進(jìn)等。解決方案的目標(biāo)是避免類似故障的再次發(fā)生,并提高產(chǎn)品的可靠性和質(zhì)量。

芯片的售后質(zhì)量分析是通過(guò)對(duì)故障芯片進(jìn)行分析和調(diào)查,以確定故障原因并提供解決方案的過(guò)程。這包括故障檢測(cè)和定位、故障分析和調(diào)查、數(shù)據(jù)分析和統(tǒng)計(jì)、解決方案提供等步驟。FA的目標(biāo)是解決芯片質(zhì)量問(wèn)題,并改進(jìn)產(chǎn)品設(shè)計(jì)和制造過(guò)程。 ? 對(duì)于車規(guī)MCU芯片,每次FA,整車廠和Tier-1客戶都要求提供完整詳細(xì)8D報(bào)告,一點(diǎn)都不能馬虎!

2.14 DFT與DFM

DFT(Design for Testability)和DFM(Design for Manufacturing)是芯片設(shè)計(jì)中兩個(gè)重要的概念,它們旨在提高芯片的測(cè)試性和制造性。 ? DFT(Design for Testability)是指在芯片設(shè)計(jì)階段考慮測(cè)試的可行性和效率。DFT的目標(biāo)是設(shè)計(jì)出易于測(cè)試和故障定位的芯片,以提高測(cè)試的覆蓋率和效率,減少測(cè)試成本和時(shí)間。在DFT中,設(shè)計(jì)工程師會(huì)采用一些特殊的設(shè)計(jì)技術(shù)和結(jié)構(gòu),如掃描鏈(Scan Chain)、邊界掃描(Boundary Scan)、故障模式注入(Fault Model Injection)等,以方便測(cè)試人員對(duì)芯片進(jìn)行測(cè)試和故障定位。 ? DFM(Design for Manufacturing)是指在芯片設(shè)計(jì)階段考慮制造的可行性和效率。DFM的目標(biāo)是設(shè)計(jì)出易于制造和生產(chǎn)的芯片,以提高生產(chǎn)效率和降低制造成本。在DFM中,設(shè)計(jì)工程師會(huì)考慮到制造過(guò)程中的一些限制和要求,如工藝容差、布局規(guī)則、材料選擇等,以確保芯片的可制造性和可靠性。此外,DFM還包括對(duì)設(shè)計(jì)規(guī)則、設(shè)計(jì)布局和材料選擇等方面的優(yōu)化,以減少制造過(guò)程中的缺陷和不良。 ? DFT和DFM是芯片設(shè)計(jì)中的兩個(gè)重要概念,尤其是對(duì)于車規(guī)MCU這樣的高復(fù)雜度和高集成度芯片設(shè)計(jì)。DFT旨在提高芯片的測(cè)試性能和效率,減少測(cè)試成本和時(shí)間;DFM旨在提高芯片的制造性能和效率,降低制造成本。通過(guò)考慮DFT和DFM,設(shè)計(jì)工程師可以設(shè)計(jì)出更易于測(cè)試和制造的芯片,提高產(chǎn)品的質(zhì)量和競(jìng)爭(zhēng)力。 ?

車規(guī)MCU芯片的軟件開(kāi)發(fā)生態(tài)

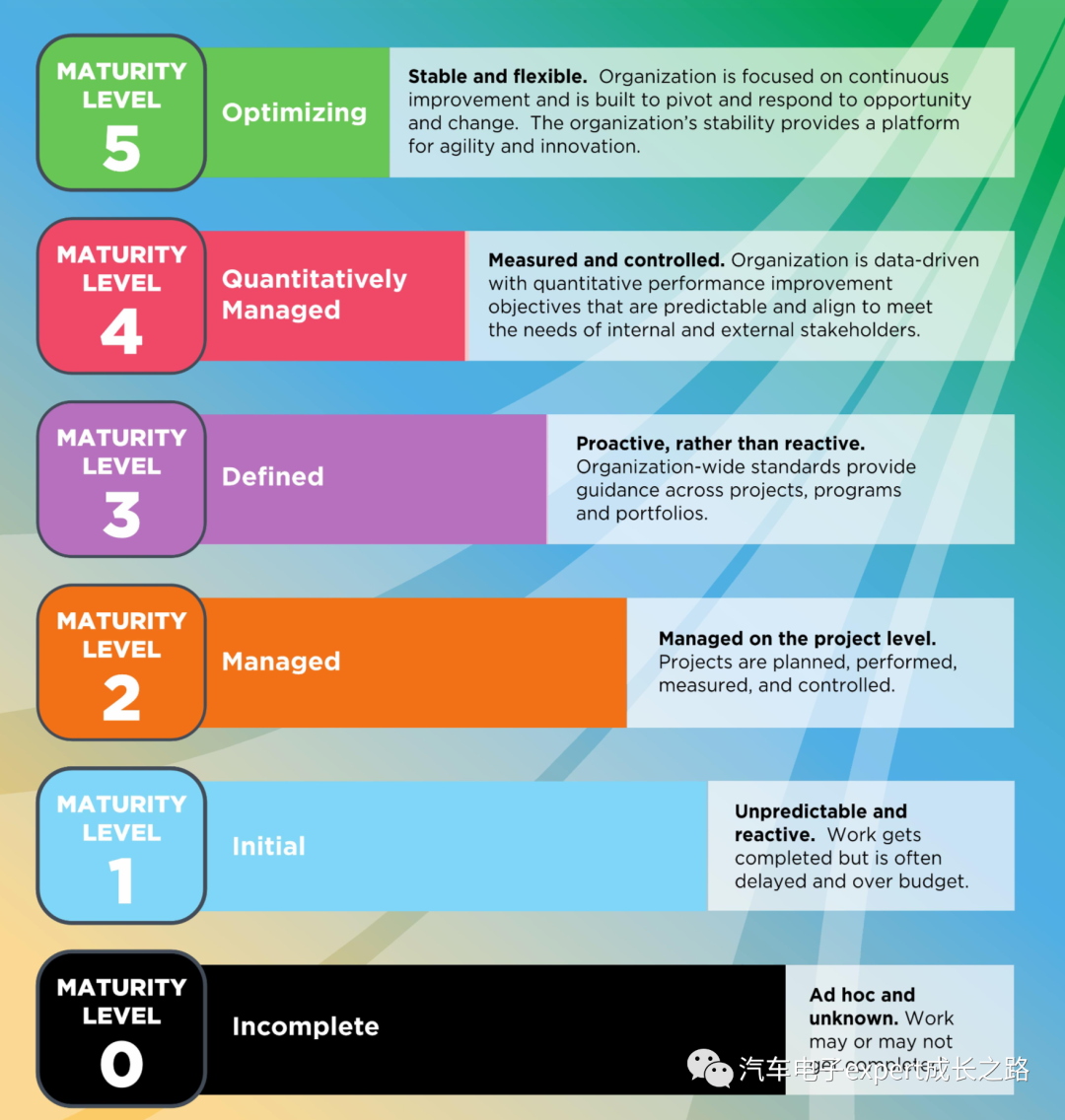

3.1 汽車軟件開(kāi)發(fā)流程--ASPIC與CMMI

CMMI是“能力成熟度模型集成”(Capability Maturity Model Integration)的縮寫,是一種用于評(píng)估和改進(jìn)組織的軟件和系統(tǒng)工程能力的模型。CMMI最初由美國(guó)國(guó)防部軟件工程研究所(SEI)開(kāi)發(fā),旨在幫助組織提高其軟件開(kāi)發(fā)和工程管理的能力,并提供一種評(píng)估和改進(jìn)的框架。 ? CMMI模型包括五個(gè)不同的成熟度級(jí)別,從初始級(jí)別(Level 1)到優(yōu)化級(jí)別(Level 5)。每個(gè)級(jí)別代表了組織在軟件和系統(tǒng)工程能力方面的不同水平和成熟度。通過(guò)使用CMMI模型,組織可以評(píng)估其當(dāng)前的能力水平,并采取適當(dāng)?shù)拇胧﹣?lái)改進(jìn)和提高其工程過(guò)程和實(shí)踐。

CMMI模型涵蓋了各個(gè)方面的軟件和系統(tǒng)工程能力,包括需求管理、項(xiàng)目管理、配置管理、過(guò)程管理、度量和分析等。它提供了一套標(biāo)準(zhǔn)的最佳實(shí)踐,幫助組織建立可重復(fù)和可持續(xù)的工程過(guò)程,并提供了一種評(píng)估和改進(jìn)的方法,以確保組織能夠按時(shí)、按質(zhì)地交付高質(zhì)量的軟件和系統(tǒng)。 ? ASPICE是“汽車軟件過(guò)程改進(jìn)與能力確定”(Automotive SPICE)的縮寫,是一種用于評(píng)估和改進(jìn)汽車軟件開(kāi)發(fā)過(guò)程的國(guó)際標(biāo)準(zhǔn)。ASPICE旨在提供一種評(píng)估和改進(jìn)汽車軟件開(kāi)發(fā)過(guò)程的框架,以確保高質(zhì)量和可靠性的汽車軟件。 ? ASPICE是由國(guó)際汽車工程師協(xié)會(huì)(INCOSE)和國(guó)際汽車制造商協(xié)會(huì)(AIAG)共同開(kāi)發(fā)的,它基于CMMI(能力成熟度模型集成)和ISO 15504(過(guò)程能力評(píng)估)的概念,專門針對(duì)汽車行業(yè)的軟件開(kāi)發(fā)進(jìn)行了定制。

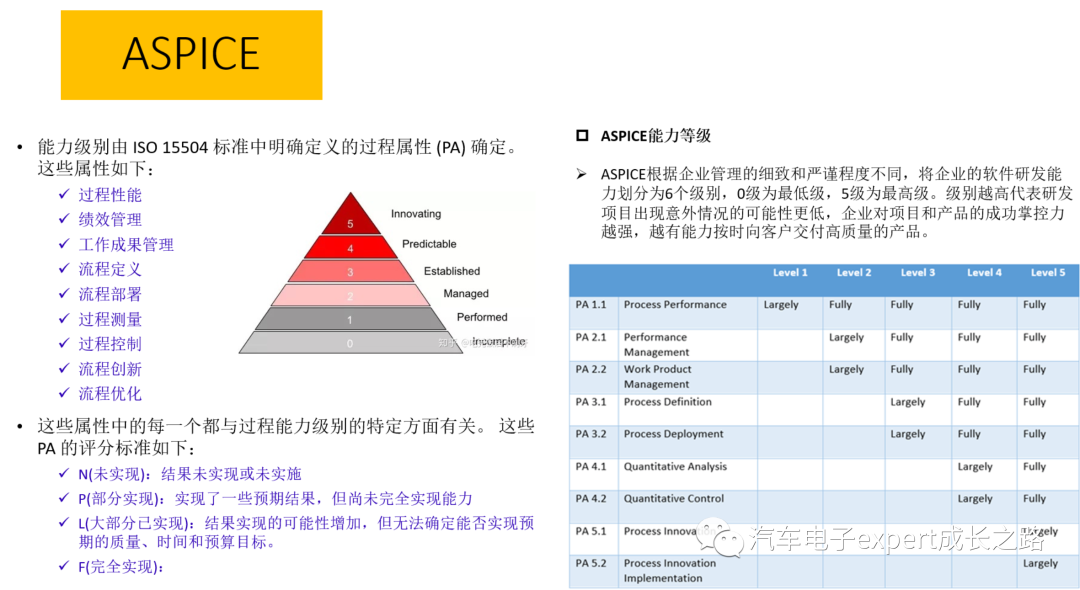

ASPICE模型包括六個(gè)不同的能力級(jí)別,從Level 0到Level 5。每個(gè)級(jí)別代表了軟件開(kāi)發(fā)過(guò)程的不同成熟度和能力水平。通過(guò)使用ASPICE模型,汽車制造商和供應(yīng)商可以評(píng)估其當(dāng)前的軟件開(kāi)發(fā)過(guò)程,并采取相應(yīng)的措施來(lái)改進(jìn)和提高其能力。

ASPICE模型涵蓋了軟件開(kāi)發(fā)過(guò)程的各個(gè)方面,包括需求管理、軟件架構(gòu)、軟件測(cè)試、配置管理、問(wèn)題解決等。它提供了一套標(biāo)準(zhǔn)的最佳實(shí)踐,幫助組織建立可重復(fù)和可持續(xù)的軟件開(kāi)發(fā)過(guò)程,并提供了一種評(píng)估和改進(jìn)的方法,以確保汽車軟件的高質(zhì)量和安全性。

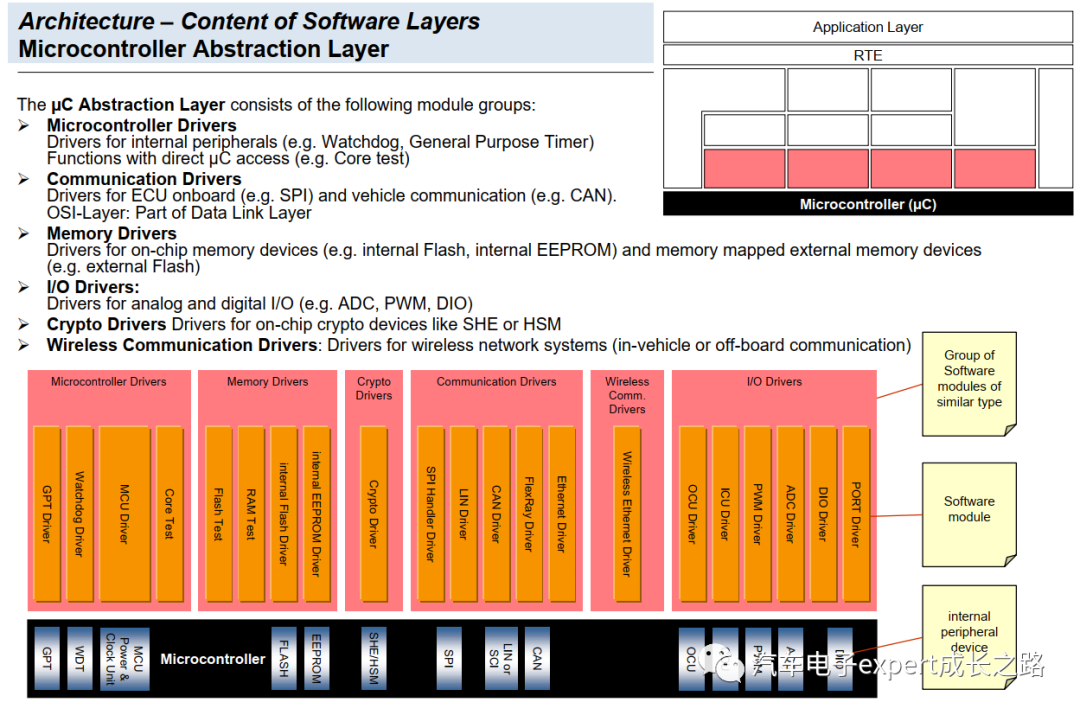

3.2 汽車開(kāi)放系統(tǒng)架構(gòu)--AUTOSAR MCAL

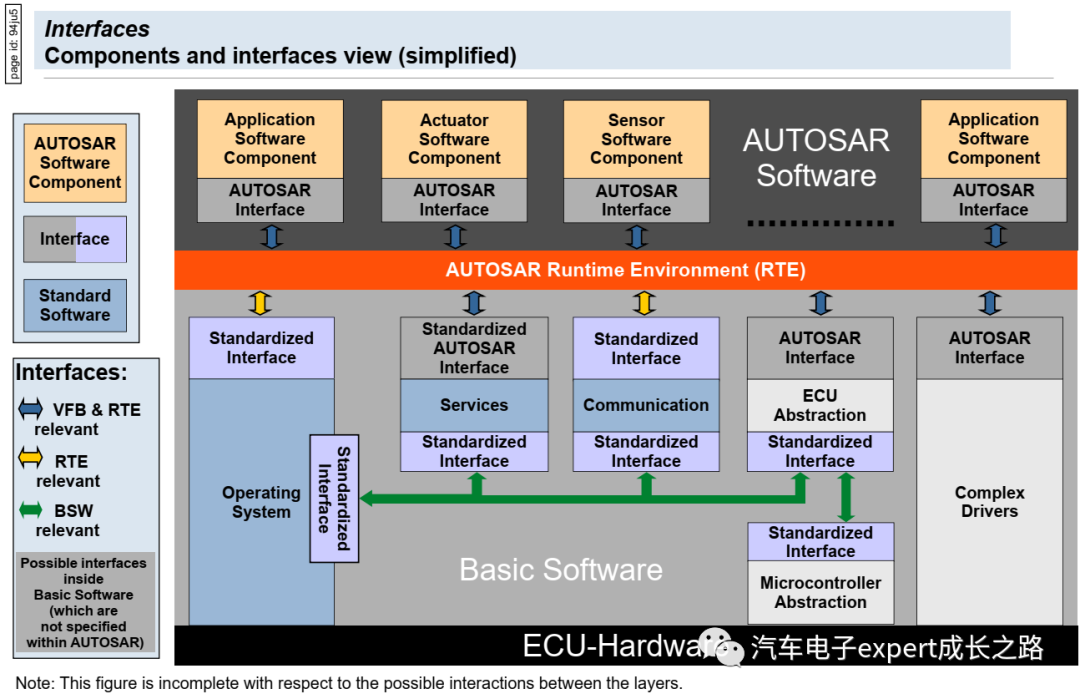

AUTOSAR是“汽車開(kāi)放系統(tǒng)架構(gòu)”(Automotive Open System Architecture)的縮寫,是一種用于汽車電子系統(tǒng)開(kāi)發(fā)的標(biāo)準(zhǔn)化架構(gòu)。AUTOSAR旨在提供一種統(tǒng)一的方法和規(guī)范,使汽車制造商和供應(yīng)商能夠更加高效地開(kāi)發(fā)和集成電子控制單元(ECU)。 ? AUTOSAR的目標(biāo)是實(shí)現(xiàn)汽車電子系統(tǒng)的模塊化、可重用性和互操作性。它定義了一套標(biāo)準(zhǔn)化的軟件組件、通信協(xié)議、接口和架構(gòu),以支持不同供應(yīng)商的軟件和硬件的集成。通過(guò)采用AUTOSAR,汽車制造商可以更容易地組裝和配置各種ECU,同時(shí)減少開(kāi)發(fā)時(shí)間和成本。

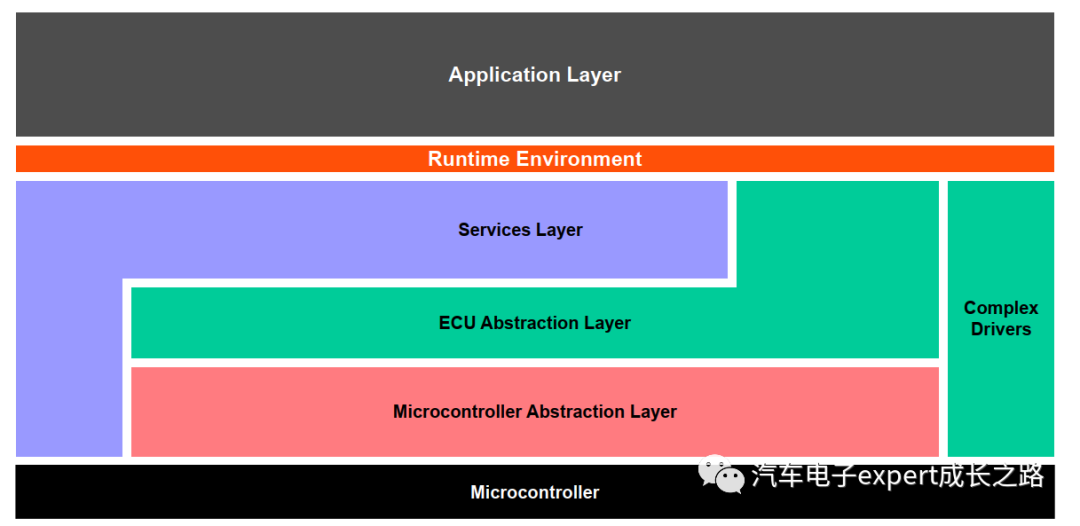

AUTOSAR架構(gòu)包括三個(gè)主要層次:應(yīng)用層(ASW)、運(yùn)行時(shí)環(huán)境層(RTE)和基礎(chǔ)軟件層(BSW)。應(yīng)用層定義了汽車功能和應(yīng)用軟件的規(guī)范,運(yùn)行時(shí)環(huán)境層提供了運(yùn)行和管理應(yīng)用軟件的基礎(chǔ)設(shè)施,基礎(chǔ)軟件層提供了與硬件和底層操作系統(tǒng)的接口。

通過(guò)采用AUTOSAR,汽車制造商可以實(shí)現(xiàn)軟件的模塊化和可重用性,提高開(kāi)發(fā)效率和質(zhì)量,并支持更快速的創(chuàng)新和功能擴(kuò)展。此外,AUTOSAR還為汽車行業(yè)提供了一種開(kāi)放的標(biāo)準(zhǔn)化平臺(tái),促進(jìn)了供應(yīng)商之間的合作和互操作性。 ? AUTOSAR BSW中的微控制器抽象層(MCAL)通常由車規(guī)MCU芯片公司提供,以作為MCU的外設(shè)的底層驅(qū)動(dòng)使用:

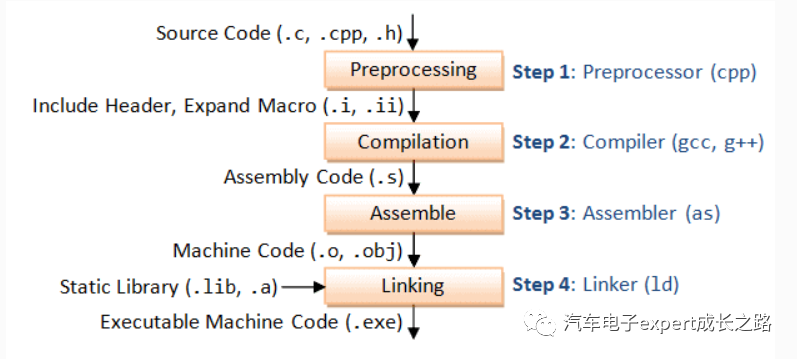

3.3 軟件開(kāi)發(fā)工具鏈(Toolchain)

MCU(Microcontroller Unit)軟件開(kāi)發(fā)工具鏈?zhǔn)怯糜陂_(kāi)發(fā)嵌入式系統(tǒng)的一系列工具和軟件。它包括以下幾個(gè)主要組成部分:

集成開(kāi)發(fā)環(huán)境(IDE):IDE是開(kāi)發(fā)嵌入式系統(tǒng)的核心工具,提供了代碼編輯、編譯、調(diào)試和部署等功能。常見(jiàn)的MCU軟件開(kāi)發(fā)IDE包括Keil MDK、IAR Embedded Workbench、Eclipse等。

編譯器:編譯器將高級(jí)語(yǔ)言(如C、C++)編寫的代碼轉(zhuǎn)換為機(jī)器語(yǔ)言,以便在MCU上執(zhí)行。常見(jiàn)的MCU編譯器有ARM GCC、Keil C Compiler、IAR C/C++ Compiler等。

調(diào)試器/仿真器:調(diào)試器/仿真器用于連接MCU并進(jìn)行調(diào)試和仿真操作。它提供了斷點(diǎn)調(diào)試、變量監(jiān)視、寄存器查看等功能,幫助開(kāi)發(fā)人員定位和解決問(wèn)題。常見(jiàn)的MCU調(diào)試器/仿真器有J-Link、ST-Link、Segger等。

代碼生成工具:代碼生成工具是一種可以自動(dòng)生成部分代碼的工具,可以提高開(kāi)發(fā)效率。例如,CubeMX是STMicroelectronics提供的一個(gè)代碼生成工具,可以自動(dòng)生成初始化代碼和驅(qū)動(dòng)程序。

靜態(tài)分析工具:靜態(tài)分析工具用于檢查代碼質(zhì)量和發(fā)現(xiàn)潛在的問(wèn)題,如代碼規(guī)范違規(guī)、內(nèi)存泄漏、未初始化變量等。常見(jiàn)的MCU靜態(tài)分析工具有Lint、Coverity等。

特定MCU的軟件庫(kù)和驅(qū)動(dòng)程序:MCU廠商通常提供特定MCU的軟件庫(kù)和驅(qū)動(dòng)程序,用于簡(jiǎn)化開(kāi)發(fā)過(guò)程。這些庫(kù)和驅(qū)動(dòng)程序提供了各種功能,如GPIO控制、定時(shí)器、串口通信等。

以上是MCU軟件開(kāi)發(fā)工具鏈的一些主要組成部分,不同的開(kāi)發(fā)項(xiàng)目和需求可能會(huì)有所不同。開(kāi)發(fā)人員可以根據(jù)自己的需求選擇適合的工具和軟件,以提高開(kāi)發(fā)效率和質(zhì)量。 ?

3.4 各種中間件軟件(Middleware)

針對(duì)汽車電子ECU和域控制器的應(yīng)用軟件開(kāi)發(fā),除了上面提到的SDK/AUTSOAR MCAL底層驅(qū)動(dòng)軟件,車規(guī)MCU廠家需要給整車廠和Tier-1客戶提供各種中間件軟件(Middleware),包括但不限于: ?

D-Flash模擬EEPROM軟件

信息安全固件(HSM Firmware)和安全啟動(dòng)(Secure Boot)

基于LIN/CAN(FD)/FlexRay車載通信總線的傳輸層協(xié)議(TP)/統(tǒng)一診斷服務(wù)(UDS)/參數(shù)標(biāo)定協(xié)議(XCP) stack

基于車載總線的應(yīng)用軟件升級(jí)(bootlodaer/FOTA)

基于車載以太網(wǎng)通信的時(shí)間敏感網(wǎng)絡(luò)(TSN)、DoIP診斷協(xié)議棧、面向服務(wù)架構(gòu)(SOA)

多核通信和同步(IPC)軟件

電機(jī)控制庫(kù)和參數(shù)標(biāo)定軟件

當(dāng)然,這其中很多中間件軟件也可以通過(guò)與第三方合作伙伴(3rd Partner)建立軟件生態(tài)的方式提供。比如NXP的軟件生態(tài)合作伙伴如下:

總結(jié)

本文只是拋磚引玉地概述了車規(guī)芯片的行業(yè)標(biāo)準(zhǔn)和為了保證可靠性和質(zhì)量所需的設(shè)計(jì)、研發(fā)、生產(chǎn)制造、封裝測(cè)試、應(yīng)用軟件開(kāi)發(fā)生態(tài)、售后失效分析各個(gè)環(huán)節(jié)的要求。后續(xù)我的《漫談車規(guī)MCU》系列公眾號(hào)文章將針對(duì)本文提到的每個(gè)車規(guī)芯片相關(guān)topic具體展開(kāi)介紹更多細(xì)節(jié),希望對(duì)大家和中國(guó)車規(guī)芯片的發(fā)展有所幫助。 ?

Enwei Hu(胡恩偉) ?

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論