SOPC(SystemOnProgrammableChip) 是用可編程邏輯技術把整個系統放到一片硅片上的一種特殊嵌入式系統一方面,它片上系統(SOC)完成整個系統的邏輯功能;另一方面,它是可編程系統,具有靈活的設計方式,可裁剪,擴充,升級,并具備軟硬件在系統可編程功能J.S)PC 是PID 和ASIC 技術融合的結果,可以認為SOPC代表了半導體產業未來的發展方向。本文采用EDA 軟件QuartuslI 中的SOPCBuilder 構建了一個SOPC 系統。并以構建的系統為平臺進行電子鐘的軟件設計:最后在Altera公司FPGA 多媒體開發平臺DE2 上進行實現該方案不同于基于處理器或控制器及SOC 的嵌入式系統,基于SOPC 的嵌入式系統具有可配置的特點,不會包括任何專用外設,而是可根據需要靈活地在一片FPGA 中構造外設接口。

電子鐘是一種用數字電子技術實現時、分、秒自然計時的裝置,與機械式時鐘相比具有更高的準確性和直觀性,而且使用壽命較長,與機械鐘相比具有更高的準確性和直觀性,具有更長的使用壽命,已得到廣泛的使用。數字鐘的設計方法有許多種,例如可用中小規模集成電路組成電子鐘,也可以利用專用的電子鐘芯片配以顯示電路及其所需要的外圍電路組成電子鐘,還可以利用單片機來實現電子鐘等等。這些方法都各有其特點,其中利用單片機實現的電子鐘具有編程靈活,以便于功能的擴展。

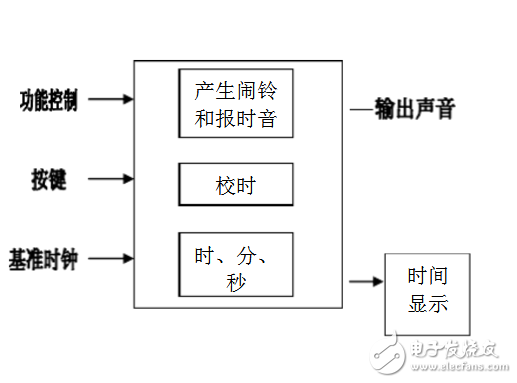

電子鐘設計原理

數字鐘的示意如下圖所示。它由石英晶體振蕩器、分頻器、計數器、譯碼器顯示器和校時電路組成。振蕩器產生穩定的高頻脈沖信號,作為數字鐘的時間基準,然后經過分頻器輸出標準秒脈沖。秒計數器滿60后向分計數器進位,分計數器滿60后向小時計數器進位,小時計數器按照“24翻1”規律計數。計數器的輸出分別經譯碼器送顯示器顯示。計時出現誤差時,可以用校時電路校時、校分。

電子鐘功能

1) 具有正確的時、分、秒計時功能。

2) 計時結果要用數碼管分別顯示進、分、秒的十位和個位。

3) 有校時功能。當S鍵按下時,分計數器以秒脈沖的速度遞增,并按60min循環,即

計數到期59min后再回到00。當工A鍵按下時,時計數器以秒脈沖的速度遞增,并按24h循環,即計數到23h后再回00。

4) 利用揚聲器整點報時。當計時到達59分59秒時開始報時,在59分50秒、52秒、54秒、56秒、58秒時鳴叫,鳴叫聲頻為500hz;到達59分60秒時為最后一聲整點報時,頻率為1khz。

控定時器的基本組成

數字鐘鐘控定時器由:計數器、D觸發器、數據選擇器、數據分配器、譯碼器、報時器、鬧時器組、分頻器和一個或非門這九大模塊構成。計數器主要分為24進制計數器和60進制計數器,24進制計數器對數字鐘的小時位計行計數,60進制對數字鐘的分和秒進行計數。D觸發器主要是用在對數字進行校準時的按鍵消抖作用,以免在校時的時候產生抖動信號。數據分配器的作用是在動態譯碼時選擇輸出數據。譯碼器對輸出信號進行譯碼在數碼管上顯示出來,讓大家數字鐘的表示直觀。報時電路是使時鐘在整點有報時功能而設計的。鬧時器是對時鐘進行比較產生鬧時電信號的電路。

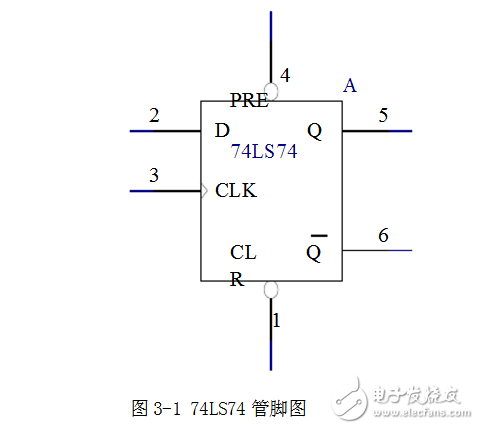

D觸發器的設計

在本設計中運用到了3個D觸發器,它主要是用在對數字進行校準時的按鍵消抖作用,以免在校時的時候產生抖動信號。

在電路中用到了D觸發器74LS74,74LS74的管腳圖如圖3-1。

觸發器,它是由門電路構成的邏輯電路,它的輸出具有兩個穩定的物理狀態(高電平和低電平),所以它能記憶一位二進制代碼。觸發器是存放在二進制信息的最基本的單元。按其功能可為基本RS觸發器觸、JK觸發器、D觸發器和T觸發器。

這幾種觸發器都有集成電路產品。其中應用最廣泛的當數JK觸發器和D觸發器。不過,深刻理解RS觸發器對全面掌握觸發器的工作方式或動作特點是至關重要的。事實上,JK觸發器和D觸發器是RS觸發器的改進型,其中JK觸發器保留了兩個數據輸入端,而D觸發器只保留了一個數據輸入端。D觸發器有邊沿D觸發器和高電平D觸發器。74LS74為一個電平D觸發器。

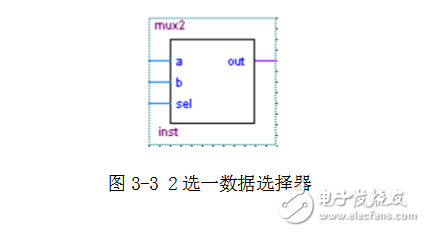

數據選擇器的設計

在多路數據傳送過程中,能夠根據需要將其中任意一路選出來的電路,叫做數據選擇器,也稱多路選擇器或多路開關。數據選擇器(MUX)的邏輯功能是在地址選擇信號的控制下,從多路數據中選擇一路數據作為輸出信號。

通過QuartusII軟件進行編譯后,仿真結果如圖3-2所示,

打包后成元器件如圖3-3所示;

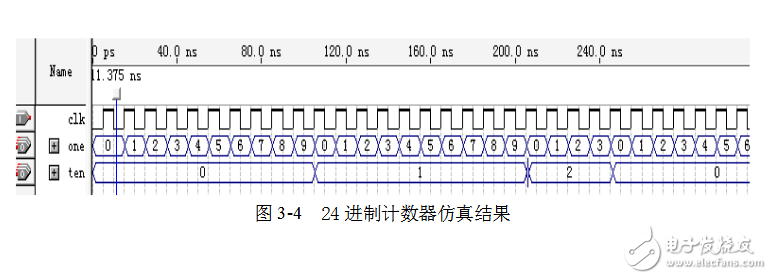

計數器的設計

計數器是一種計算輸入脈沖的時序邏輯網絡,被計數的輸入信號就是時序網絡的時鐘脈沖,它不僅可以計數而且還可以用來完成其他特定的邏輯功能,如測量、定時控制、數字運算等等。

數字鐘的計數電路是用兩個六十進制計數電路和“24進制”計數電路實現的。數字鐘的計數電路的設計可以用反饋清零法。當計數器正常計數時,反饋門不起作用,只有當進位脈沖到來時,反饋信號將計數電路清零,實現相應模的循環計數。以六十進制為例,當計數器從00,01,02,……,59計數時,反饋門不起作用,只有當第60個秒脈沖到來時,反饋信號隨即將計數電路清零,實現模為60的循環計數。

下面是用Verilog HDL語言編寫的24進制、60進制計數器的程序代碼: 1)24進制計數器程序代碼;

module count24(ten,one,clk); output[3:0] ten,one; input clk;

reg[3:0] ten,one; always @(posedge clk) begin

if(ten[3:0]==2&&one[3:0]==3) begin

ten[3:0]《=0; one[3:0]《=0; end

else if(one[3:0]==9) begin

one[3:0]《=0;

ten[3:0]《=ten[3:0]+1; end else

one[3:0]《=one[3:0]+1; end

endmodule

通過QuartusII軟件進行編譯后,仿真結果如圖3-4所示,

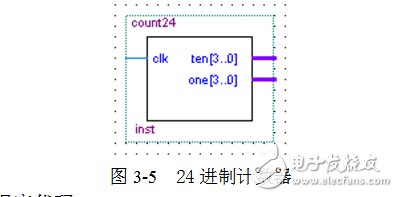

打包后成元器件如圖3-5所示;

60進制計數器程序代碼;

module count60(cout,ten,one,clk); output[3:0] ten,one; output cout; input clk;

reg[3:0] ten,one; always @(posedge clk) begin

if(one[3:0]==9) begin

one[3:0]《=0; if(ten[3:0]==5) ten[3:0]《=0; else

ten[3:0]《=ten[3:0]+1; end else

one[3:0]《=one[3:0]+1; end

assign cout=(ten[3:0]==0&&one[3:0]==0)?1:0; endmodule

通過QuartusII軟件進行編譯后,仿真結果如圖3-6所示;

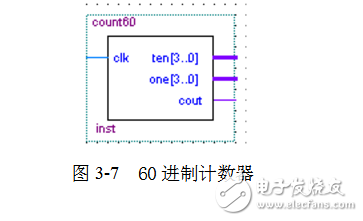

打包后成元器件如圖3-7所示

數據分配器

能夠將1個輸入數據,根據需要傳送到m個輸出端的任何一個輸出端的電路,叫做數據分配器,又稱為多路分配器,其邏輯功能正好與數據選擇器相反。電路結構:由與門組成的陣列。分類:1路-4路數據分配器(如74LS139)、1路-8路數據分配器(74LS138)等。由于譯碼器和數據分配器的功能非常接近,所以譯碼器一個很重要的應用就是構成數據分配器。 也正因為如此,市場上沒有集成數據分配器產品,只有集成譯碼器產品。

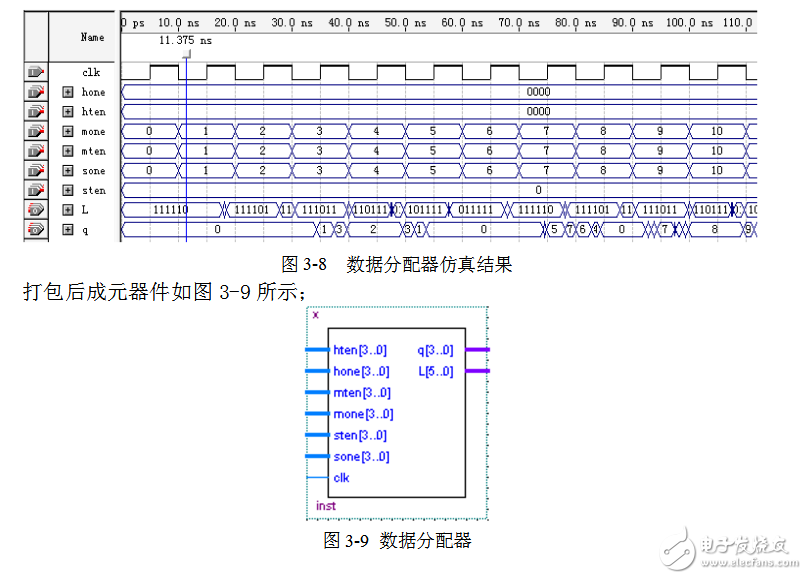

通過QuartusII軟件進行編譯后,仿真結果如圖3-8所示;

譯碼器

譯碼器是一個多輸入、多輸出的組合邏輯電路。它的工作是把給定的代碼進行“翻譯”,變成相應的狀態,使輸出通道中相應的一路有信號輸出。譯碼器在數字系統中有廣泛的用途,不僅用于代碼的轉換、終端的數字顯示,還用于數字分配,存儲器尋址和組合控制信號等。譯碼器可以分為通用譯碼器和顯示譯碼器兩大類。在電路中用的譯碼器是共陰極譯碼器74LS48,用74LS48把輸入的8421BCD碼ABCD譯成七段輸出a-g,再由七段數碼管顯示相應的數。

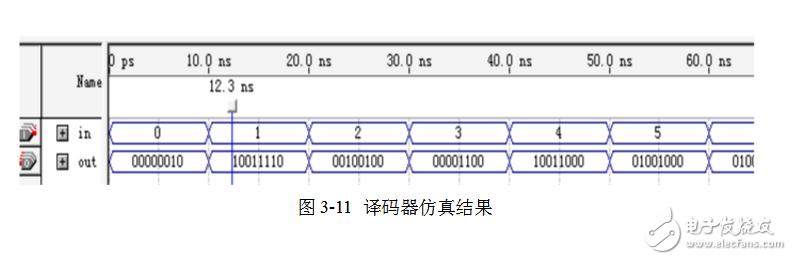

通過QuartusII軟件進行編譯后,仿真結果如圖3-11所示;

分頻器

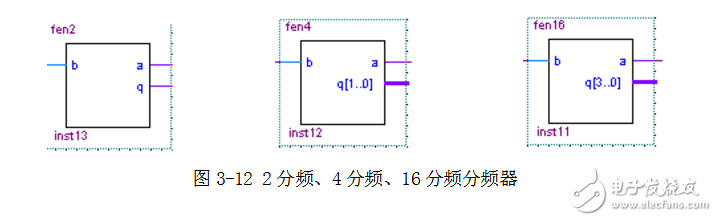

分頻器的作用是將由石英晶體產生的高頻信號分頻成基時鐘脈沖信號和擴展部分所需的頻率。在此電路中,分頻器的功能主要有兩個:一是產生標準脈沖信號;二是功能擴展電路所需的信號,如仿電臺用的1KHz的高頻信號和500Hz的低頻信號等。可以組成二分頻電路和四分頻電路和十六分頻器。

打包后成元器件如圖3-12所示;

鬧時器

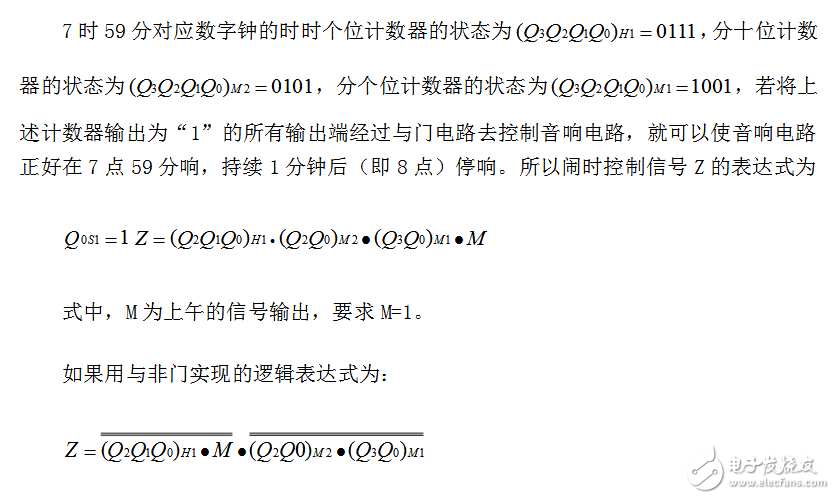

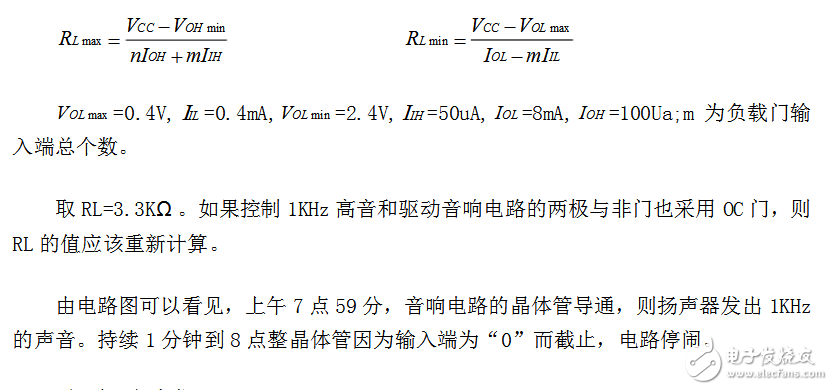

數字鐘在指定的時刻發出信號,或驅動音響電路“鬧時”;或對某裝置的電源進行接通或斷開“控制”。不管是鬧時還是控制,都要求時間準確,即信號的開始時刻與持續時間必須滿足規定的要求。在這里將舉例來說明它的工作原理。要求上午7時59分發出鬧時信號,持續1分鐘。設計如下:

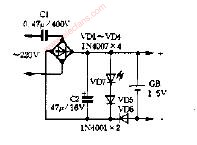

在電路圖中用到了4輸入二與非門74LS20,集電極開路的2輸入四與非門74LS03,因OC門的輸出端可以進行“線與”,使用時在它們的輸出端與電源+5V端之間應接一電阻RL。RL的值由下式決定:

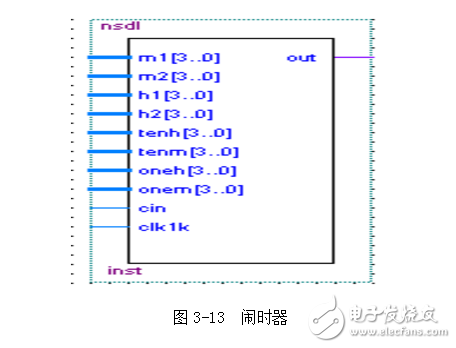

鬧時器程序代碼;

module nsdl(out,m1,m2,h1,h2,tenh,oneh,tenm,onem,clk1k,cin);

output out;

input[3:0] m1,m2,h1,h2,tenh,tenm,oneh,onem; input cin, clk1k;

reg out;

always @(m1 or m2 or h1 or h2 or tenh or tenm or oneh or onem or cin) begin

if(cin) out《=0; else if(cin==0) begin

if(tenh==h1&&oneh==h2&&tenm==m1&&onem==m2) out《=clk1k; else out《=0; end end

endmodule

打包后成元器件如圖3-13所示;

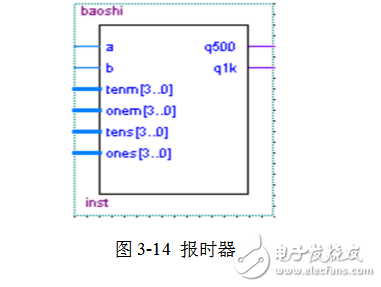

報時器

(一)功能要求

報時的功能要求是:每當數字鐘計時快要到正點時,通常按照4低音1高音的順序發出間斷聲響,以最后一聲高音結束的時刻為正點時刻。

? ? ? (二)該電路的工作原理

電路圖的工作原理舉例來說明;例如設4聲低音(約500Hz)分別 在59分51秒、53秒、55秒及57秒,最后一聲高音(約1000Hz)發生在59秒,它們的持續時間為1秒。只有當分十進位的Q2M2Q0M2=11,分個位的Q3M1Q0M1=11,秒十位的Q2S2Q0S2=11及秒個位的Q0S1=1時,音響電路才能工作。

(三)對該電路中使用的元件的介紹

因為在該電路中所用的元件主要是74LS00、74LS04及74LS20這些元件在前面的

電路中已經介紹。這里就不再介紹它了

報時器程序代碼;

module baoshi(tenm,onem,tens,ones,q500,q1k,a,b); input a,b;

input [3:0]tenm,onem,tens,ones; output q500,q1k; reg q500,q1k;

always @(tenm or onem or tens or ones) begin

if ({tenm,onem}==8‘h59&&{tens,ones}==8’h50||{tenm,onem}==8‘h59&&{tens,ones}==8’h52|| {tenm,onem}==8‘h59&&{tens,ones}==8’h54||{tenm,onem}==8‘h59&&{tens,ones}==8’h56|| {tenm,onem}==8‘h59&&{tens,ones}==8’h58) q500《=a; else q500《=0; end

always @(tenm or onem or tens or ones) begin

if ((tenm[3:0]==0000&&onem[3:0]==0000)&&(tens[3:0]==0000&&ones[3:0]==0000)) q1k《=b; else q1k《=0; end

endmodule

打包后成元器件如圖3-14所示;

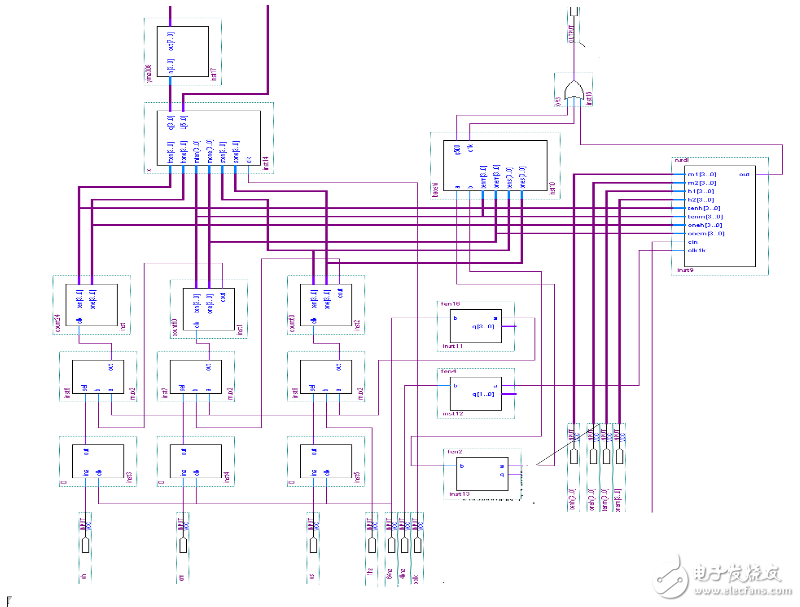

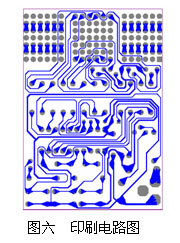

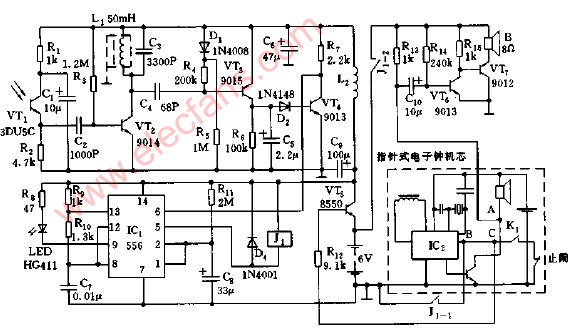

數字鐘原理圖

將各模塊組合一起構成如圖3-15所示:

軟件調試的過程據功能的增加分為幾步:

首先,根據原來的100進制顯示程序的基礎上編寫成時分秒六位顯示的主程序。該程序將時分秒分成個位和十位分別計算,所以將60進制和24進制變成10進制、6進制和2進制。又因為如果時十位為2的話,不能大于3,所以在分十位向時個位進位時得判斷時十位是否為2,在組員的幫助下經過不斷試驗和修改終于完成。過程比較順利。

該電子鐘使用一個鍵來調時,利用長按來選擇所要調的位,用短暫按下來對位進行加1,前提是時鐘暫停,這個功能也是通過長按來實現的。選位是從秒個位到時十位依次選取,但到時十位以后就回不到秒個位了,就是不會循環。所以就得對選的位進行檢查,如果到了時十位再按取位鍵就重新賦給秒個位地址。這樣就可以循環選位了。但在后來的測試中又有了新的問題,如果該位到了9,對一個位進行加1調整就會顯示亂碼。時分秒的十位都會調到9!

對于這個問題費看一些周折。起先構思再加一個減一的鍵,但不但沒有解決這個亂碼問題而且減到了0一下很可能也會出現亂碼。所以就轉而尋求程序解決。調時的時候讓它也像正常運行的時候進位?沒見過這樣的。繼而決定在進行加1調時的時候檢測該位是否到10或6或3。所以就產生了所謂的調時比較子程序,就是在調時的時候將該位跟10或6或3比較。最后,調試的時候卻總是出現這樣的情況:所調的位超過了9或5或2就變成亂碼。比原來進步的地方就是時分秒的十位不用超過9就變成亂碼。這說明雖然還沒成功,但還是有前展的。就繼續調試。

電子發燒友App

電子發燒友App

評論