制造工藝的微米是指IC內(nèi)電路與電路之間的距離。制造工藝的趨勢(shì)是向密集度愈高的方向發(fā)展。密度愈高的IC電路設(shè)計(jì),意味著在同樣大小面積的IC中,可以擁有密度更高、功能更復(fù)雜的電路設(shè)計(jì)。現(xiàn)在主要的180nm、130nm、90nm、65nm、45納米。intel已經(jīng)于2010年發(fā)布32納米的制造工藝的酷睿i3/酷睿i5/酷睿i7系列。并且已有發(fā)布22nm與15nm產(chǎn)品的計(jì)劃。而AMD則表示、自己的產(chǎn)品將會(huì)直接跳過32nm工藝(2010年第三季度生產(chǎn)少許32nm產(chǎn)品、如Orochi、Llano)于2011年中期初發(fā)布28nm的產(chǎn)品(APU)

指令集

⑴CISC指令集

CISC指令集,也稱為復(fù)雜指令集,英文名是CISC,(Complex Instruction Set Computer的縮寫)。在CISC微處理器中,程序的各條指令是按順序串行執(zhí)行的,每條指令中的各個(gè)操作也是按順序串行執(zhí)行的。順序執(zhí)行的優(yōu)點(diǎn)是控制簡(jiǎn)單,但計(jì)算機(jī)各部分的利用率不高,執(zhí)行速度慢。其實(shí)它是英特爾生產(chǎn)的x86系列(也就是IA-32架構(gòu))CPU及其兼容CPU,如AMD、VIA的。即使是現(xiàn)在新起的X86-64(也說成AMD64)都是屬于CISC的范疇。

要知道什么是指令集還要從當(dāng)今的X86架構(gòu)的CPU說起。X86指令集是Intel為其第一塊16位CPU(i8086)專門開發(fā)的,IBM1981年推出的世界第一臺(tái)PC機(jī)中的CPU-i8088(i8086簡(jiǎn)化版)使用的也是X86指令,同時(shí)電腦中為提高浮點(diǎn)數(shù)據(jù)處理能力而增加了X87芯片,以后就將X86指令集和X87指令集統(tǒng)稱為X86指令集。

雖然隨著CPU技術(shù)的不斷發(fā)展,Intel陸續(xù)研制出更新型的i80386.i80486直到過去的PII至強(qiáng)、PIII至強(qiáng)、Pentium 3,Pentium 4系列,最后到今天的酷睿2系列、至強(qiáng)(不包括至強(qiáng)Nocona),但為了保證電腦能繼續(xù)運(yùn)行以往開發(fā)的各類應(yīng)用程序以保護(hù)和繼承豐富的軟件資源,所以Intel公司所生產(chǎn)的所有CPU仍然繼續(xù)使用X86指令集,所以它的CPU仍屬于X86系列。由于Intel X86系列及其兼容CPU(如AMD Athlon MP、)都使用X86指令集,所以就形成了今天龐大的X86系列及兼容CPU陣容。x86CPU目前主要有intel的服務(wù)器CPU和AMD的服務(wù)器CPU兩類。

⑵RISC指令集

RISC是英文“Reduced Instruction Set Computing ”的縮寫,中文意思是“精簡(jiǎn)指令集”。它是在CISC指令系統(tǒng)基礎(chǔ)上發(fā)展起來的,有人對(duì)CISC機(jī)進(jìn)行測(cè)試表明,各種指令的使用頻度相當(dāng)懸殊,最常使用的是一些比較簡(jiǎn)單的指令,它們僅占指令總數(shù)的20%,但在程序中出現(xiàn)的頻度卻占80%。復(fù)雜的指令系統(tǒng)必然增加微處理器的復(fù)雜性,使處理器的研制時(shí)間長(zhǎng),成本高。并且復(fù)雜指令需要復(fù)雜的操作,必然會(huì)降低計(jì)算機(jī)的速度。基于上述原因,20世紀(jì)80年代RISC型CPU誕生了,相對(duì)于CISC型CPU,RISC型CPU不僅精簡(jiǎn)了指令系統(tǒng),還采用了一種叫做“超標(biāo)量和超流水線結(jié)構(gòu)”,大大增加了并行處理能力。RISC指令集是高性能CPU的發(fā)展方向。它與傳統(tǒng)的CISC(復(fù)雜指令集)相對(duì)。相比而言,RISC的指令格式統(tǒng)一,種類比較少,尋址方式也比復(fù)雜指令集少。當(dāng)然處理速度就提高很多了。目前在中高檔服務(wù)器中普遍采用這一指令系統(tǒng)的CPU,特別是高檔服務(wù)器全都采用RISC指令系統(tǒng)的CPU。RISC指令系統(tǒng)更加適合高檔服務(wù)器的操作系統(tǒng)UNIX,現(xiàn)在Linux也屬于類似UNIX的操作系統(tǒng)。RISC型CPU與Intel和AMD的CPU在軟件和硬件上都不兼容。

目前,在中高檔服務(wù)器中采用RISC指令的CPU主要有以下幾類:PowerPC處理器、SPARC處理器、PA-RISC處理器、MIPS處理器、Alpha處理器。

⑶IA-64

EPIC(Explicitly Parallel Instruction Computers,精確并行指令計(jì)算機(jī))是否是RISC和CISC體系的繼承者的爭(zhēng)論已經(jīng)有很多,單以EPIC體系來說,它更像Intel的處理器邁向RISC體系的重要步驟。從理論上說,EPIC體系設(shè)計(jì)的CPU,在相同的主機(jī)配置下,處理Windows的應(yīng)用軟件比基于Unix下的應(yīng)用軟件要好得多。

Intel采用EPIC技術(shù)的服務(wù)器CPU是安騰Itanium(開發(fā)代號(hào)即Merced)。它是64位處理器,也是IA-64系列中的第一款。微軟也已開發(fā)了代號(hào)為Win64的操作系統(tǒng),在軟件上加以支持。在Intel采用了X86指令集之后,它又轉(zhuǎn)而尋求更先進(jìn)的64-bit微處理器,Intel這樣做的原因是,它們想擺脫容量巨大的x86架構(gòu),從而引入精力充沛而又功能強(qiáng)大的指令集,于是采用EPIC指令集的IA-64架構(gòu)便誕生了。IA-64 在很多方面來說,都比x86有了長(zhǎng)足的進(jìn)步。突破了傳統(tǒng)IA32架構(gòu)的許多限制,在數(shù)據(jù)的處理能力,系統(tǒng)的穩(wěn)定性、安全性、可用性、可觀理性等方面獲得了突破性的提高。

IA-64微處理器最大的缺陷是它們?nèi)狈εcx86的兼容,而Intel為了IA-64處理器能夠更好地運(yùn)行兩個(gè)朝代的軟件,它在IA-64處理器上(Itanium、Itanium2 ……)引入了x86-to-IA-64的解碼器,這樣就能夠把x86指令翻譯為IA-64指令。這個(gè)解碼器并不是最有效率的解碼器,也不是運(yùn)行x86代碼的最好途徑(最好的途徑是直接在x86處理器上運(yùn)行x86代碼),因此Itanium 和Itanium2在運(yùn)行x86應(yīng)用程序時(shí)候的性能非常糟糕。這也成為X86-64產(chǎn)生的根本原因。

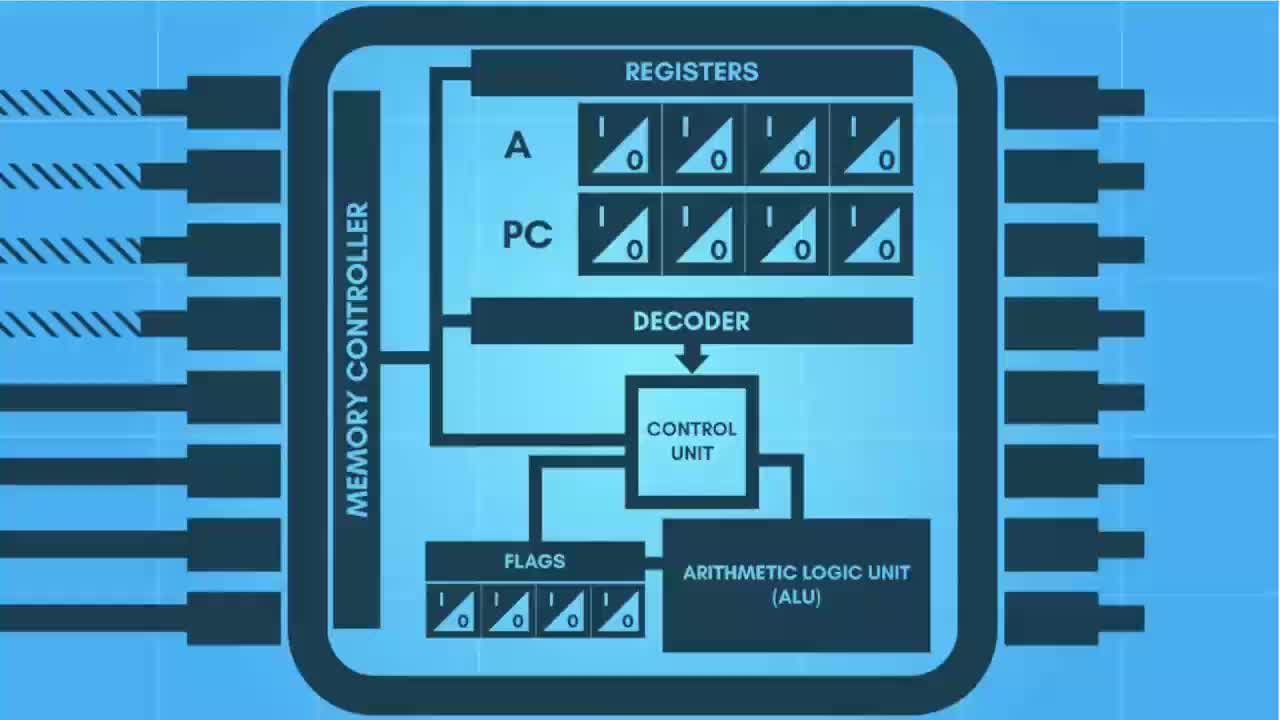

超流水線與超標(biāo)量

在解釋超流水線與超標(biāo)量前,先了解流水線(Pipeline)。流水線是Intel首次在486芯片中開始使用的。流水線的工作方式就象工業(yè)生產(chǎn)上的裝配流水線。在CPU中由5-6個(gè)不同功能的電路單元組成一條指令處理流水線,然后將一條X86指令分成5-6步后再由這些電路單元分別執(zhí)行,這樣就能實(shí)現(xiàn)在一個(gè)CPU時(shí)鐘周期完成一條指令,因此提高CPU的運(yùn)算速度。經(jīng)典奔騰每條整數(shù)流水線都分為四級(jí)流水,即指令預(yù)取、譯碼、執(zhí)行、寫回結(jié)果,浮點(diǎn)流水又分為八級(jí)流水。超標(biāo)量是通過內(nèi)置多條流水線來同時(shí)執(zhí)行多個(gè)處理器,其實(shí)質(zhì)是以空間換取時(shí)間。而超流水線是通過細(xì)化流水、提高主頻,使得在一個(gè)機(jī)器周期內(nèi)完成一個(gè)甚至多個(gè)操作,其實(shí)質(zhì)是以時(shí)間換取空間。例如Pentium 4的流水線就長(zhǎng)達(dá)20級(jí)。將流水線設(shè)計(jì)的步(級(jí))越長(zhǎng),其完成一條指令的速度越快,因此才能適應(yīng)工作主頻更高的CPU。但是流水線過長(zhǎng)也帶來了一定副作用,很可能會(huì)出現(xiàn)主頻較高的CPU實(shí)際運(yùn)算速度較低的現(xiàn)象,Intel的奔騰4就出現(xiàn)了這種情況,雖然它的主頻可以高達(dá)1.4G以上,但其運(yùn)算性能卻遠(yuǎn)遠(yuǎn)比不上AMD 1.2G的速龍甚至奔騰III。

封裝形式

CPU封裝是采用特定的材料將CPU芯片或CPU模塊固化在其中以防損壞的保護(hù)措施,一般必須在封裝后CPU才能交付用戶使用。CPU的封裝方式取決于CPU安裝形式和器件集成設(shè)計(jì),從大的分類來看通常采用Socket插座進(jìn)行安裝的CPU使用PGA(柵格陣列)方式封裝,而采用Slot x槽安裝的CPU則全部采用SEC(單邊接插盒)的形式封裝。現(xiàn)在還有PLGA(Plastic Land Grid Array)、OLGA(Organic Land Grid Array)等封裝技術(shù)。由于市場(chǎng)競(jìng)爭(zhēng)日益激烈,目前CPU封裝技術(shù)的發(fā)展方向以節(jié)約成本為主。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論