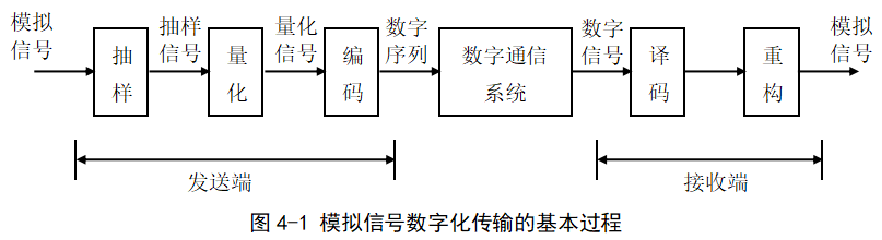

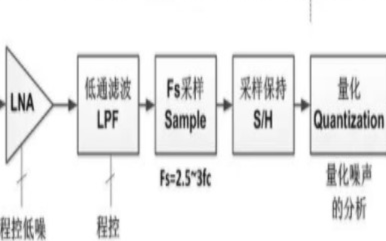

采樣及采樣保持

采樣貌似有一套完整的理論,就是《數字信號處理》書中的一堆公式推導,我們這里當然不會那么去說。其實采樣最核心的問題就是采樣率選擇的問題。

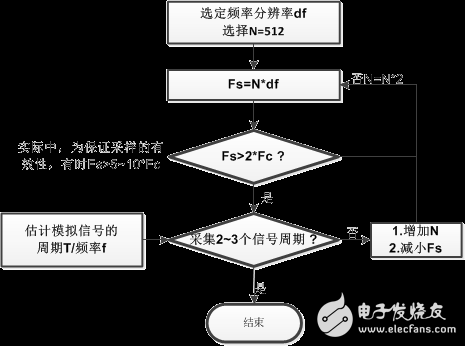

根據實際,選擇頻率分辨率df

選擇做DFT得點數N,因為DFT時域點數和變換后頻域點數相同,則采樣率可確定,Fs=N*df

Fs是否滿足Nyquist的采樣定理?是,OK,否則增加點數N,重新計算2。

我們希望df越小越好,但實際上,df越小,N越大,計算量和存儲量隨之增大。一般取N為為2的整數次冪,不足則在尾端補0。

這里給出我的一個選擇Fs的方案流程圖,僅供參考。

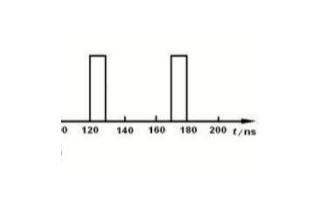

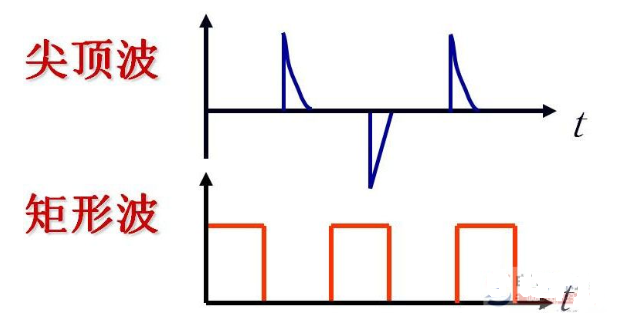

采樣后還有一個重要的操作是采樣保持(S/H)操作,采樣脈沖采樣后無法立刻量化,這個過程要等待很短的一個時間,硬件上一般0.幾個us,等待量化器的量化。

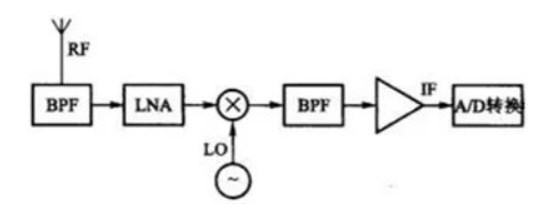

注意,在量化之前,所有的信號都是模擬信號,模擬信號就有很多干擾的問題需要考慮,這里只是從總體上給出我對整個過程的理解。更多細化的方案還需要根據實際信號進行研究。

量化

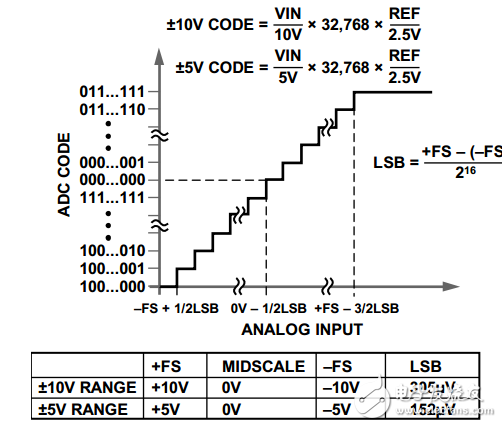

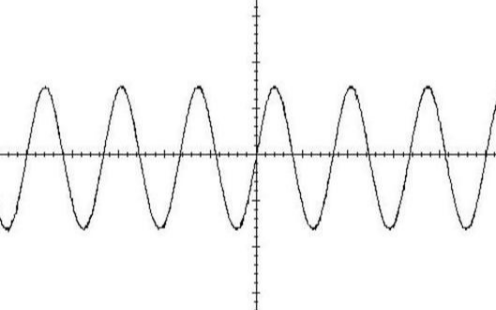

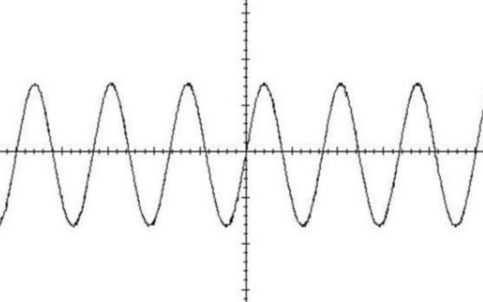

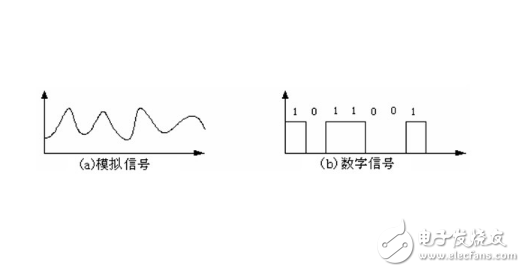

我們可以先直觀的看一下量化的過程,

》

量化有個關鍵的參數,叫量化位數,在所有的AD轉換芯片(如AD7606)上都能看到這個關鍵的參數,常見的有8bit,10bit,12bits,16bit和24bit。

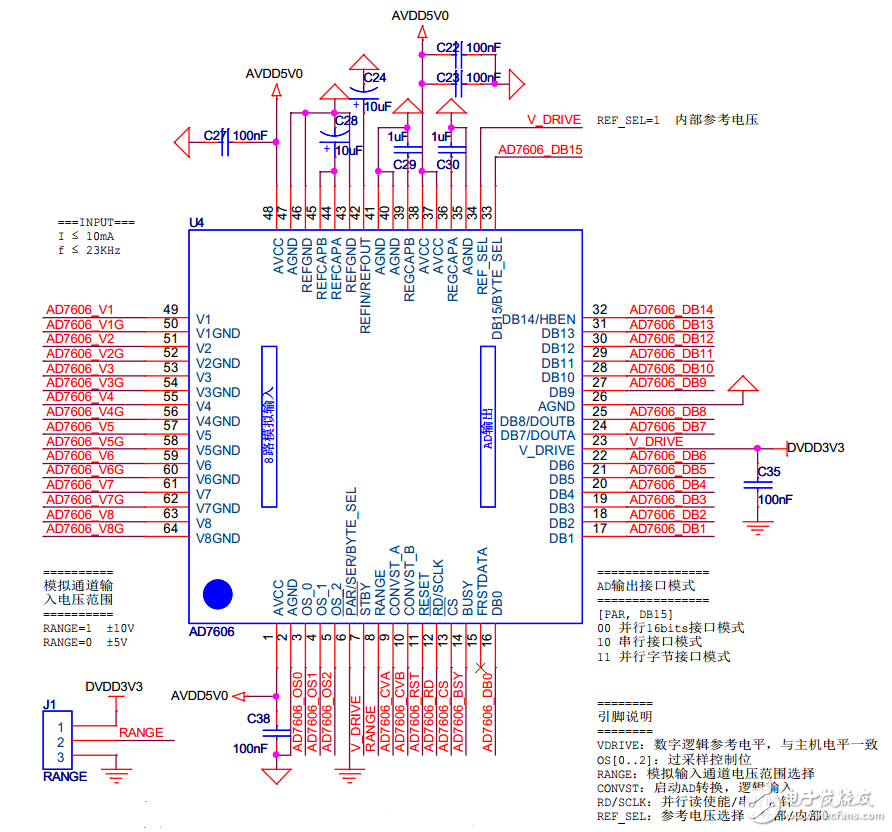

如上圖,以AD7606為例,AD7606是16bit的AD芯片,量化位數指用16bit來表示連續信號的幅值。因此,考慮AD的測量范圍(AD7606有兩種:±5V和±10V),則AD分辨率是

±5V: (5V-(-5V)) / (2^16) = 152 uV

±10V: (10V-(-10V)) / (2^16) = 305 uV

量化位數越高,AD分辨率越高,習慣上,AD分辨率用常用LSB標示。

因此,AD7606中對于某個輸入模擬電壓值,因為存在正負電壓,若以0V為中間電壓值,范圍為±5V時AD轉換電壓可計算為

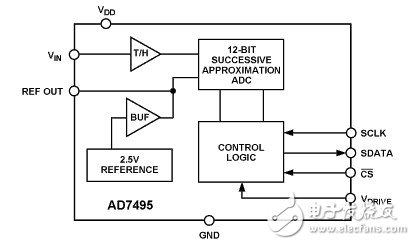

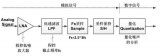

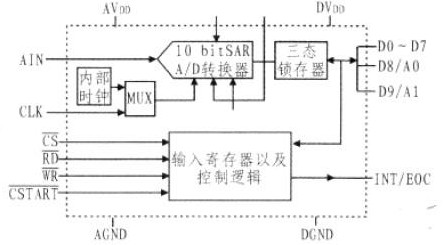

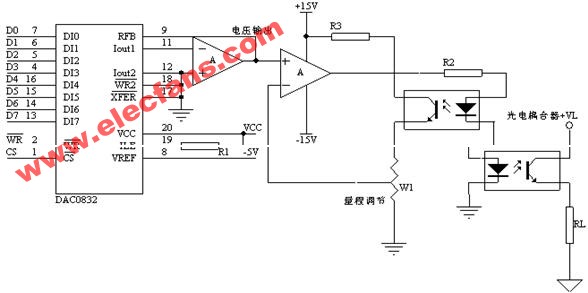

AD7606若使用內部參考電壓,Vref=2.5V。哦對了,這又出現個參考電壓。參考電壓與AD量化的實現方式有關,從速度上分串行和并行,串行包括逐次逼近型,并行方式包括并行比較式,如下圖(左:串行,右:并行)。AD7606是使用逐次逼近型的方式。

AD轉換芯片另外兩個重要參數是轉換時間(轉換速率)。并行AD的轉換速率比串行的要高。但并行比較的方式中電阻的精度對量化有影響。

接著,我們還將介紹一個重要的概念:量化噪聲。量化噪聲對應量化信噪比,

SNRq = (6.02N + 4.77) dB

其中N為量化位數,且不去管這個公式是怎么得到的(詳細推導可參考文獻[2]),對于

N=12, SNRq ≈ 70dB

N=16, SNRq ≈ 94dB

從中可以看出:每增加1bit量化位數,SNRq將提高6.02dB,在設計過程中,如果對方有信噪比的要求,則在ADC選型時就要選擇合適位數的ADC芯片。

明顯的,并不是量化位數越高越好,量化位數的提高將對成本、轉換速度、存儲空間與數據吞吐量等眾多方面提出更高的要求。同時,我們盡量提高量化噪聲的前提是信號的SNR已經比較低了,如果信號的SNR比量化噪聲還高,努力提高量化噪聲將是舍本求末的做法。

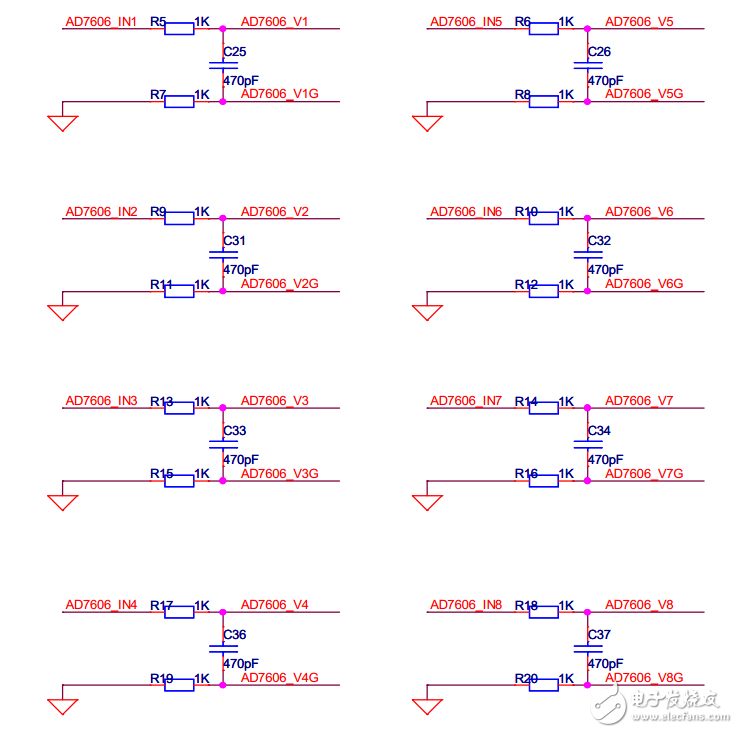

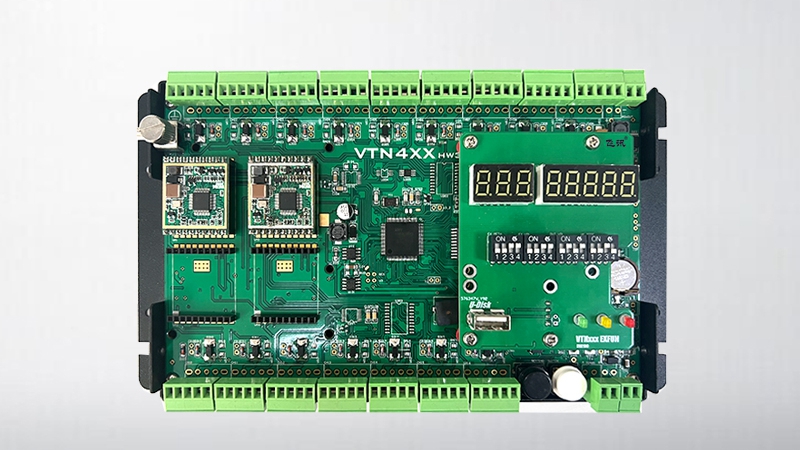

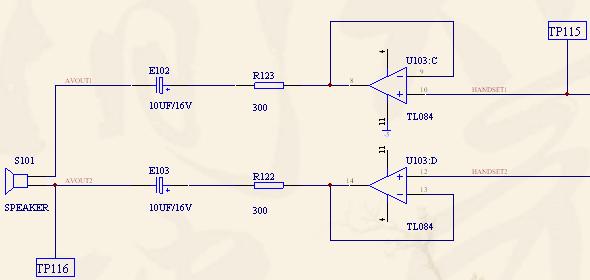

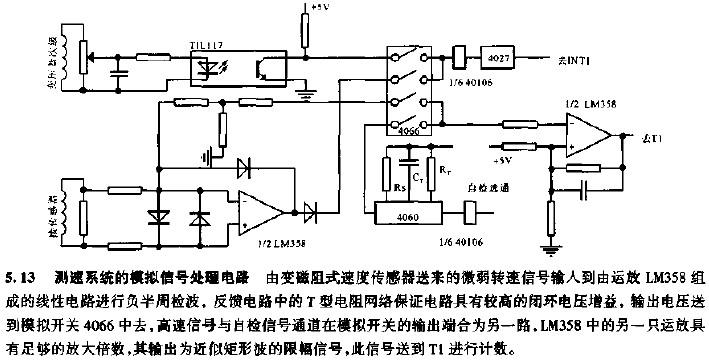

到最后,給點福利吧,下面是我參考AD7606數據手冊設計的原理圖,經過實踐檢驗可用:

電子發燒友App

電子發燒友App

評論