74HC573芯片概述

74HC573是擁有八路輸出的透明鎖存器,輸出為三態(tài)門,是一種高性能硅柵CMOS器件。74HC573包含八路D 型透明鎖存器,每個(gè)鎖存器具有獨(dú)立的D 型輸入,以及適用于面向總線的應(yīng)用的三態(tài)輸出。所有鎖存器共用一個(gè)鎖存使能(LE)端和一個(gè)輸出使能(OE)端。由此得出74hc573芯片屬于8位數(shù)碼管驅(qū)動(dòng)芯片。

當(dāng)LE為高時(shí),數(shù)據(jù)從Dn輸入到鎖存器,在此條件下,鎖存器進(jìn)入透明模式,也就是說,鎖存器的輸出狀態(tài)將會(huì)隨著對(duì)應(yīng)的D輸入每次的變化而改變。當(dāng)LE為低時(shí),鎖存器將存儲(chǔ)D輸入上的信息一段就緒時(shí)間,直到LE的下降沿來臨。當(dāng)OE為低時(shí),8個(gè)鎖存器的內(nèi)容可被正常輸出;當(dāng)OE為高時(shí),輸出進(jìn)入高阻態(tài)。OE端的操作不會(huì)影響鎖存器的狀態(tài)。

74HC573和74LS373原理一樣,8數(shù)據(jù)鎖存器。主要用于數(shù)碼管、按鍵等等的控制

HC573原理說明

M54HC563/74HC563/M54HC573/74HC573的八個(gè)鎖存器都是透明的D 型鎖存器,當(dāng)使能(G)為高時(shí),Q 輸出將隨數(shù)據(jù)(D)輸入而變。當(dāng)使能為低時(shí),輸出將鎖存在已建立的數(shù)據(jù)電平上。輸出控制不影響鎖存器的內(nèi)部工作,即老數(shù)據(jù)可以保持,甚至當(dāng)輸出被關(guān)閉時(shí),

新的數(shù)據(jù)也可以置入。這種電路可以驅(qū)動(dòng)大電容或低阻抗負(fù)載,可以直接與系統(tǒng)總線接口并驅(qū)動(dòng)總線,而不需要外接口。特別適用于緩沖寄存器,I/O 通道,雙向總線驅(qū)動(dòng)器和工作寄存器。

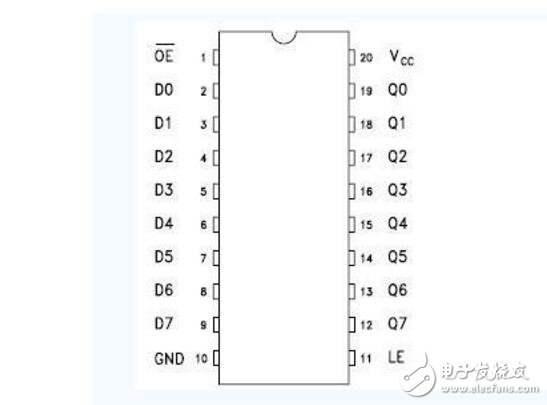

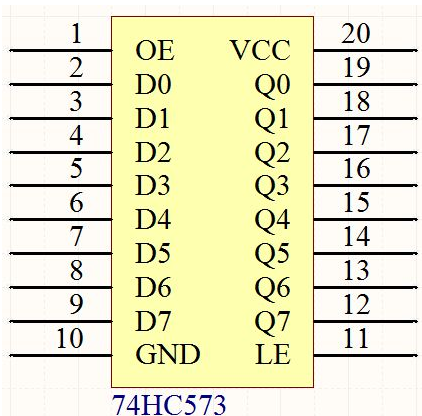

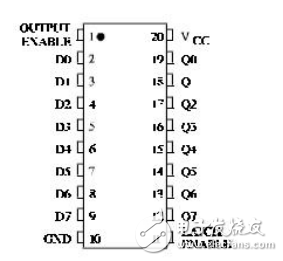

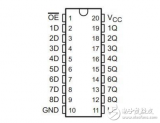

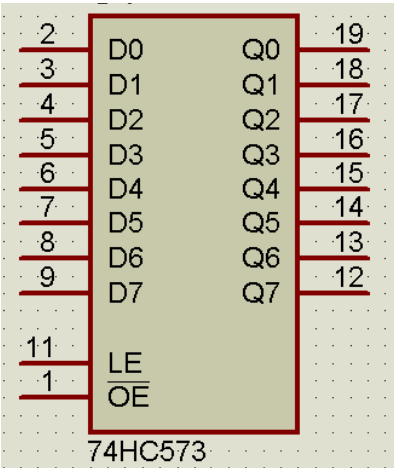

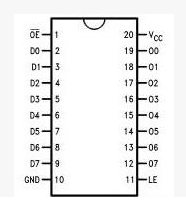

HC573引腳圖

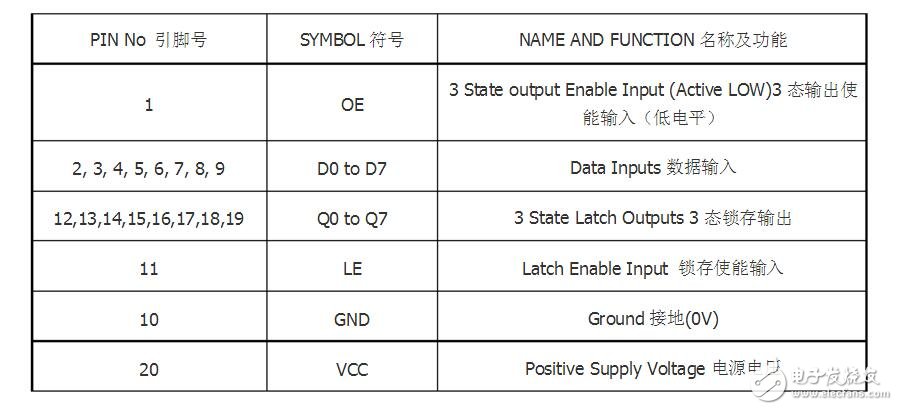

HC573引腳功能表

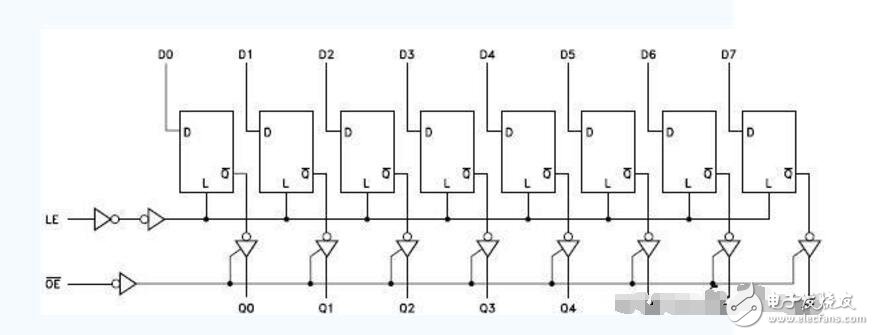

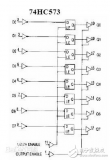

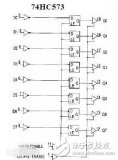

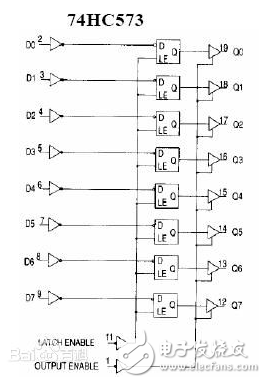

74hc573邏輯圖

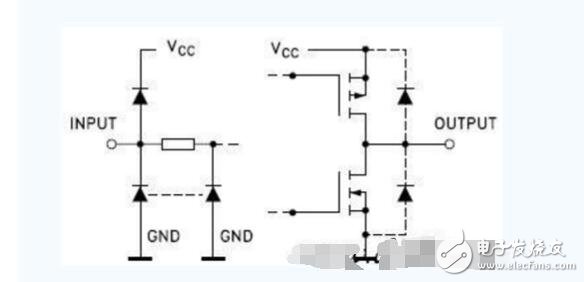

輸入輸出等效電路

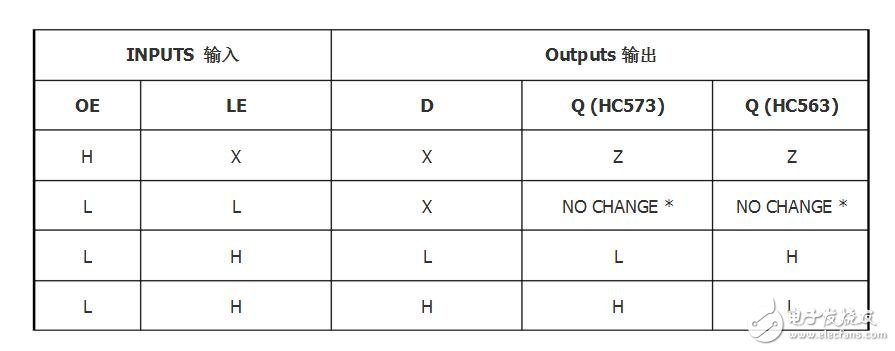

1. 真值表

參見74LS373的PDF的第2頁: Dn LE OE On H H L H L H L L X L L Qo X X H Z 這個(gè)就是真值表,表示這個(gè)芯片在輸入和其它的情況下的輸出情況。 每個(gè)芯片的數(shù)據(jù)手冊(cè)(datasheet)中都有真值表。 布爾邏輯比較簡(jiǎn)單,在此不贅述;

2. 高阻態(tài) 就是輸出既不是高電平,也不是低電平,而是高阻抗的狀態(tài);在這種狀態(tài)下,可以多個(gè)芯片并聯(lián)輸出;但是,這些芯片中只能有一個(gè)處于非高阻態(tài)狀態(tài),否則會(huì)將芯片燒毀; 高阻態(tài)的概念在RS232和RS422通訊中還可以用到。

3. 數(shù)據(jù)鎖存 當(dāng)輸入的數(shù)據(jù)消失時(shí),在芯片的輸出端,數(shù)據(jù)仍然保持; 這個(gè)概念在并行數(shù)據(jù)擴(kuò)展中經(jīng)常使用到。

4. 數(shù)據(jù)緩沖

加強(qiáng)驅(qū)動(dòng)能力。74LS244/74LS245/74LS373/74LS573都具備數(shù)據(jù)緩沖的能力。

OE:output_enable,輸出使能;

LE:latch_enable,數(shù)據(jù)鎖存使能,latch是鎖存的意思;

Dn:第n路輸入數(shù)據(jù);

On:第n路輸出數(shù)據(jù);

再看這個(gè)真值表,意思如下:

第四行:當(dāng)OE=1是,無論Dn、LE為何,輸出端為高阻態(tài);

第三行:當(dāng)OE=0、LE=0時(shí),輸出端保持不變;

第二行第一行:當(dāng)OE=0、LE=1時(shí),輸出端數(shù)據(jù)等于輸入端數(shù)據(jù);

結(jié)合下面的波形圖,在實(shí)際應(yīng)用的時(shí)候是這樣做的:

a. OE=0;

b. 先將數(shù)據(jù)從單片機(jī)的口線上輸出到Dn;

c. 再將LE從0-》1-》0 d. 這時(shí),你所需要輸出的數(shù)據(jù)就鎖存在On上了,輸入的數(shù)據(jù)在變化也影響不到輸出的數(shù)據(jù)了;實(shí)際上,單片機(jī)現(xiàn)在在忙著干別的事情,串行通信、掃描鍵盤……單片機(jī)的資源有限啊。

在單片機(jī)按照RAM方式進(jìn)行并行數(shù)據(jù)的擴(kuò)展時(shí),使用movx @dptr, A這條指令時(shí),這些時(shí)序是由單片機(jī)來實(shí)現(xiàn)的。 后面的表格中還有需要時(shí)間的參數(shù),你不需要去管它,因?yàn)檫@些參數(shù)都是幾十ns級(jí)別的,對(duì)于單片機(jī)在12M下的每個(gè)指令周期最小是1us的情況下,完全可以實(shí)現(xiàn);如果是你自己來實(shí)現(xiàn)這個(gè)邏輯,類似的指令如下:

mov P0,A ;將數(shù)據(jù)輸出到并行數(shù)據(jù)端口

clr LE

setb LE

clr LE ;上面三條指令完成LE的波形從0-》1-》0的變化

74ls573跟74LS373邏輯上完全一樣,只不過是管腳定義不一樣,數(shù)據(jù)輸入和輸出端

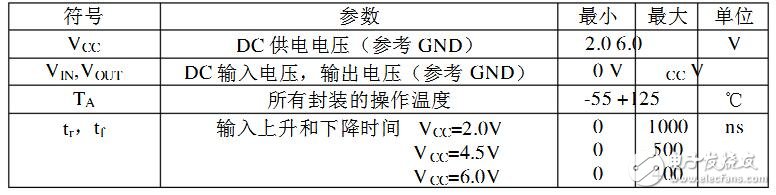

74HC573最大值范圍

最大值范圍是指超過這個(gè)值,將損害器件。 操作最好在下面的推薦操作條件下。

+額定功率的下降——PDIP:-10mW/℃ ,65℃~125℃

SOIC:-7 mW/℃ ,65℃~125℃

推薦操作條件

這個(gè)器件帶有保護(hù)電路,以免被高的靜態(tài)電壓或電場(chǎng)損壞。然而,對(duì)于高阻抗電路,必須要采取預(yù)防以免工作在任何高于最大值范圍的條件下工作。VIN和VOUT應(yīng)該被約束在GND≤(VIN或VOUT)≤VCC。

不用的輸入管腿必須連接總是連接到一個(gè)適合的邏輯電壓電平(也就是GND或者VCC)。不用的輸出管腿必須懸空。

74hc573鎖存器作用

在LED和數(shù)碼管顯示方面,要維持一個(gè)數(shù)據(jù)的顯示,往往要持續(xù)的快速的刷新。尤其是在四段八位數(shù)碼管等這些要選通的顯示設(shè)備上。在人類能夠接受的刷新頻率之內(nèi),大概每三十毫秒就要刷新一次。這就大大占用了處理器的處理時(shí)間,消耗了處理器的處理能力,還浪費(fèi)了處理器的功耗。

鎖存器的使用可以大大的緩解處理器在這方面的壓力。當(dāng)處理器把數(shù)據(jù)傳輸?shù)芥i存器并將其鎖存后,鎖存器的輸出引腳便會(huì)一直保持?jǐn)?shù)據(jù)狀態(tài)直到下一次鎖存新的數(shù)據(jù)為止。這樣在數(shù)碼管的顯示內(nèi)容不變之前,處理器的處理時(shí)間和IO引腳便可以釋放。可以看出,處理器處理的時(shí)間僅限于顯示內(nèi)容發(fā)生變化的時(shí)候,這在整個(gè)顯示時(shí)間上只是非常少的一個(gè)部分。而處理器在處理完后可以有更多的時(shí)間來執(zhí)行其他的任務(wù)。這就是鎖存器在LED和數(shù)碼管顯示方面的作用:節(jié)省了寶貴的MCU時(shí)間。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論