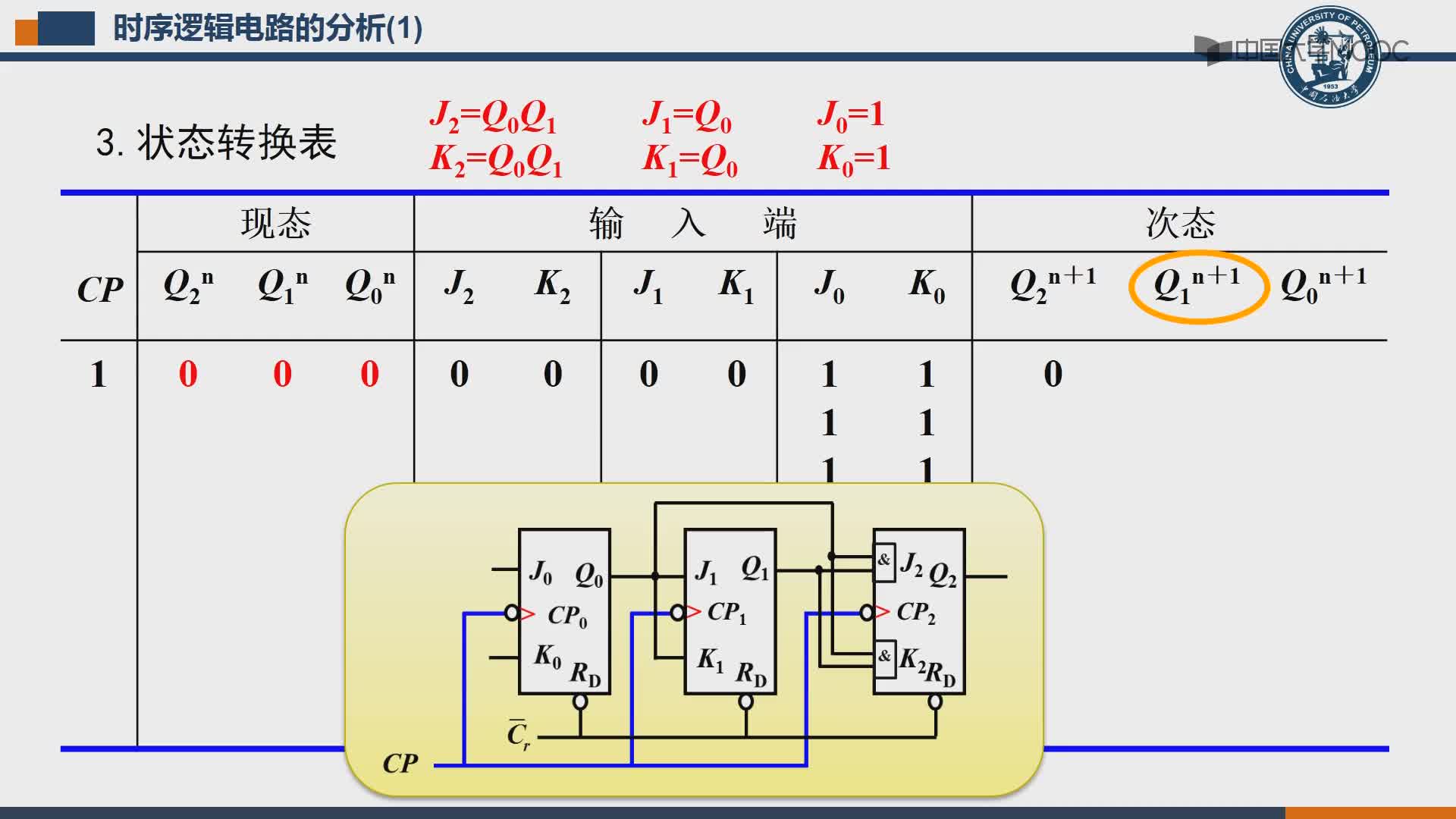

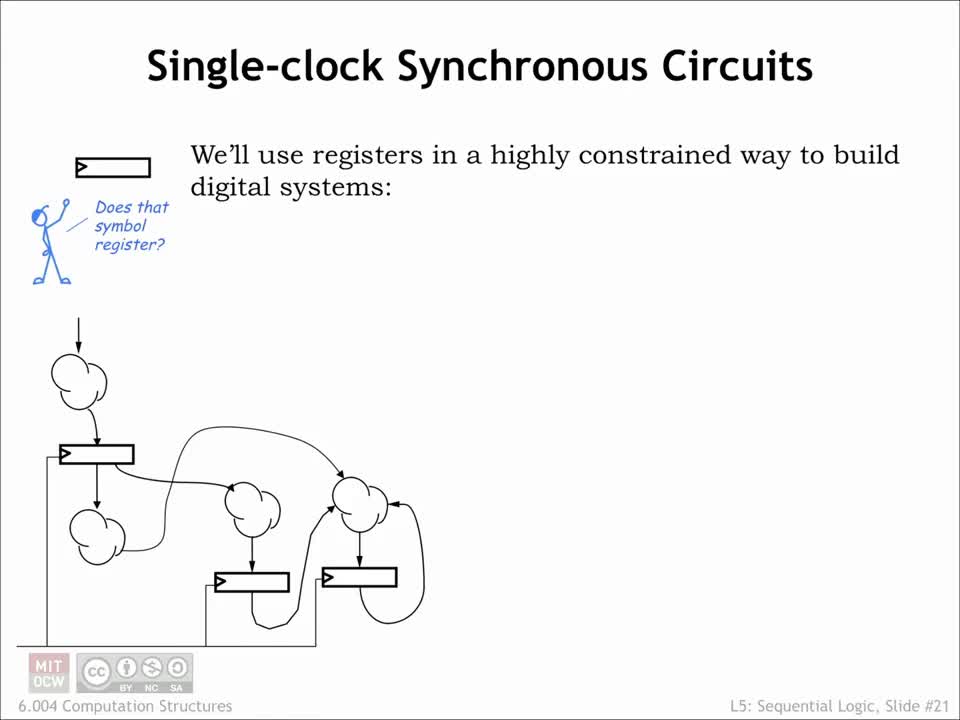

什么是時序電路

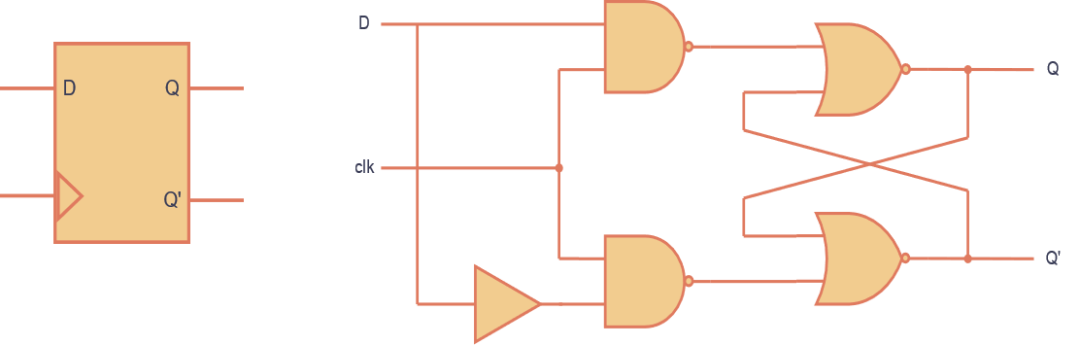

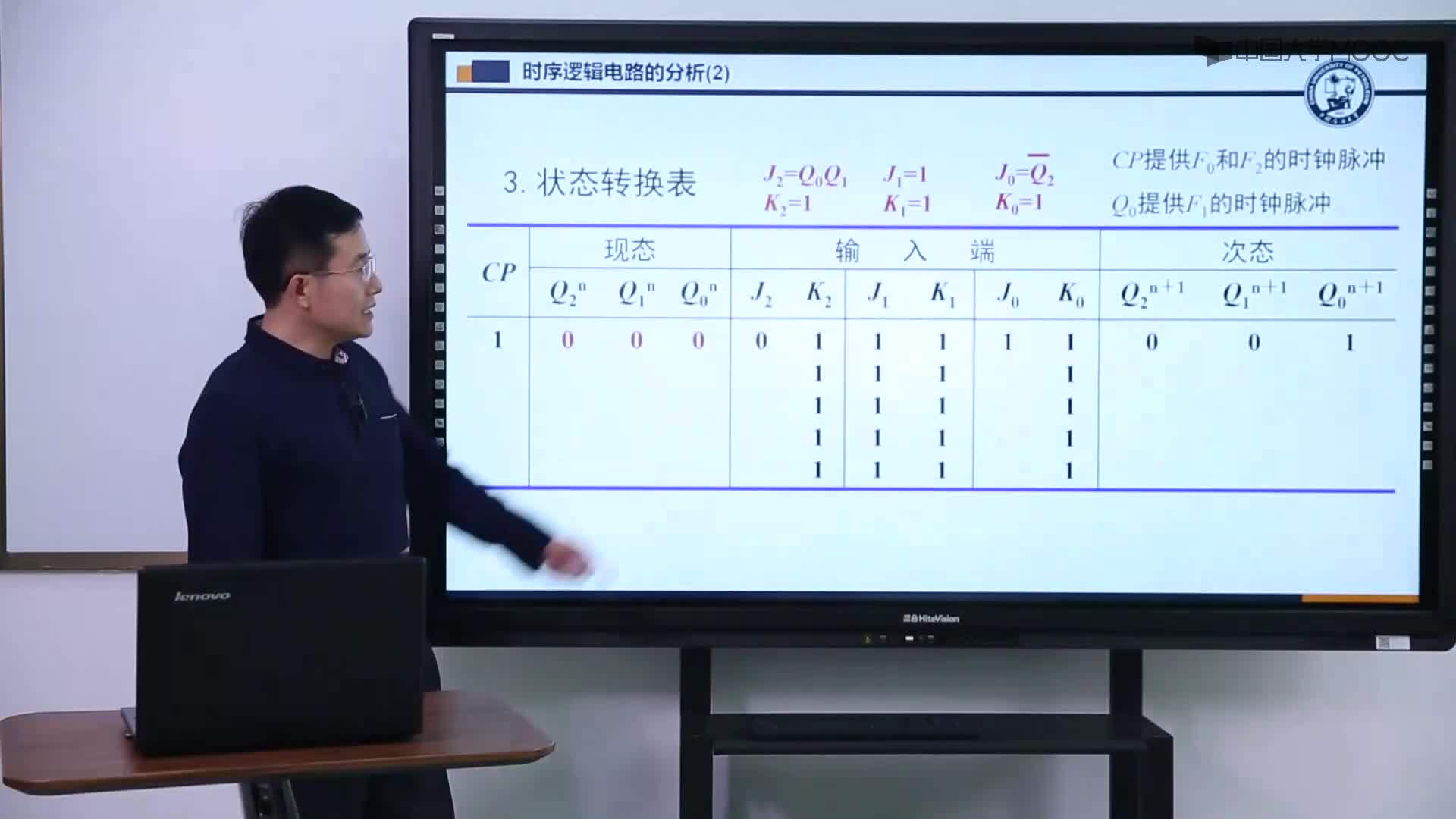

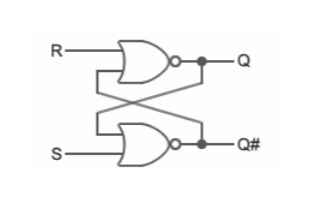

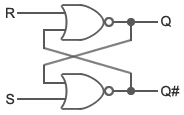

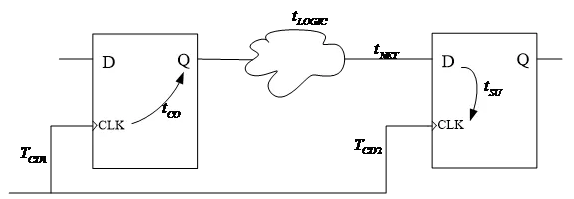

任意時刻的穩(wěn)定輸出,不僅與該時刻的輸入有關(guān),而且還和電路原來的狀態(tài)有關(guān)的數(shù)字電路,稱作時序邏輯電路,簡稱時序電路。時序電路一般由觸發(fā)器構(gòu)成的存貯電路和組合電路組成。若電路中所有的觸發(fā)器都由同一時鐘脈沖控制,則稱這種時序電路為同步時序電路,否則稱為異步時s序電路。常用的時序電路部件有寄存器、計數(shù)器等。

寄存器

在數(shù)字系統(tǒng)和電子計算機中,常需要把一些數(shù)碼和運算結(jié)果存貯起來,這種存貯數(shù)碼的邏輯部件稱為寄存器。

寄存器按功能可分為數(shù)碼寄存器和移位寄存器。 前者只能存貯數(shù)碼, 以便在需要時取出;后者不但能夠存貯數(shù)碼,而且能把數(shù)碼按順序依次左移、右移、或雙向移動。

依數(shù)據(jù)的存貯方式,寄存器又有并行輸入和串行輸入之分。前者是指多位數(shù)據(jù)在寫入命令的作用下同時存入寄存器,后者是指多位數(shù)據(jù)在時鐘脈沖的作用下依次移位,逐個存入寄存器。與此類似,寄存器的輸出方式也有并行輸出和串行輸出兩種,前者是指寄存器內(nèi)的數(shù)據(jù)同時向外輸出,后者是指寄存器內(nèi)的數(shù)據(jù)依次逐個輸出。也有采用串并行輸入和串并行輸出的寄存器。不過一般數(shù)碼寄存器采用的是并行輸入、并行輸出的方式,而移位寄存器采用的是既可串行輸入,并行(或串并行)輸出方式,也可串并行輸入、串并行輸出的方式。

電子發(fā)燒友App

電子發(fā)燒友App

評論