使用 LTSpice 模擬和評(píng)估傳導(dǎo)發(fā)射。

在我的大多數(shù) DC/DC 轉(zhuǎn)換器設(shè)計(jì)中,我主要使用模擬設(shè)備的 DC/DC 轉(zhuǎn)換器。主要原因之一是,正如我們將在此處學(xué)習(xí)的那樣,我們將節(jié)省大量設(shè)計(jì)時(shí)間,因?yàn)?AD 允許我們使用出色的工具LTSpice模擬他們的 DC/DC 轉(zhuǎn)換器。

凌力爾特公司最初于 1999 年設(shè)計(jì)了 LTSpice,20 多年來(lái)它一直是我的模擬仿真工具。這是令人信服的,我不記得我是否有一個(gè)沒(méi)有反映我在現(xiàn)場(chǎng)看到的模擬。

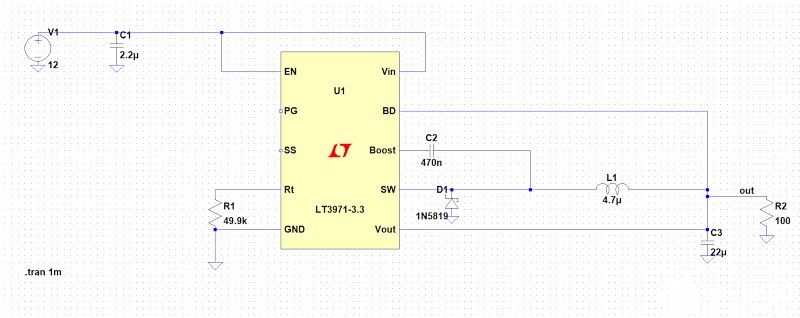

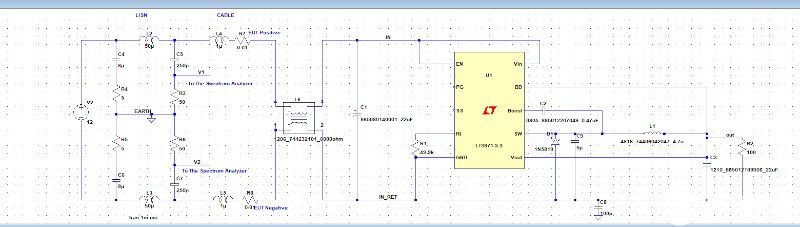

假設(shè)我們要設(shè)計(jì)一個(gè) 10 V 至 3.3 V 降壓轉(zhuǎn)換器,1A。我們可以從 AD 網(wǎng)站上選擇眾多 DC/DC 轉(zhuǎn)換器之一。我選擇了 LT3971-3.3,因?yàn)樗恍枰獛讉€(gè)額外的組件。因此,讓我們打開(kāi) LT3971-3.3 數(shù)據(jù)表,復(fù)制參考原理圖,并使用 LTspice 運(yùn)行我們的第一個(gè)仿真。

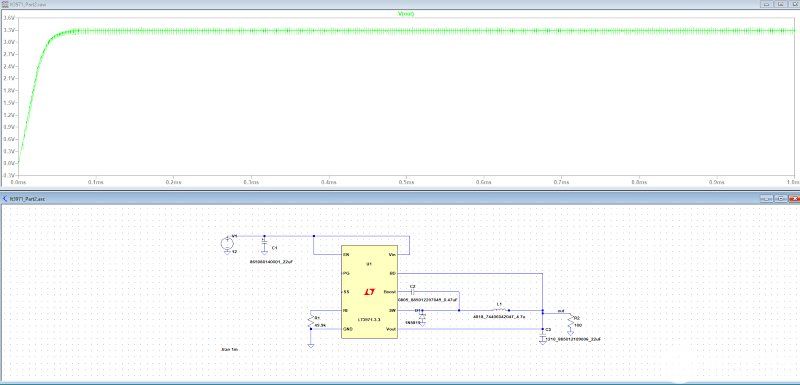

圖 1.數(shù)據(jù)表中所示的 LT3971-3.3 原理圖。(使用理想的無(wú)源元件)。圖片由Francesco Poderico提供

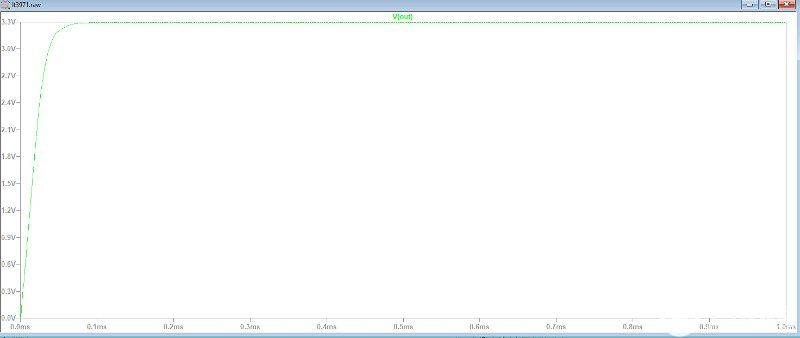

圖 2. 運(yùn)行第一個(gè)模擬。圖片由Francesco Poderico提供

首先要注意的是,DCDC 轉(zhuǎn)換器需要不到 0.1 毫秒的時(shí)間來(lái)穩(wěn)定輸出。讓我們注意這一點(diǎn)(稍后我們將需要它)。

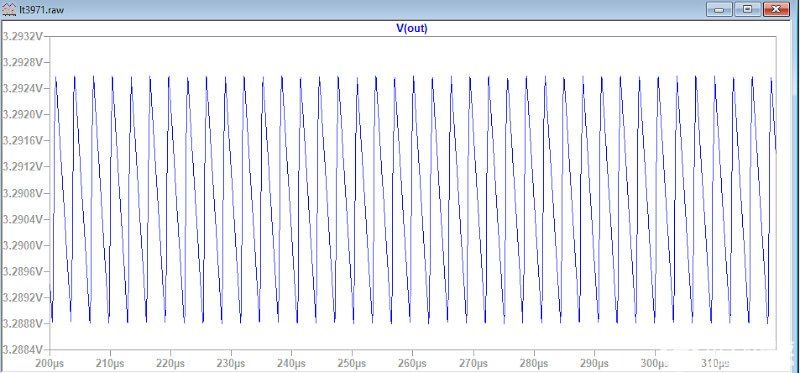

現(xiàn)在讓我們放大 Vout,看看在大學(xué)學(xué)習(xí)的典型鋸齒波形。

圖 3. 通過(guò)放大 Vout,我們可以看到理想降壓轉(zhuǎn)換器的典型鋸波波形。圖片由Francesco Poderico提供

都好!或不?

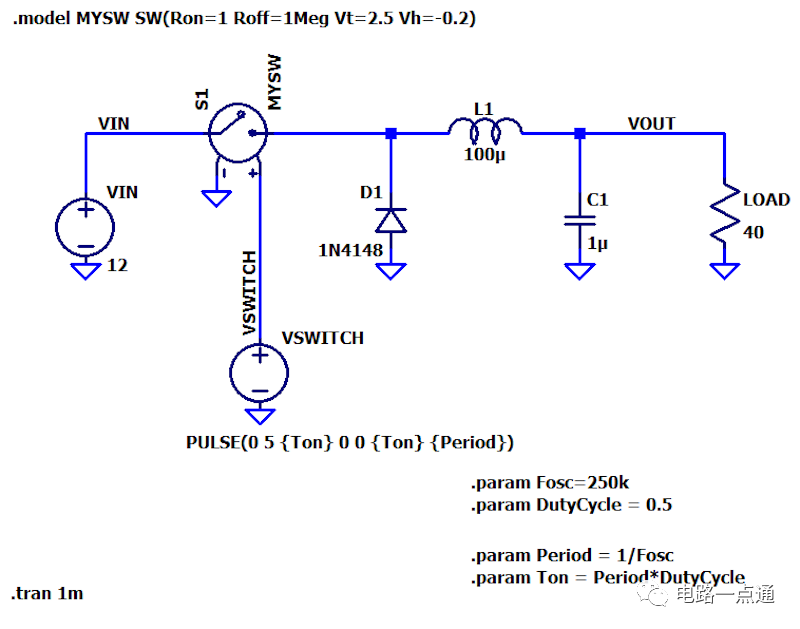

問(wèn)題是我們沒(méi)有為無(wú)源元件 L1、C1、C2 和 C3 使用正確的模型。

讓我們使用 L1、C1、C2 和 C3 的一些模型重復(fù)相同的模擬。讓我們使用 L1、C1、C2 和 C3 的正確模型重復(fù)模擬,看看它有什么不同。

對(duì)于本文,我們將使用 Wurth 組件。Wurth 的好處是他們?yōu)?LTSpice、Altium 等創(chuàng)建了一個(gè)巨大的庫(kù)。所以讓我們繼續(xù) Wurth 并下載一些 LTspice 庫(kù),我們需要這個(gè)庫(kù)來(lái)進(jìn)行模擬。

我已經(jīng)下載了庫(kù):

LTSpice_WE-LQFS、LTSpice_WE-CNSW、LTSpice_WCAP_ASLU、LTSpice_WCAP_CSGP

它們可從 Wurth 網(wǎng)站免費(fèi)獲得。請(qǐng)下載并復(fù)制到 C:Users yourname DocumentsLTSpiceXVIIlib。

完成此操作后,我們可以將這個(gè)庫(kù)用于我們的項(xiàng)目。讓我們運(yùn)行相同的模擬,但對(duì)所有無(wú)源使用正確的模型。

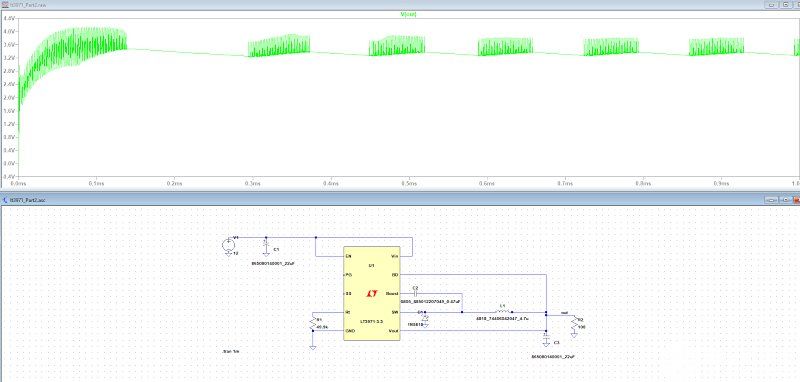

圖 4. 上面的仿真是一個(gè)完美的例子,它說(shuō)明了為什么我們應(yīng)該為 DCDC 轉(zhuǎn)換器使用具有低 ESR 的電容器。圖片由Francesco Poderico提供

我們有第一個(gè)驚喜:上圖顯示輸出電壓非常不穩(wěn)定。原因是我在 C1 和 C3 上都使用了壞電容。然而,關(guān)于輸出電壓,C3 是最重要的。因此,第一課:C3 應(yīng)該具有低 ESR 和低 ESL。讓我們用一個(gè)優(yōu)秀的陶瓷電容器來(lái)改變 C3 并重復(fù)模擬。

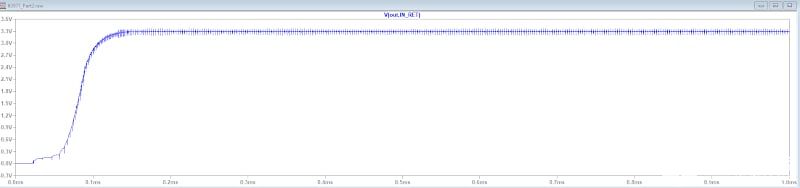

圖 5。C3 現(xiàn)在是一個(gè)陶瓷電容器。現(xiàn)在輸出穩(wěn)定,但如果我們將此電壓輸出與圖 2 中的電壓輸出進(jìn)行比較,我們會(huì)注意到 Vout 現(xiàn)在噪聲更大。圖片由Francesco Poderico提供

它已經(jīng)看起來(lái)好多了。然而,并不像我們之前看到的那么完美。

添加我們?cè)诘?3 部分中設(shè)計(jì)的 LISN 和電源線,并將它們放在一起。

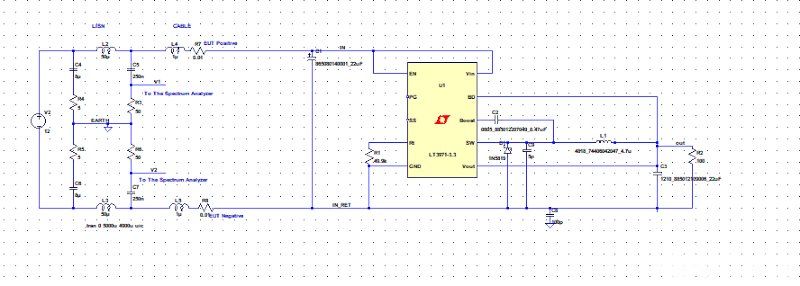

電路變成了這樣:

圖 6. 在電路回路和大地之間添加一個(gè) LISN 和一個(gè) 100 pF 寄生電容(參見(jiàn)第 1 部分、第 2 部分、第 3 部分)。圖片由Francesco Poderico提供

輸出電壓變?yōu)椋?/p>

圖 7. Vout 現(xiàn)在開(kāi)始看起來(lái)更嘈雜了。圖片由Francesco Poderico提供

在圖 6 中,您應(yīng)該注意到 SW 引腳和 U1 參考之間有一個(gè) 5pF 電容。我添加了這些電容器來(lái)模擬低側(cè) MOS(U1 內(nèi)部)的內(nèi)部 Cd,而 C8 是我們?cè)诘?3 部分中研究的寄生電容器(100 pF)。

共模和差模噪聲

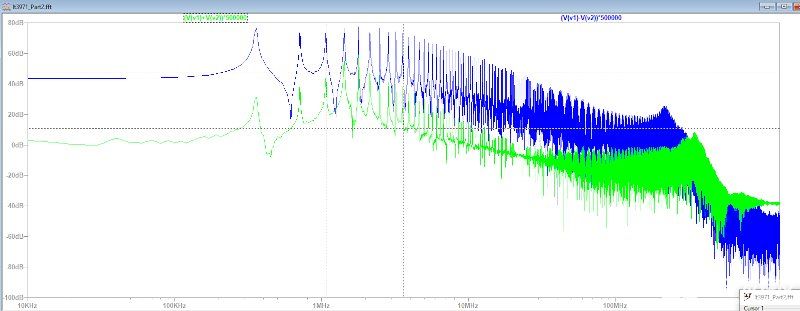

現(xiàn)在使用我們?cè)诘?3 部分中學(xué)習(xí)的公式測(cè)量共模和差模電壓。

VCM = (V1+V2)/2 [eq. 1]

VDM = (V1-V2)/2。[eq.2]

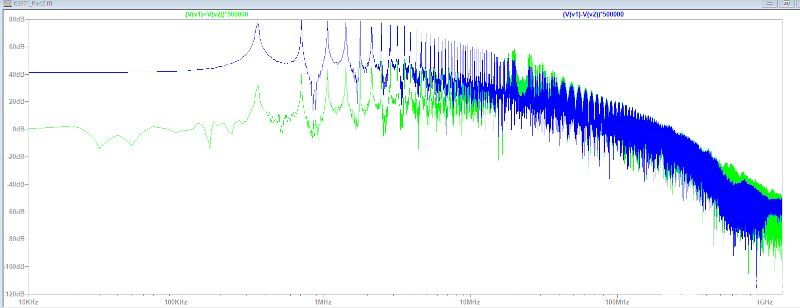

圖 8.共模噪聲。圖片由 Francesco Poderico 提供

使用 LTSpice,可以可視化任何信號(hào)或組合的 FFT。

由于我們正在尋找以 dBuV 為單位的頻率響應(yīng),因此等式。1和當(dāng)量。2 需要乘以 1,000,000 倍。因此它們變?yōu)?(V1+V2)*500000 和 (V1-V2)*500000(所以它已經(jīng)在 udBV 中了)。如果我們想象重疊 EN55022 圖,我們已經(jīng)可以說(shuō)發(fā)射還不錯(cuò)(請(qǐng)注意負(fù)載只有 100 歐姆)。

降低共模噪聲

但是,假設(shè)我們想嘗試降低共模噪聲。我們?cè)趺茨茏龅竭@一點(diǎn)?

我們可以添加一個(gè) CM 扼流圈,如下所示 (L6)。

圖 9. 添加 CM 扼流圈以改善共模噪聲。圖片由Francesco Poderico提供

讓我們看看現(xiàn)在 CM 噪聲與 DM 噪聲相比是否發(fā)生了變化。

圖 10. 共模噪聲現(xiàn)在低于圖 8。圖片由Francesco Poderico提供

哇,有什么區(qū)別。現(xiàn)在我們可以看到共模噪聲和差模噪聲之間的顯著分離。插入L6后,差模噪聲并沒(méi)有太大變化,但差模噪聲卻有顯著降低。L6 仍然不是我在設(shè)計(jì)中選擇的電感,因?yàn)槲曳噶艘粋€(gè)故意的錯(cuò)誤……你能看到嗎?

作為練習(xí),將負(fù)載 R2 減小到至少 0.5 A,然后更改 L6、C1 和 C3 以改善發(fā)射。祝您好運(yùn),我希望您現(xiàn)在擁有一個(gè)強(qiáng)大的工具,讓您 無(wú)需猜測(cè)而是為適當(dāng)?shù)膽?yīng)用選擇適當(dāng)?shù)慕M件,從而更有信心通過(guò) CE。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論