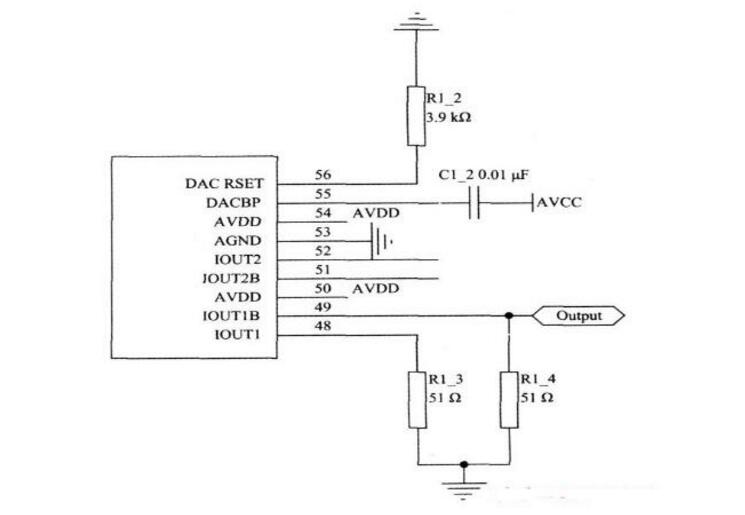

ad9854應用電路圖一:信號發生電路

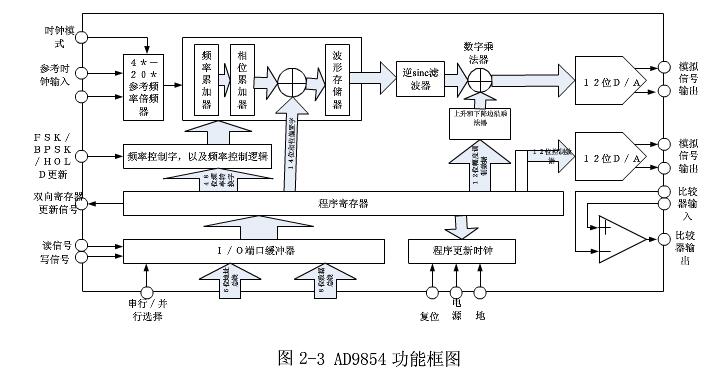

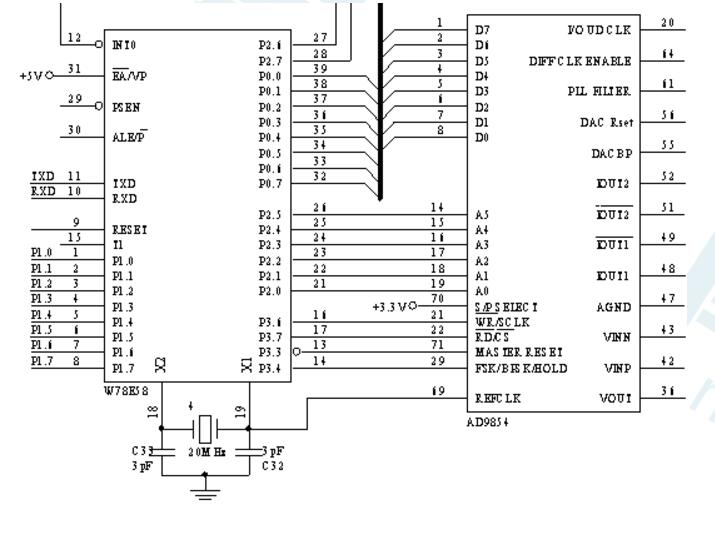

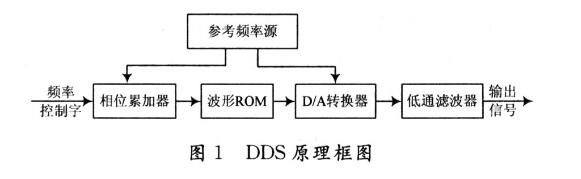

這里采用了AD9854 這款DDS 芯片, 它在300 MHz 時鐘驅動下, 按照乃奎斯特采樣定律可以產生最高150 MHz 的信號,為了得到信號較好的頻率則一般只得到最高100 MHz 的信號。若要得到高于100 MHz 的信號, 則可采用其高次諧波得到。基于AD9854 的信號發生電路如圖 所示:

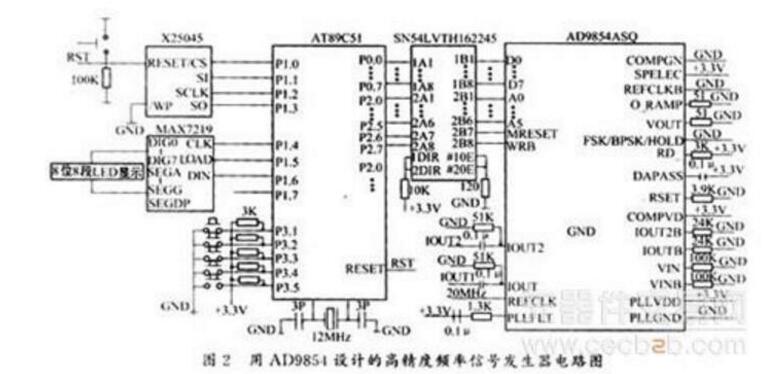

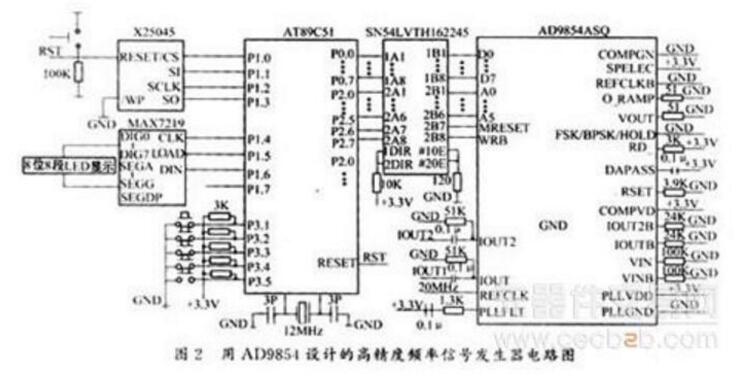

ad9854應用電路圖二:高精度頻率發生器

下面給出一種用AD9854開發高精度頻率信號發生器的簡易方法,開發者只需要熟悉MCS-51單片機編程即可。該系統具有開發周期短,開發成本低的特點,也可以作為探索AD9854功能的一種方法,它的電路原理圖見圖2。

系統主要由DDS芯片AD9854、單片機AT89C51、看門狗定時器X25045和LED顯示驅動芯片MAX7219組成。在這個系統中提供了8位七段LED顯示器,其中前五位為輸出頻率值,顯示范圍為00.000~99.999MHz,后三位為幅度顯示位,顯示范圍為0~999,表示幅值從零幅度到滿幅度的變化。

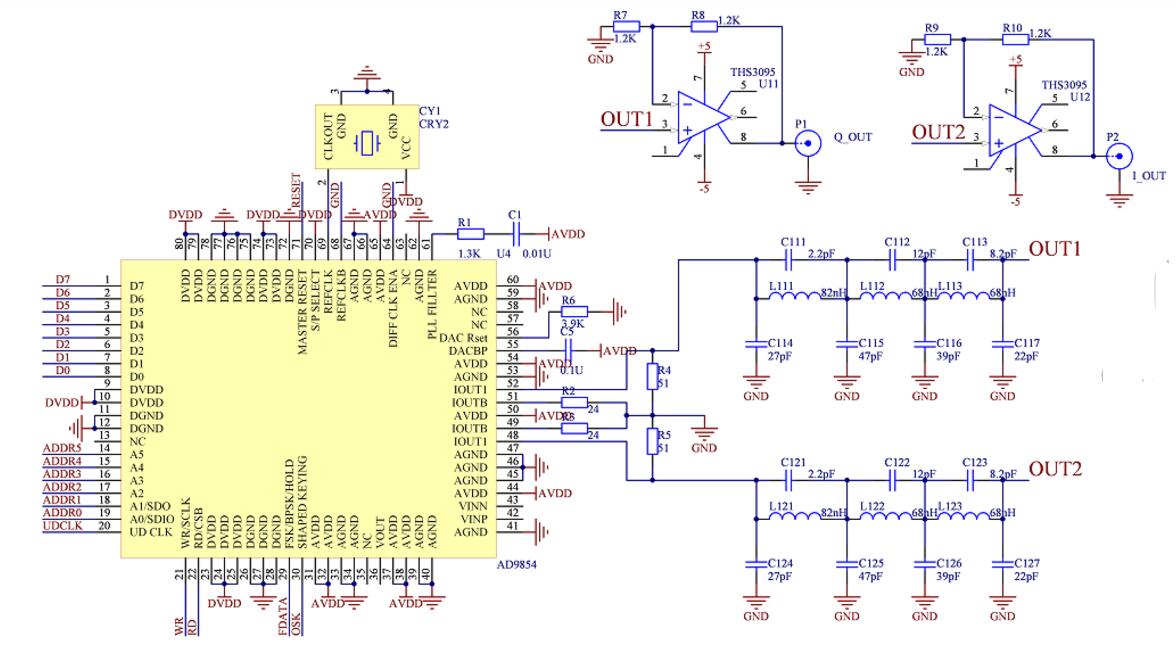

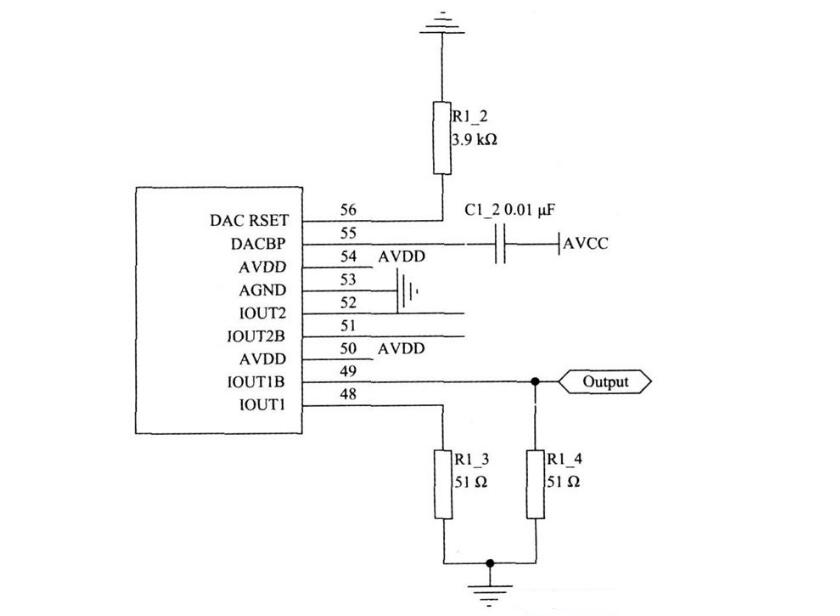

ad9854應用電路圖三:正交信號源

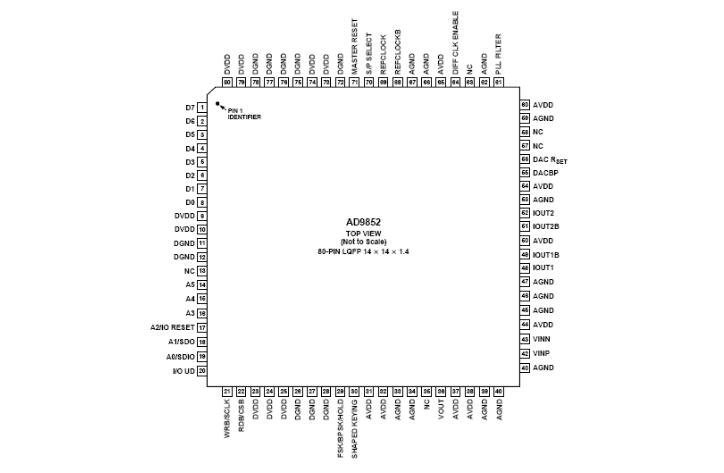

正交信號源選擇了DDS芯片AD9854,具體實現電路見下圖。對AD9854進行編程控制,使之輸出兩路幅度相同并且正交的信號,然后對輸出信號進行濾波,使得正弦波變得更加平滑,濾波之后再把輸出峰值為512mV的信號放大2倍到1.24V。

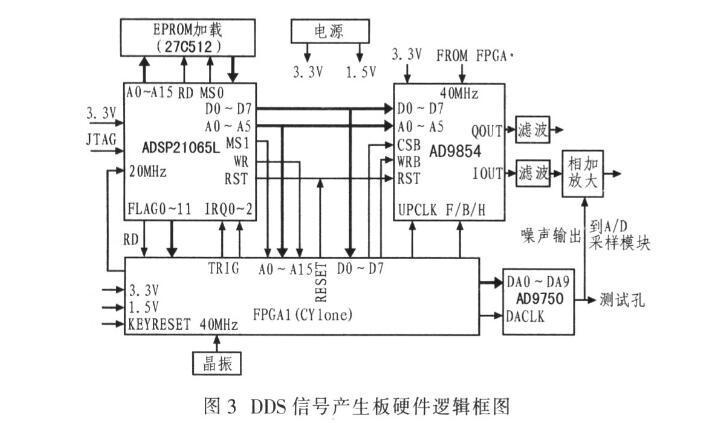

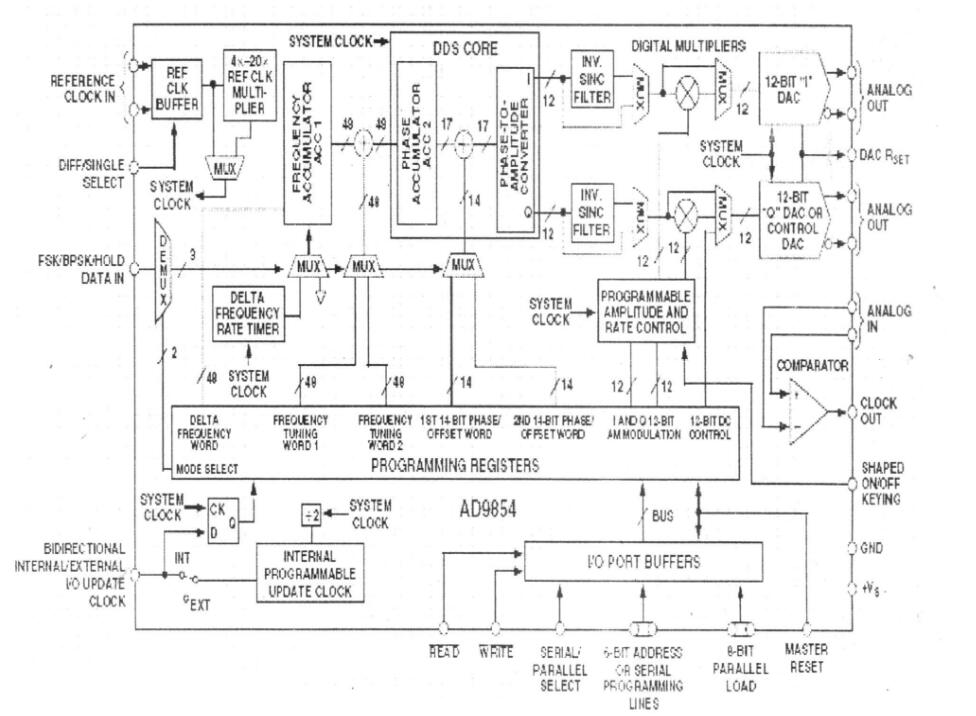

ad9854應用電路圖四:信號產生

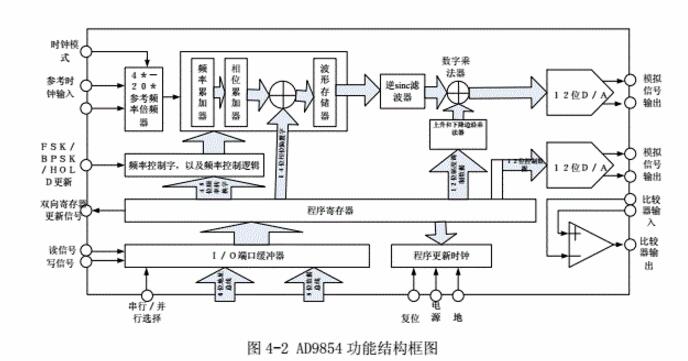

信號產生系統硬件主要有AD9854,ADSP21065L,帶通濾波器,FPGA噪聲產生電路,DDS輸出中頻信號增益控制,噪聲信號相加電路,以及相關的時鐘,電源,FPGA控制等功能單元。DDS模塊主要由AD9854,ADSP21065L和相應的FPGA控制邏輯構成。ADSP21065L根據FPGA的控制時序來設置DDS的工作方式和控制字。圖3為信號產生系統的硬件邏輯框圖。

具體模塊功能說明:

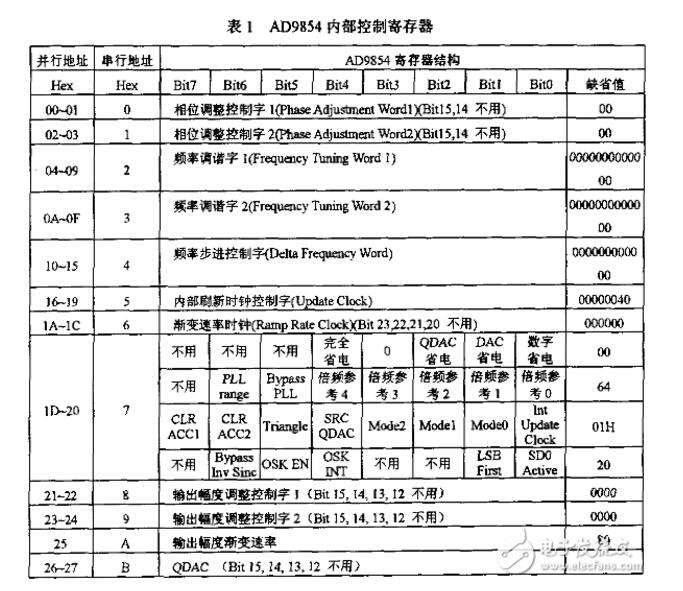

(1)DDS控制模塊 ADSP21065L外部輸入20 MHz時鐘,最高工作在60 MHz,主要控制AD9854,向AD9854寫控制字,中斷輸入IRQ0~IRQ2接FPGA,外部采用上拉電平。其中,一個作為雷達的重頻周期信號,一個作為雷達波形的時序信號,而另一個保留。Flag0~Flag11是雙向輸入引腳,主要為AD9854產生3個控制信號,也可作為外部的輸入控制信號,要求外部可控。ADSP-21065L的外部供電電源為3.3 V,采用板上(REG1117)直流變換器實現。ADSP21065L的加載采用EPROM(27C512)方式,用JTAG調試。FPGA采用Cyclone系列的EP1C3T144,主要產生各種控制信號和時序信號。FPGA的輸出信號有:輸出 1路復位信號到DSP和AD9854,AD9854的控制信號CS、WR、UPCLK和F/B/H。20 MHz的DSP時鐘信號和40 MHz的AD9854時鐘信號。

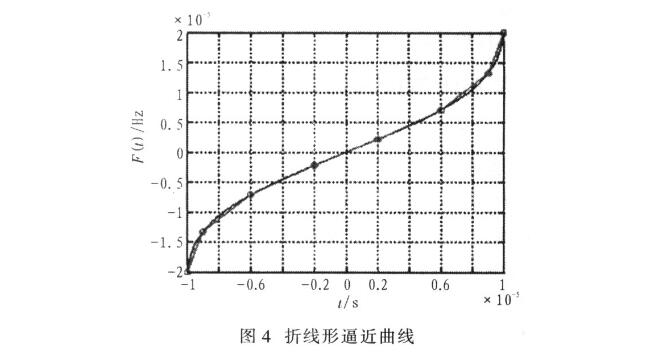

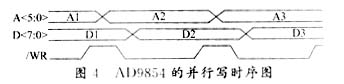

(2)DDS信號產生模塊 DDS AD9854的最高工作頻率是300 MHz,它主要接收ADSP-21065L的控制字,產生脈沖雷達波形。當外部輸入40 MHz時,內部頻率倍增器設置其工作頻率為200 MHz。其工作電壓3.3 V,也可由外部輸入的直流電源經過本板的兩片REG1117型DC-DC變換器變換得到。AD9854有5種可編程的工作模式,選擇一種模式需要編程控制寄存器(并行地址1FH)中的mode0,mode1,mode2。5種可編程的工作模式為:單音調(模式000);非斜升的FSK(模式001);斜升FSK(模式010);線性調頻脈沖(模式011);相位編碼(模式100)。對于NLFM信號,采用線性調頻折線逼近式實現,如圖4所示。因此,將調頻區域分為幾段,每段用不同的線性調頻逼近,即第一段更新頻率字,后面每段起更新頻率增量字,時間增量字就能實現折線型NLFM信號。

(3)電源模塊 該信號產生模塊的輸入電源具有+5 V和-5 V,需要產生3.3 V,1.5 V,利用5片REG1117實現。其中1片為DSP,2片為AD9854,2片分別為FPGA產生3.3 V和1.5 V。若其余的I/O設備也需使用3.3 V,則與FPGA共用。

ad9854應用電路圖五:高精度頻率合成器

AD9854的300M系統時鐘可以通過4X和20X可編程控制電路由較低的外部基準時鐘得到。直接的300M時鐘也可以通過單端或差分輸入。AD9854還有單腳輸入的常規FSK和改進的斜率FSK輸出。

ad9854相關文章:

ad9854中文資料匯總(ad9854引腳圖及功能_內部結構及應用電路)

ad9854相關下載:

電子發燒友App

電子發燒友App

評論