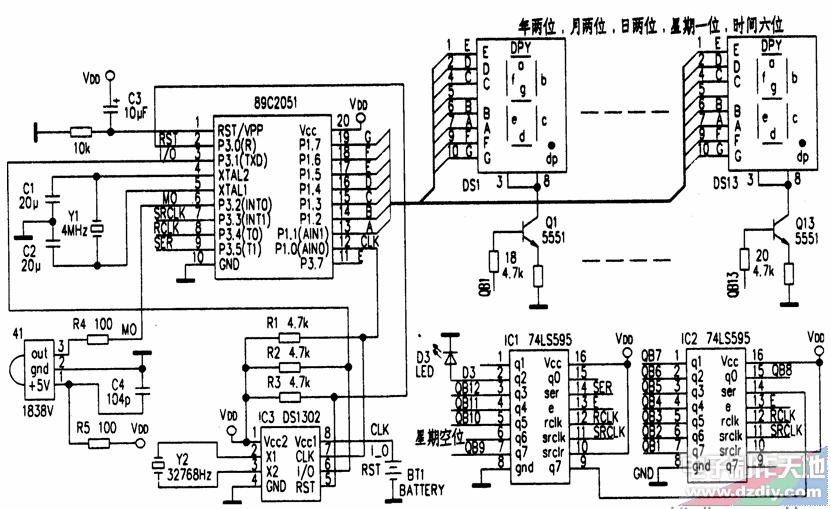

硬件電路設計

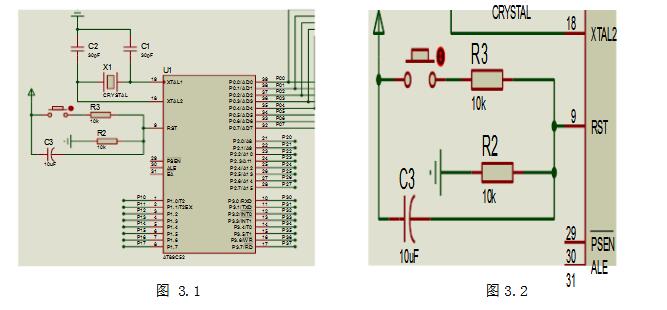

單片機最小系統

本系統以AT89C52單片機為核心,本系統選用12MHZ的晶振,使得單片機有合理的運行速度。起振電容30pF對振蕩器的頻率高低、振蕩器的穩定性和起振的快速性影響較合適,復位電路為按鍵高電平復位。AT89C52單片機最小系統電路設計如圖3.1所示:

復位電路

單片機復位的條件是當單片機振蕩器工作時,RST引腳上出現持續兩個機器周期的高電平,從而實現復位操作,使單片機回復到初始狀態。上電時,考慮到振蕩器有一定的起振時間,RST引腳上高電平必須持續10ms以上才能保證有效復位。 STC89C52的復位是由外部的復位電路來實現的。電路圖如圖3.2。

晶振電路

晶振的作用是為系統提供基本的時鐘信號。晶振電路中接在晶振旁的兩個電容,叫負載電容。一般單片機的晶振工作于并聯諧振狀態,也可以理解為諧振電容的一部分。電容值無嚴格要求,但電容取值對振蕩頻率輸出的穩定性、大小、振蕩電路起振速度有少許影響,C2、C3可在30pF時振蕩器有較高的頻率穩定性電路圖如圖3.3。

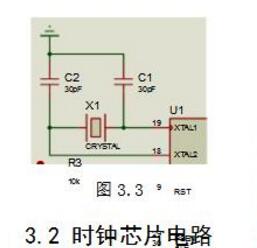

本系統采用DS12C887時鐘芯片定時及計時功能,DS12C887時鐘芯片共需要13條信號線。GND、 VCC:直流電源,其中VCC接+5V輸入,GND接地,當VCC輸入為+5V時,用戶可以訪問DS12C887內RAM中的數據,并可對其進行讀、寫操作;當VCC的輸入小于+4.25V時,禁止用戶對內部RAM進行讀、寫操作,此時用戶不能正確獲取芯片內的時間信息;當VCC的輸入小于+3V時,DS12C887會自動將電源發換到內部自帶的鋰電池上,以保證內部的電路能夠正常工作 MOT:模式選擇腳。SQW:方波輸出腳,當供電電壓VCC大于4.25V時,SQW腳可進行方波輸出。AD0~AD7:復用地址數據總線,該總線采用分時復用技術,在總線周期的前半部分,出現在AD0~AD7上的是地址信息,可用以選通DS12C887內的RAM,總線周期的后半部分出現在AD0~AD7上的數據信息 AS:地址選通輸入腳。DS/RD:數據選擇或讀輸入腳,該引腳有兩種工作模式,當MOT接VCC時,選用Motorola工作模式,在這種工作模式中,每個總線周期的后一部分的DS為高電平。

在讀操作中,DS的上升沿使DS12C887將內部數據送往總線AD0~AD7上,以供外部讀取在寫操作中,DS的下降沿將使總線 AD0~AD7上的數據鎖存在DS12C887中。當MOT接GND時,選用Intel工作模式,在該模式中,該引腳是讀允許輸入腳 R/W:讀/寫輸入端,該管腳也有2種工作模式,當MOT接VCC時,R/W工作在Motorola模式CS:片選輸入,低電平有效 IRQ:中斷請求輸入,低電平有效,該腳有效對DS12C887內的時鐘、日歷和RAM中的內容沒有任何影響,僅內部的控制寄存器有影響,在典型的應用中,RESET可以接VCC,這樣可以保證DS12C887在掉電時,其內部控制寄存器不受影響。

DS12C887電路如圖3.4所示:

液晶顯示器LM016L的VSS腳接地,VDD腳接電源,VEE腳接一可變電阻接地,RS腳接單片機P3.5腳,E腳接單片機P3.4腳,D0至D7腳接單片機的P2.0至P2.7腳。液晶顯示器LM016L電路圖如圖3.5。

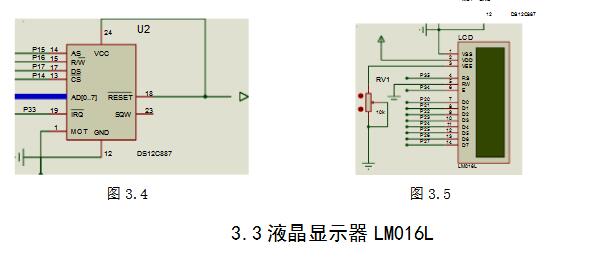

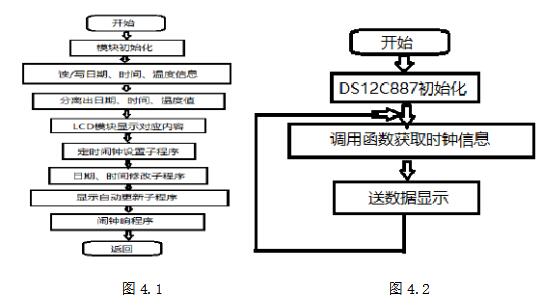

軟件體統設計

主程序流程圖如圖4.1

DS12C887程序流程圖如圖4.2。

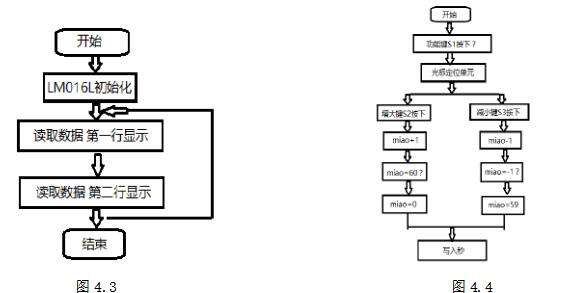

LM016L程序流程圖如圖4.3

電子發燒友App

電子發燒友App

評論