本文為大家?guī)砦蹇?span style="font-size: 12px;">五人表決器電路設(shè)計(jì)方案。

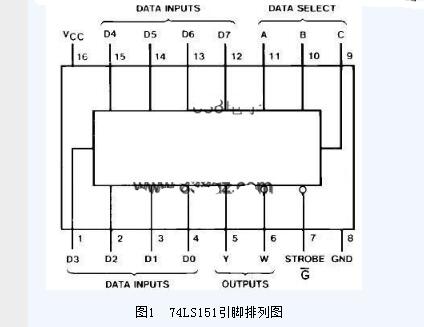

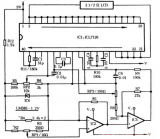

五人表決器電路設(shè)計(jì)方案一:基于74LS151設(shè)計(jì)的五人表決器電路

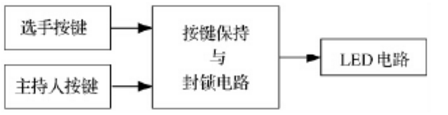

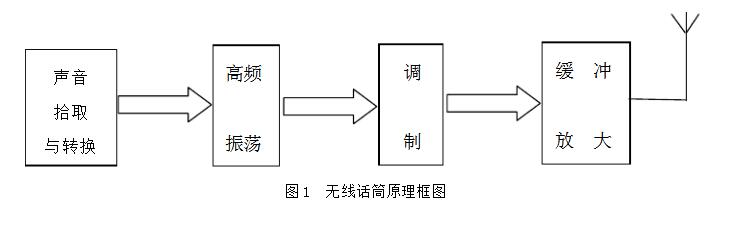

系統(tǒng)原理

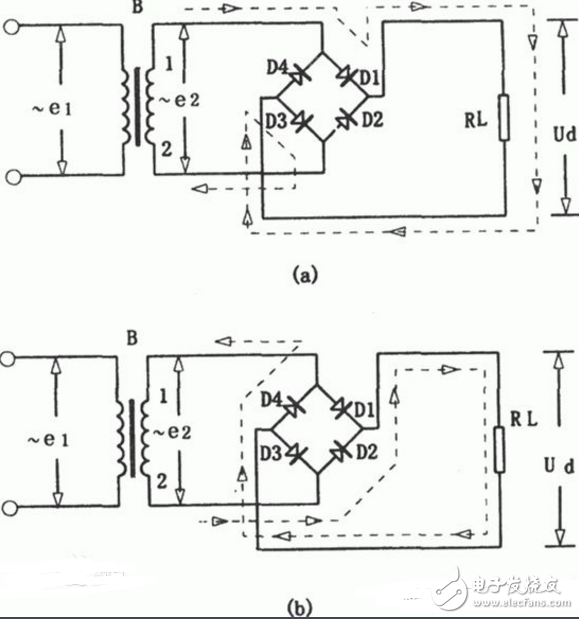

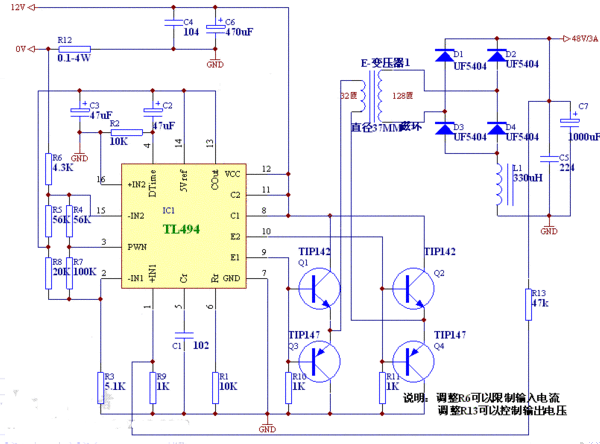

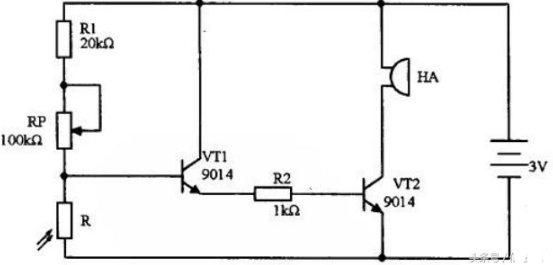

五人表決器,只要贊成人數(shù)大于或等于三,則表決通過。因此,只需將每位表決人的結(jié)果相加,判斷結(jié)果值。設(shè)五個(gè)開關(guān)A、B、C、D、E作為表決器的五個(gè)輸入變量,輸入變量為邏輯“1”時(shí),表示表決者“贊成”,紅燈亮;輸入變量為“0”時(shí),表示表決者“不贊成”,紅燈不亮;輸出邏輯“1”時(shí),表示表決“通過”,綠燈亮;輸出邏輯“0”時(shí),表示表決“不通過”,綠燈不亮;當(dāng)表決器的五個(gè)輸入變量中有3個(gè)以上(含3個(gè))為“1”時(shí),則表決器輸出為“1”,此時(shí)綠燈就亮了。

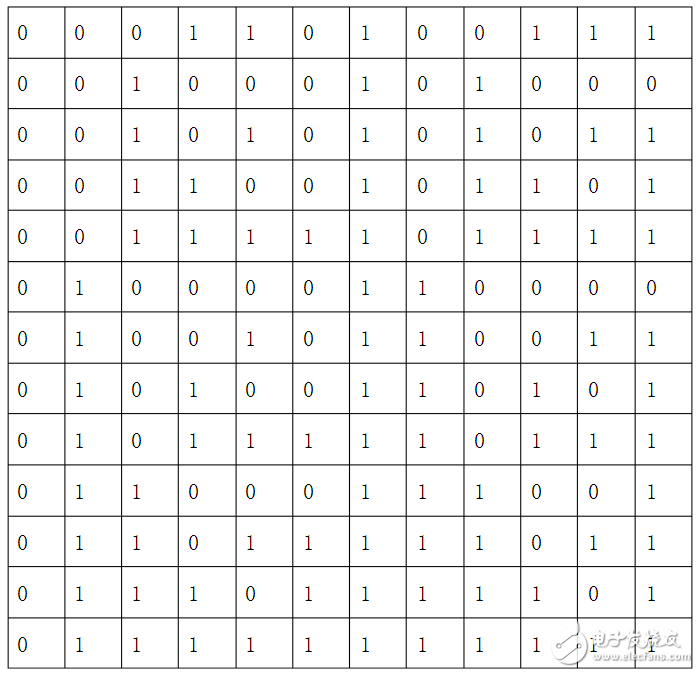

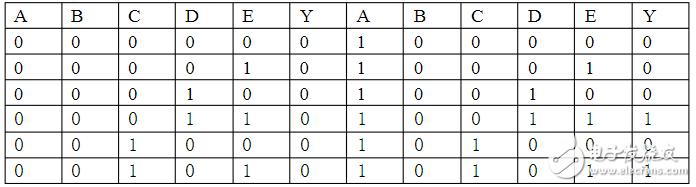

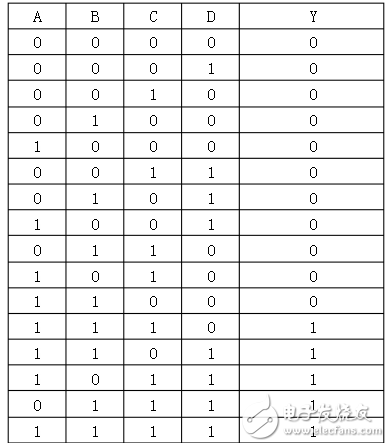

真值表

如果綠燈亮了,則表示表決通過,若綠燈不亮了,表示不通過。

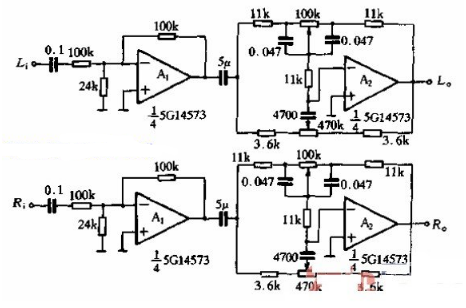

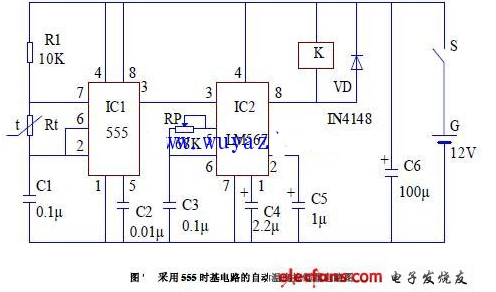

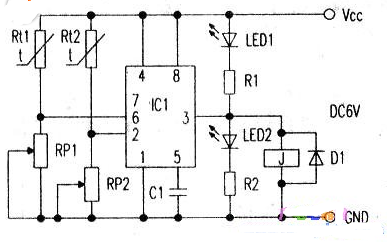

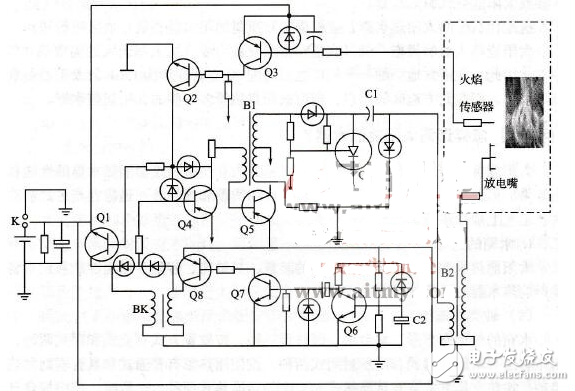

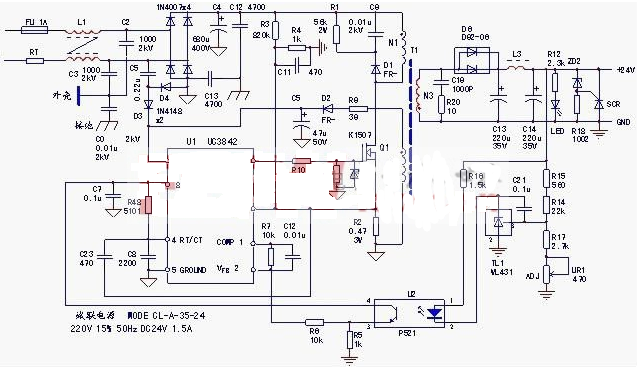

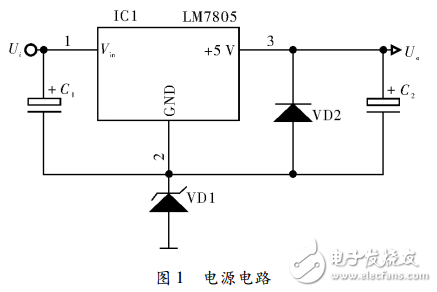

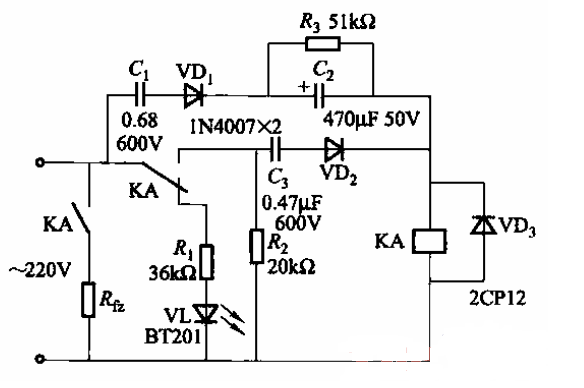

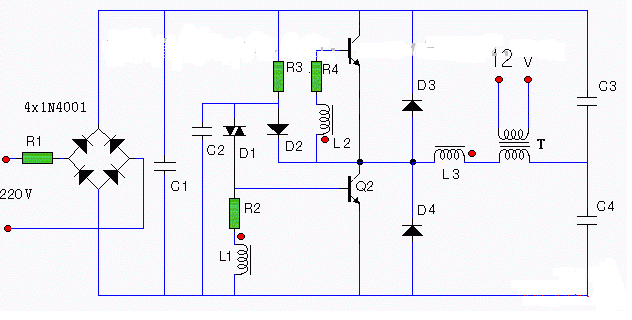

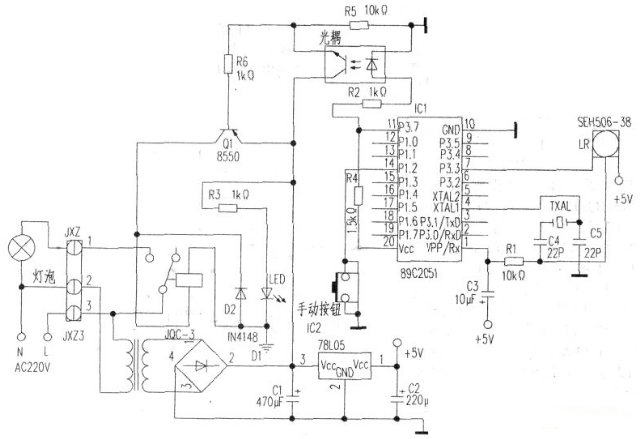

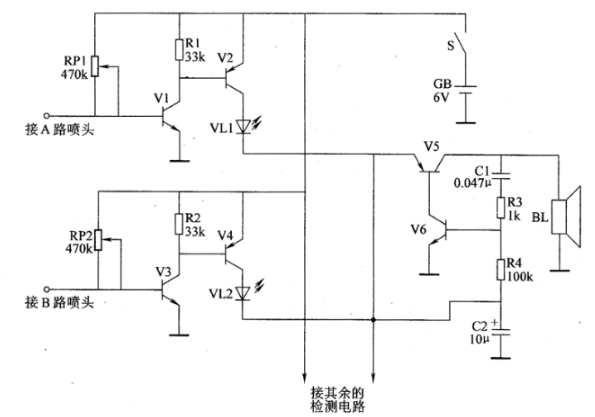

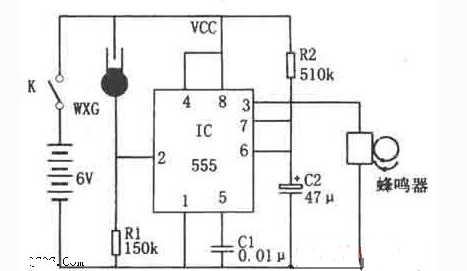

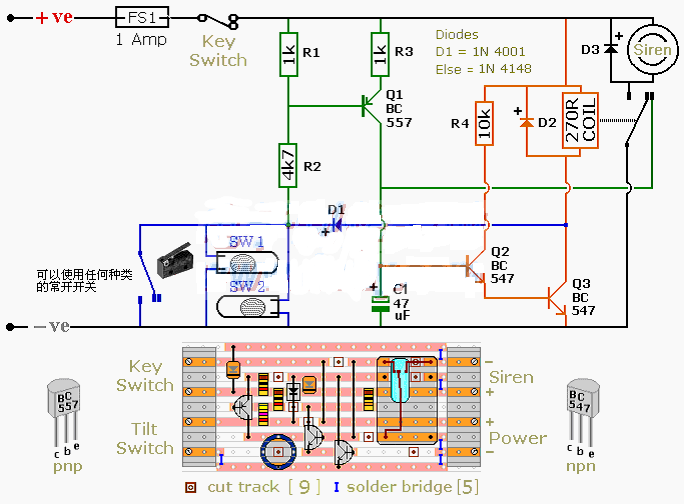

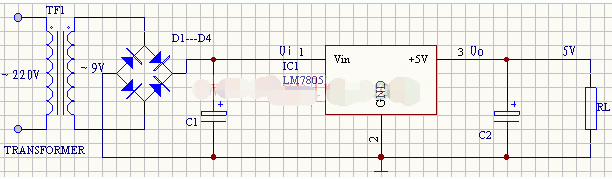

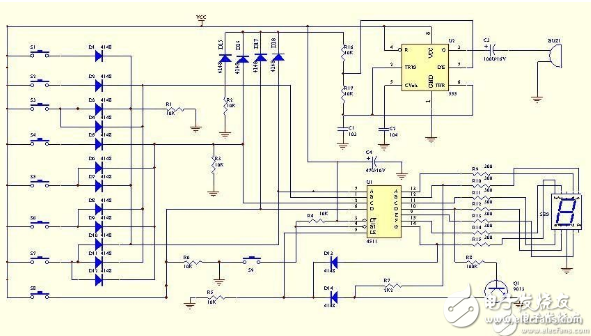

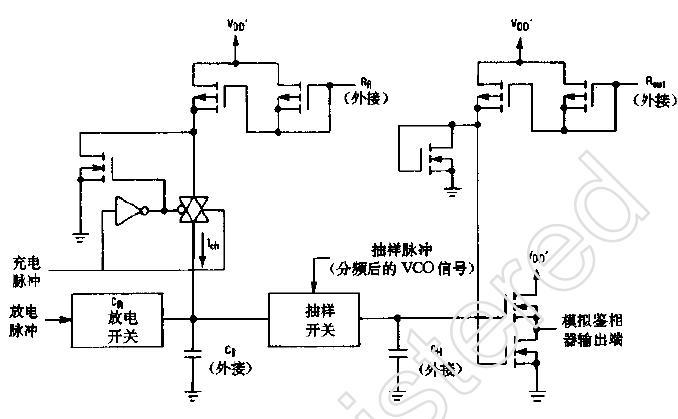

電路設(shè)計(jì)

原理圖

五人表決器電路設(shè)計(jì)方案二:verilog 五人表決器

程序設(shè)計(jì)

module vote5(a,b,c,d,e,f);

input a,b,c,d,e;

output f; reg f;

reg[2:0] count1;

initial count1=0;

always@(a,b,c,d,e)

begin

count1《=a+b+c+d+e;

f=count1《3?0:1;

end

endmodule

測(cè)試程序

module test;

reg a;

reg b;

reg c;

reg d;

reg e;

wire f;

vote5 uut (

.a(a),

.b(b),

.c(c),

.d(d),

.e(e),

.f(f) );

initial begin

a = 0;

b = 0;

c = 0;

d = 0;

e = 0;

#100

a = 1;

b = 0;

c = 0;

d = 0;

e = 0;

#100

a = 1;

b = 1;

c = 0;

d = 0;

e = 0;

#100

a = 1;

b = 1;

c = 1;

d = 0;

e = 0;

#100

a = 1;

b = 1;

c = 1;

d = 1;

e = 0;

#100

a = 1;

b = 1;

c = 1;

d = 1;

e = 1;

end

endmodule

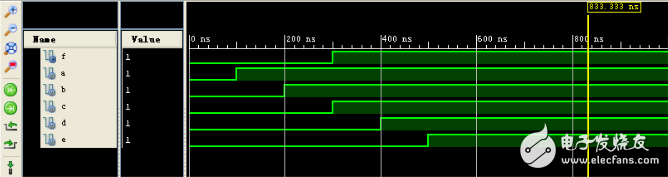

仿真圖

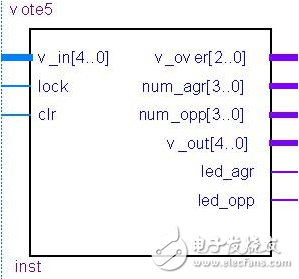

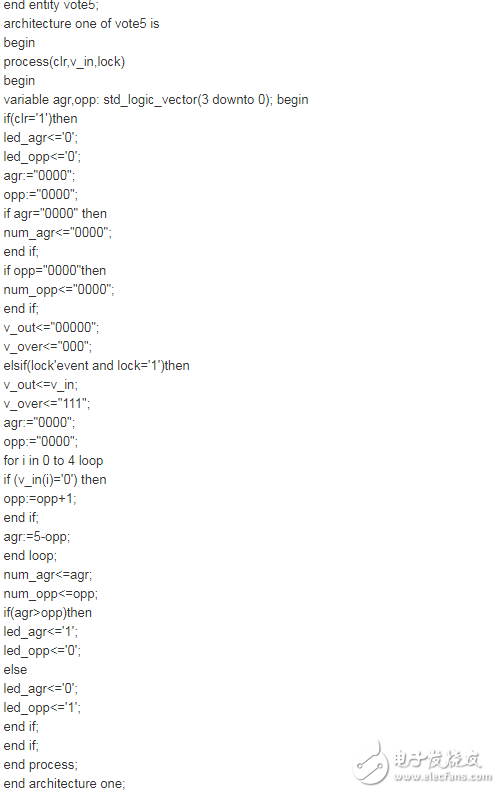

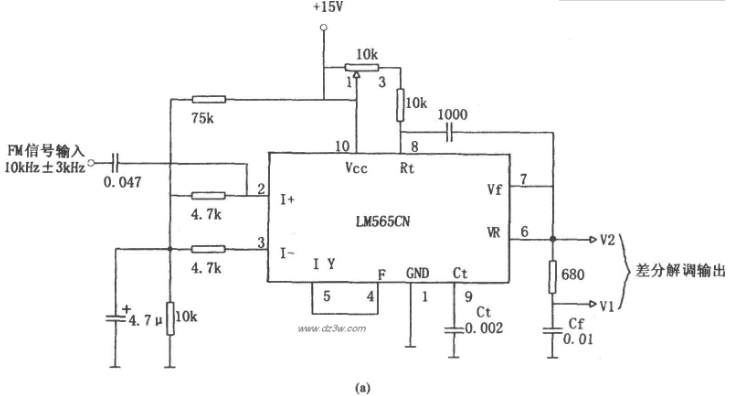

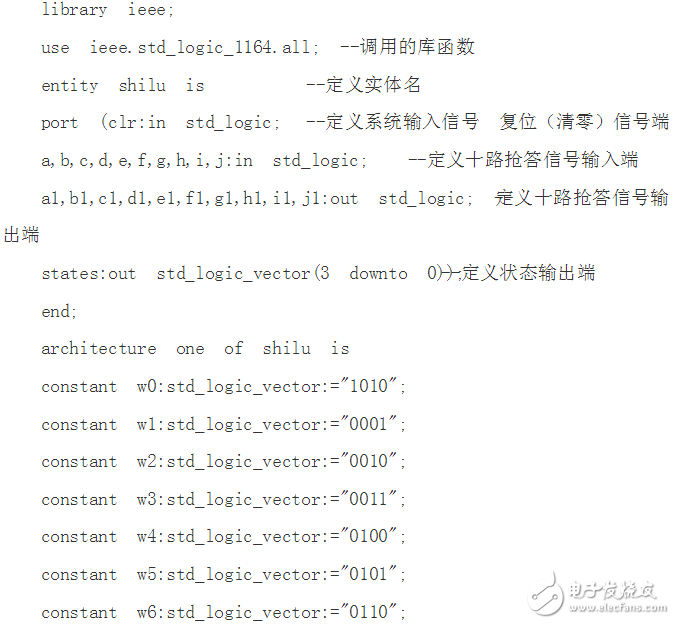

五人表決器電路設(shè)計(jì)方案三:VHDL編程的五人表決器

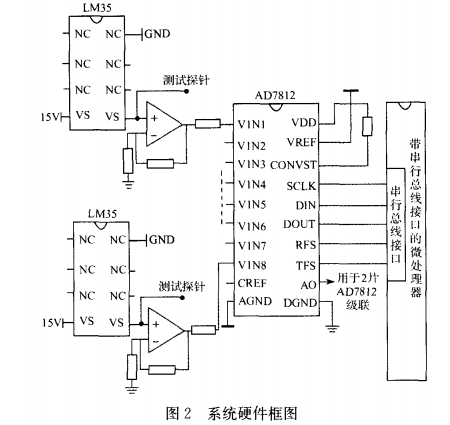

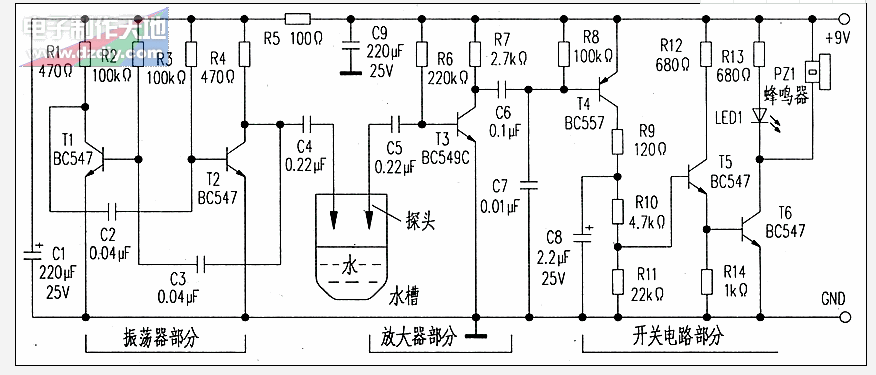

用實(shí)驗(yàn)平臺(tái)的LED 發(fā)光陣列實(shí)現(xiàn)表決結(jié)果和每人的表決信號(hào)。要求LED1顯示判決贊成(led_agr)信號(hào),LED8顯示判決反對(duì)(led_opp)信號(hào)。LED3、LED4、LED5同時(shí)顯示判決結(jié)束信號(hào)。LED10、LED11、LED12、LED13、LED14顯示5人的表決信號(hào)。

當(dāng)系統(tǒng)啟動(dòng)后,數(shù)碼管5、6分別顯示“FF ”字樣,所有用到的數(shù)碼管熄滅,表決開始,用戶此時(shí)可以通過撥動(dòng)開關(guān)輸入5人的表決意見,并通過LED10~LED14分別顯示出來,當(dāng)用戶按下lock 按鍵(按鍵6) 后,LED10~LED14的狀態(tài)被鎖存,LED3、LED4、LED5同時(shí)點(diǎn)亮,此時(shí)無論如何輸入表決意見LED10~LED14的狀態(tài)都不會(huì)改變,同時(shí)系統(tǒng)會(huì)計(jì)算出來贊成的人數(shù)和反對(duì)的人數(shù),并分別用數(shù)碼管5、6顯示出來,而且系統(tǒng)會(huì)計(jì)算出來贊成的人數(shù)和反對(duì)的人數(shù)的大小關(guān)系,并通過LED1和LED8顯示出來最終判決的表決結(jié)果(判決贊成:LED1亮;判決反對(duì):LED8亮) 。此時(shí)用戶按下清除鍵clr(按鍵7) 后,系統(tǒng)又恢復(fù)成為剛啟動(dòng)狀態(tài)。

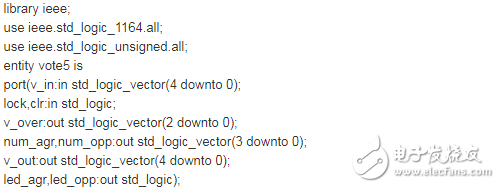

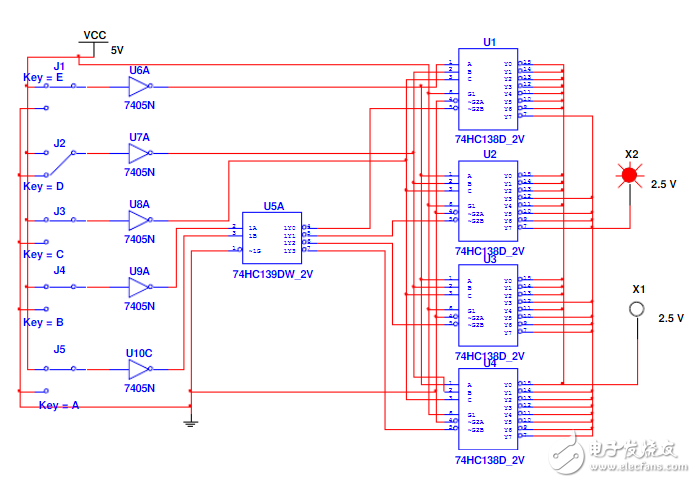

源代碼

仿真圖

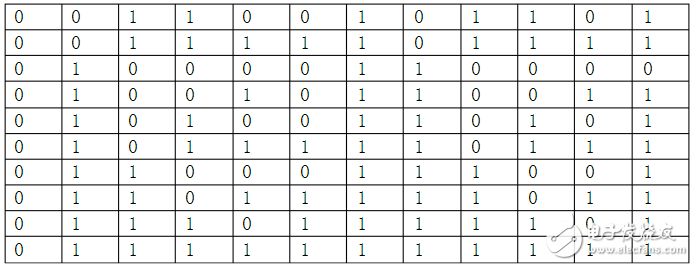

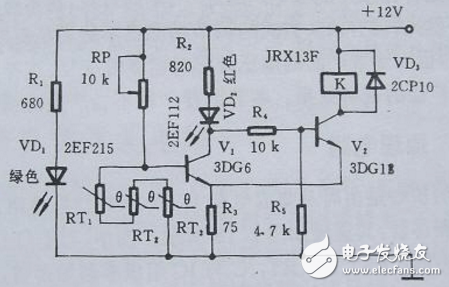

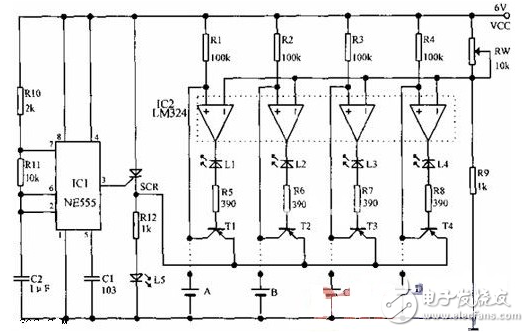

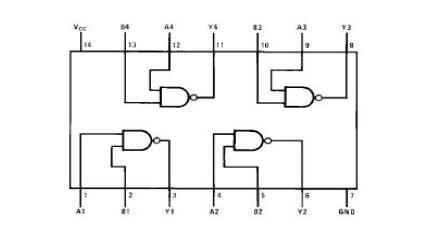

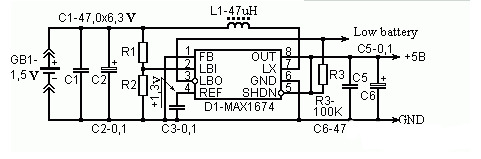

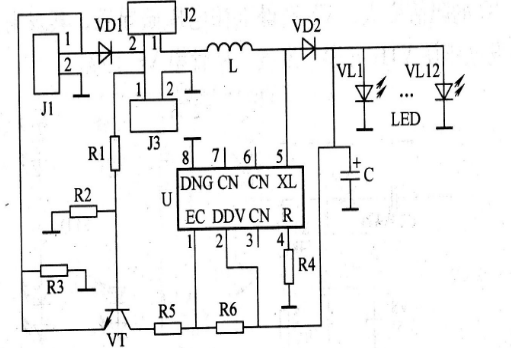

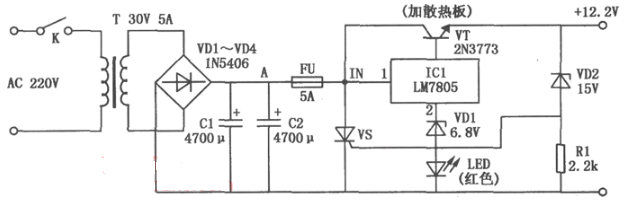

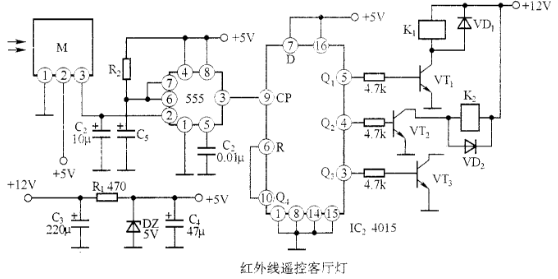

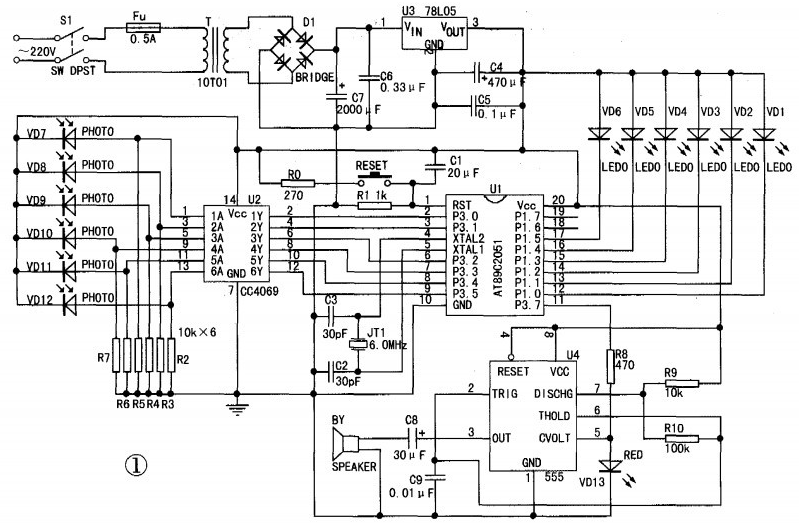

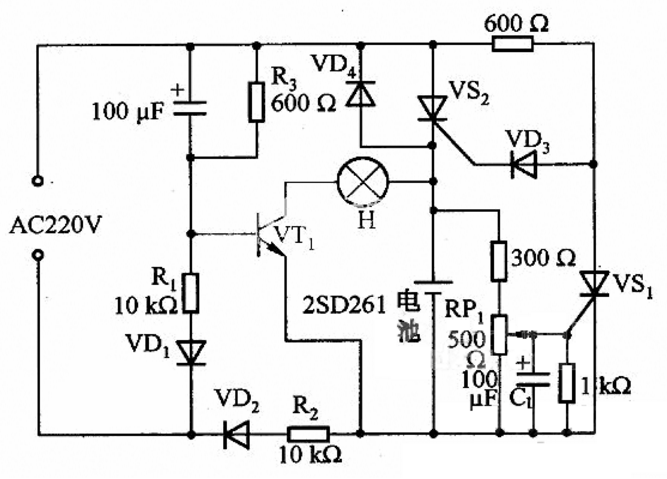

五人表決器電路設(shè)計(jì)方案四:基于74HC138的五人表決器

對(duì)于五人表決器,首先設(shè)五人分別為A B C D E 設(shè)Y為表決的結(jié)果。其中有三人或三人以上同意(同意用“1”表示,不同意用“0”表示)則紅燈亮 (紅燈用“1”表示),綠燈亮(綠燈用“0”表示)。如果紅燈亮了,則表示表決通過,若綠燈亮了,表示不通過。

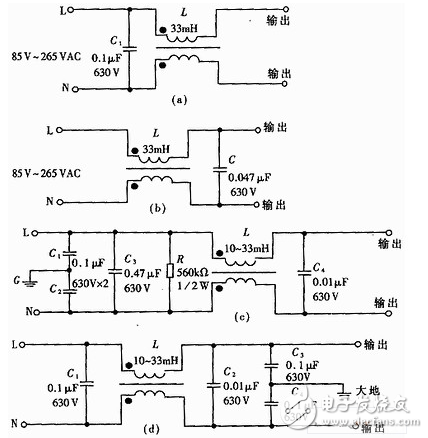

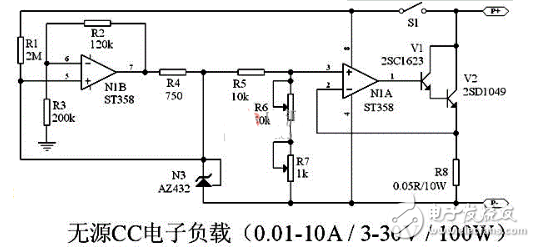

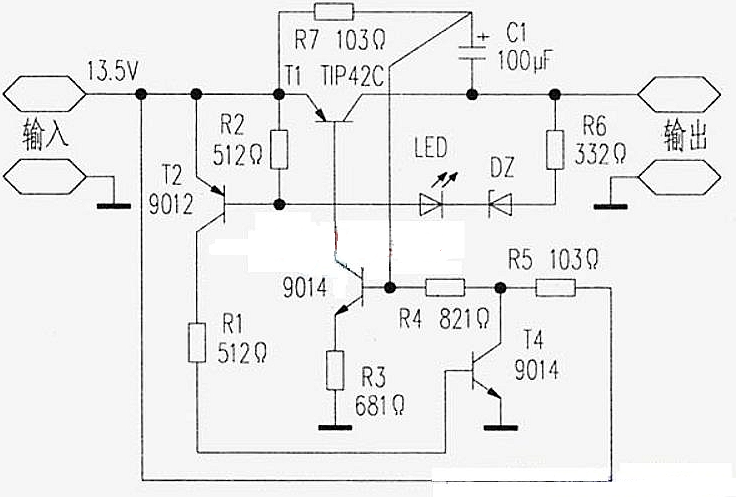

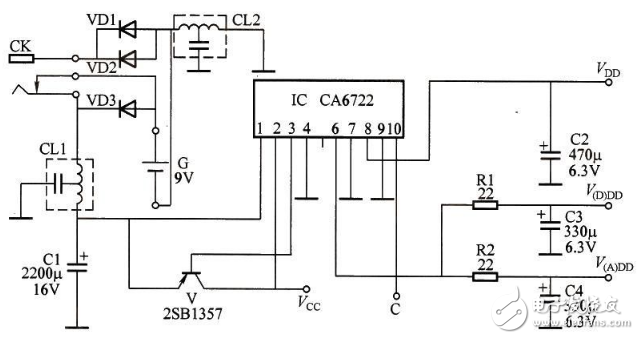

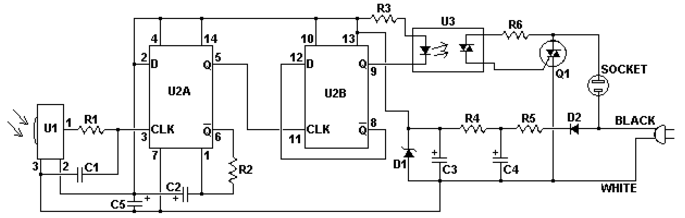

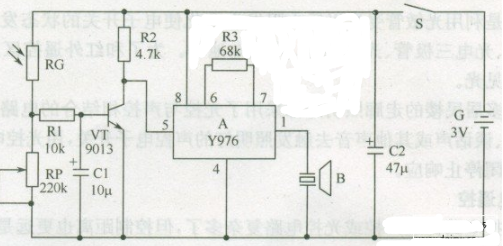

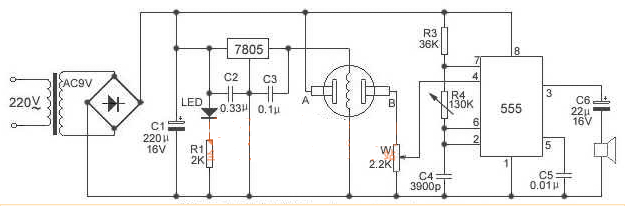

電路圖設(shè)計(jì)

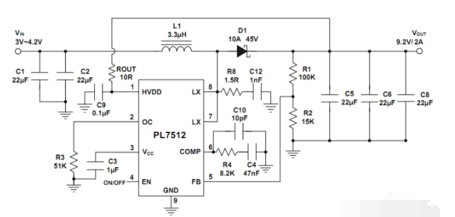

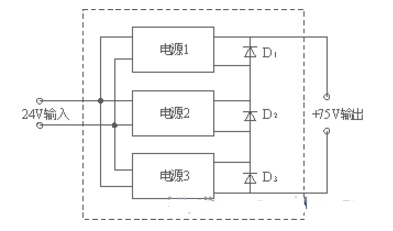

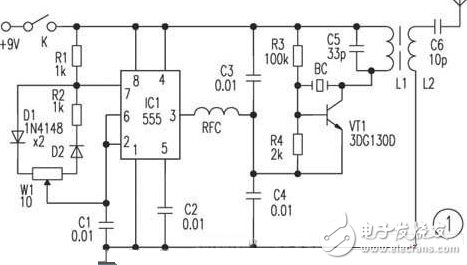

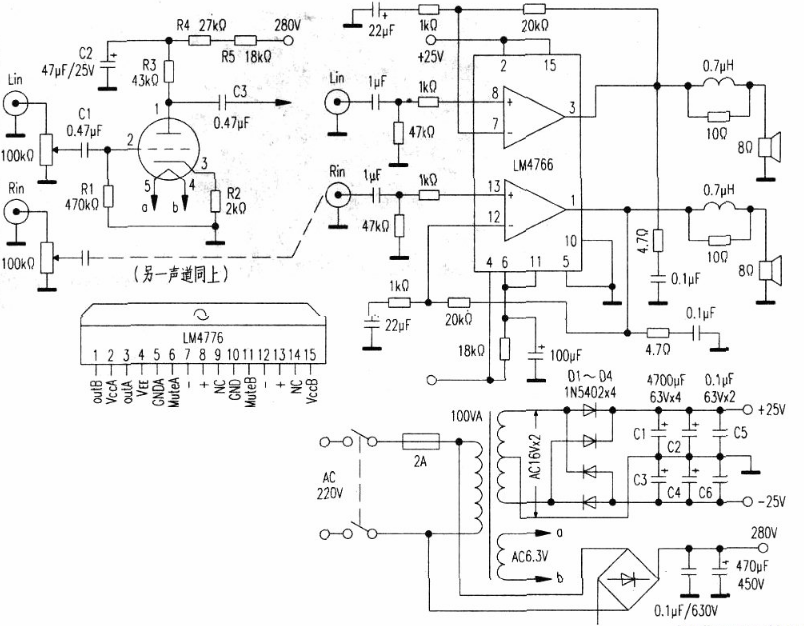

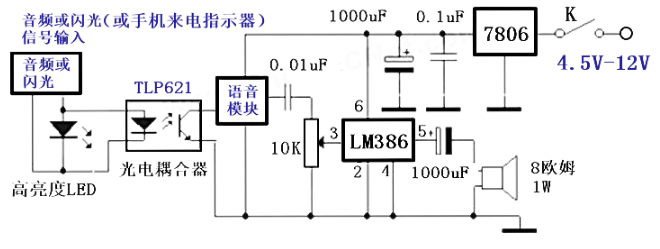

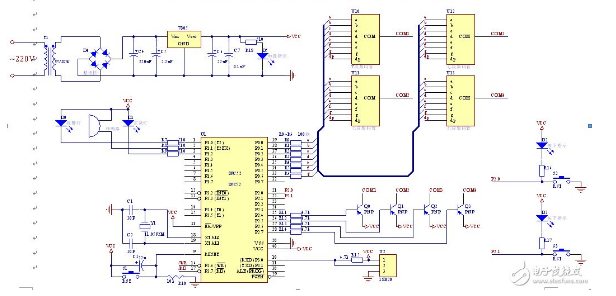

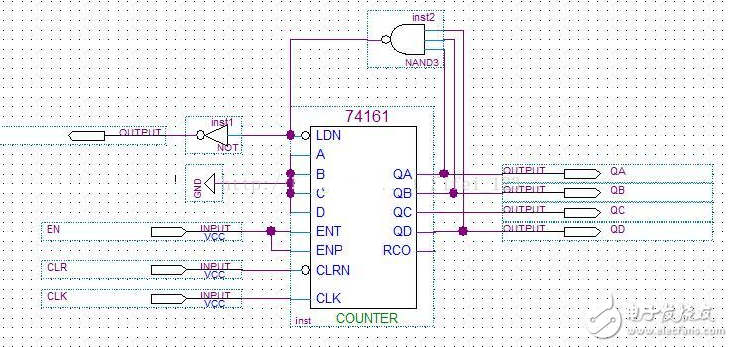

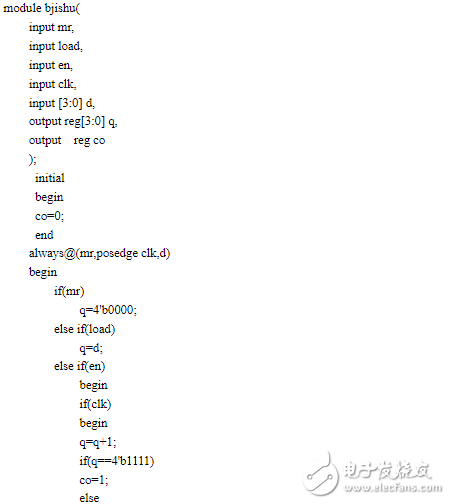

五人表決器電路設(shè)計(jì)方案五:基于FPGA的五人表決器

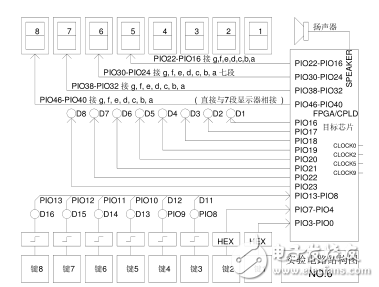

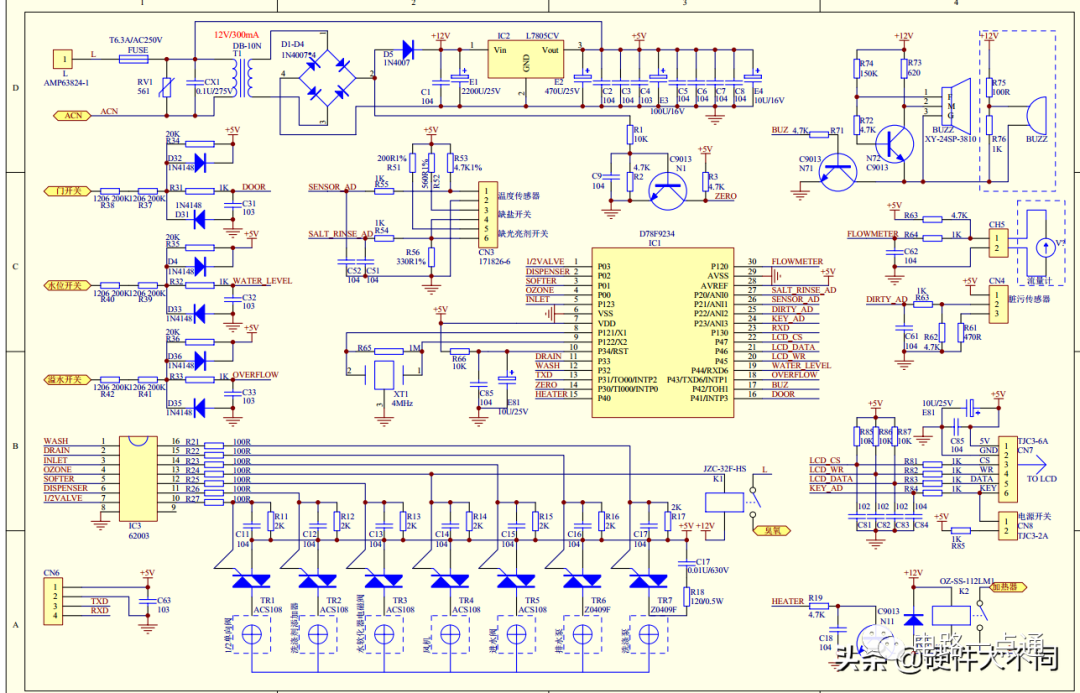

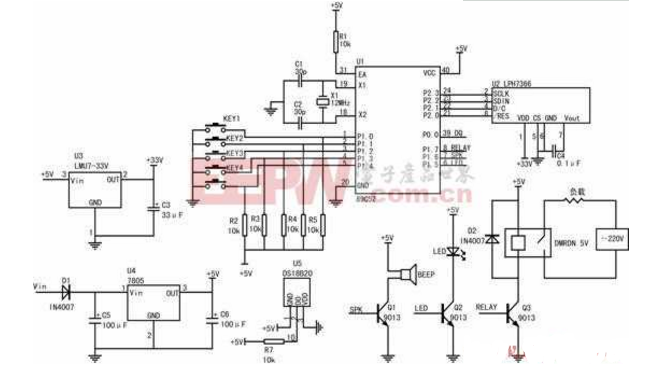

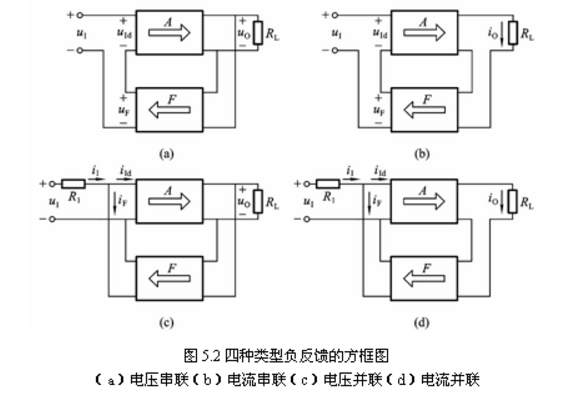

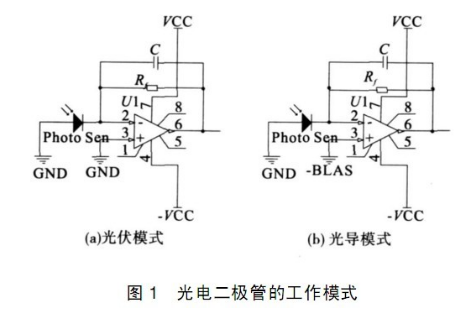

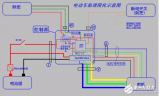

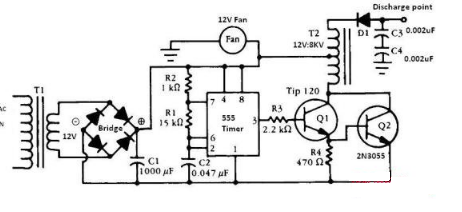

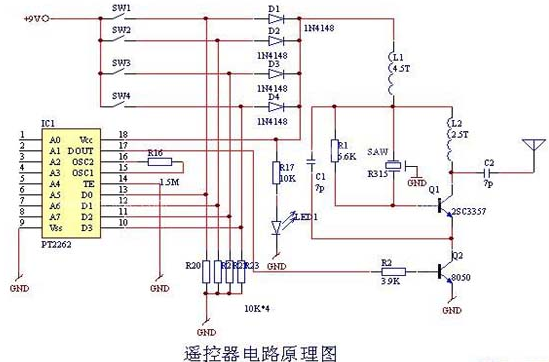

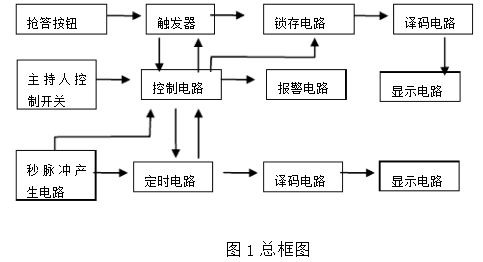

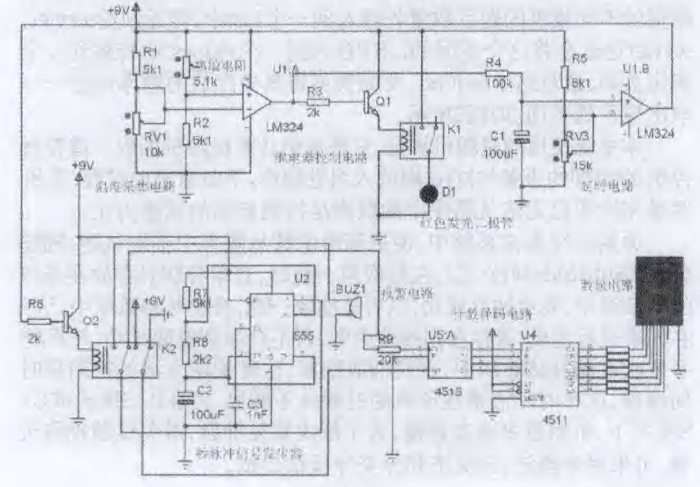

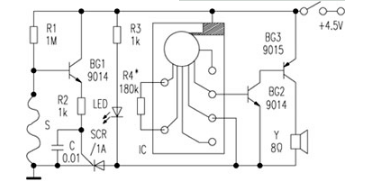

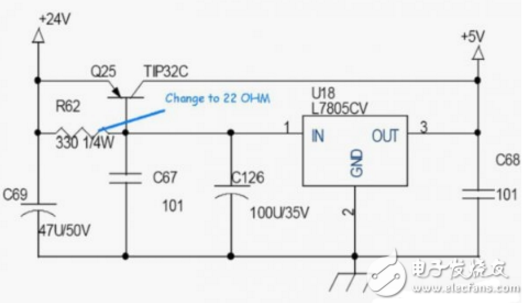

電路原理圖

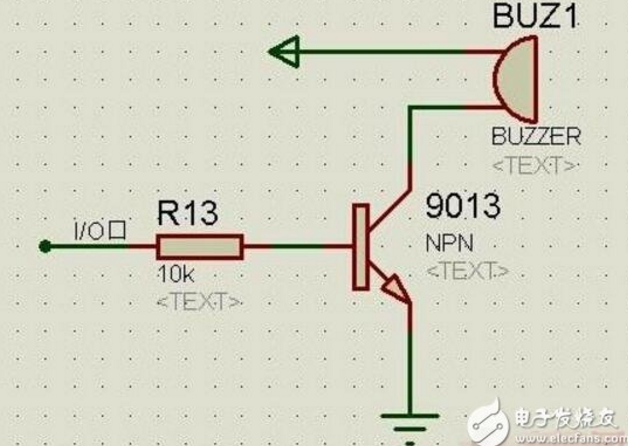

此電路圖可實(shí)現(xiàn)表決器的控制與顯示。鍵8 到鍵2 分別為五位投票者和復(fù)位,開始鍵。通過數(shù)碼管顯示投票人數(shù),和剩余時(shí)間。二極管D8 顯示通過與不通過。

引腳鎖定

仿真

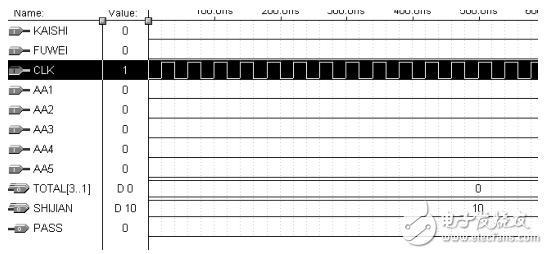

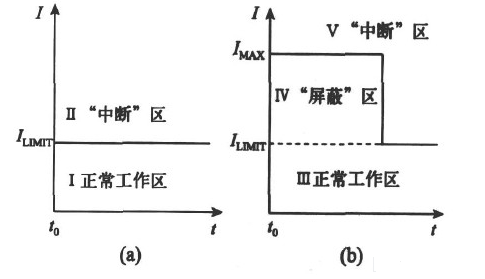

當(dāng)處于復(fù)位狀態(tài)時(shí),外界的輸入對(duì)結(jié)果沒有影響。故時(shí)間仍為10 秒,輸出統(tǒng)計(jì)人數(shù)為0。仿真波形如下圖所示。

復(fù)位時(shí)的模擬結(jié)果

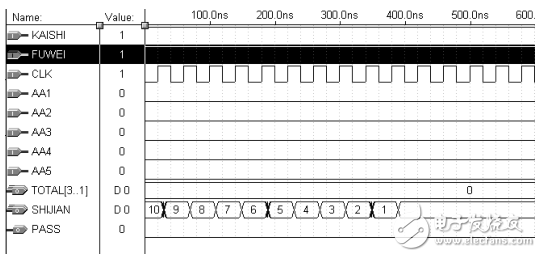

在非復(fù)位狀態(tài)下,主持人按下開始鍵。表決開始。在沒有人投票的情況下。時(shí)間變?yōu)?。表決結(jié)束。仿真波形如下圖所示。

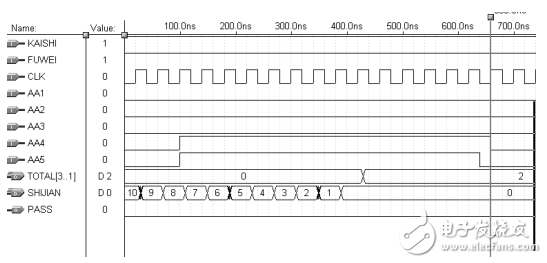

無人贊成時(shí)的模擬結(jié)果

在非復(fù)位狀態(tài)下,主持人按下開始鍵。表決開始。當(dāng)超出表決時(shí)間時(shí)才進(jìn)行表決,此表決無效。仿真波形如下圖所示。

規(guī)定時(shí)間外的模擬結(jié)果

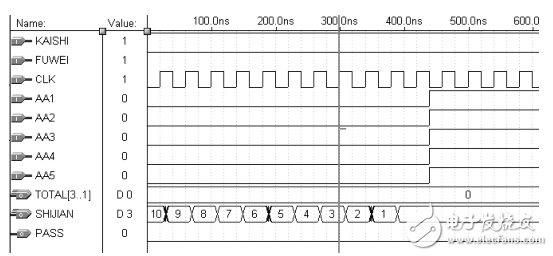

在非復(fù)位狀態(tài)下,主持人按下開始鍵。表決開始。在規(guī)定時(shí)間內(nèi)只有兩人贊同。仿真波形如下圖所示。

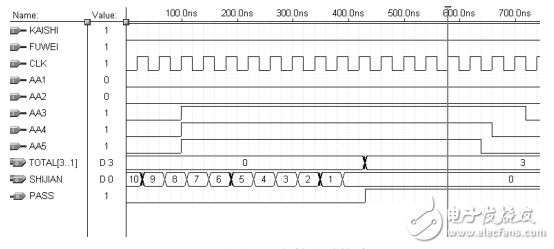

兩人贊成時(shí)的結(jié)果

在非復(fù)位狀態(tài)下,主持人按下開始鍵。表決開始。在規(guī)定時(shí)間內(nèi)只有三人贊同。仿真波形如下圖所示。

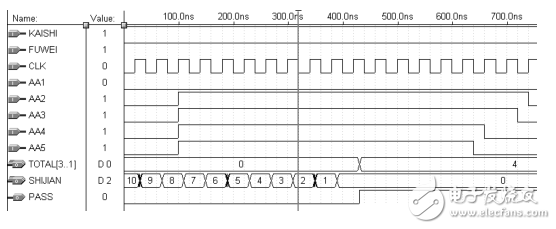

三人贊成時(shí)的結(jié)果

在非復(fù)位狀態(tài)下,主持人按下開始鍵。表決開始。在規(guī)定時(shí)間內(nèi)只有四人贊同。仿真波形如下圖所示。

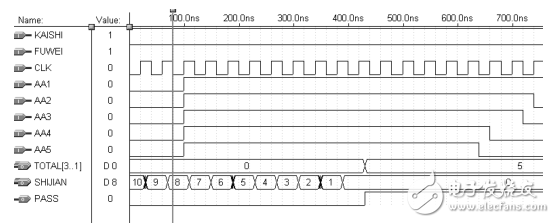

四人贊成時(shí)的結(jié)果

在非復(fù)位狀態(tài)下,主持人按下開始鍵。表決開始。在規(guī)定時(shí)間內(nèi)只有五人贊同。仿真波形如下圖所示。

五人贊成時(shí)的結(jié)果

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論