該系統(tǒng)可以完成圖像的采集、處理和顯示,從而實現(xiàn)目標識別與跟蹤的智能信號處理。該系統(tǒng)是對攝像機數(shù)字,模擬兩路視頻數(shù)據(jù)進行采集,處理后通過PCI總線在PC機上顯示出來。

視頻信號采集模塊

攝像機提供兩路視頻信號:一路模擬視頻,一路數(shù)字視頻。

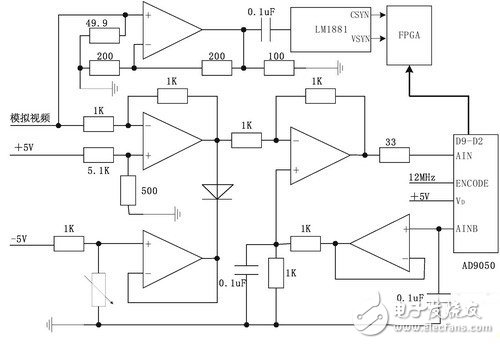

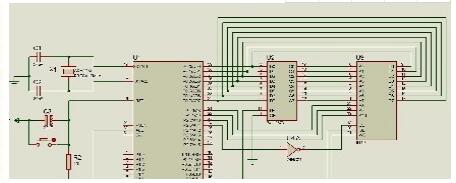

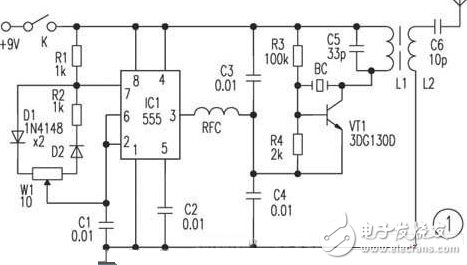

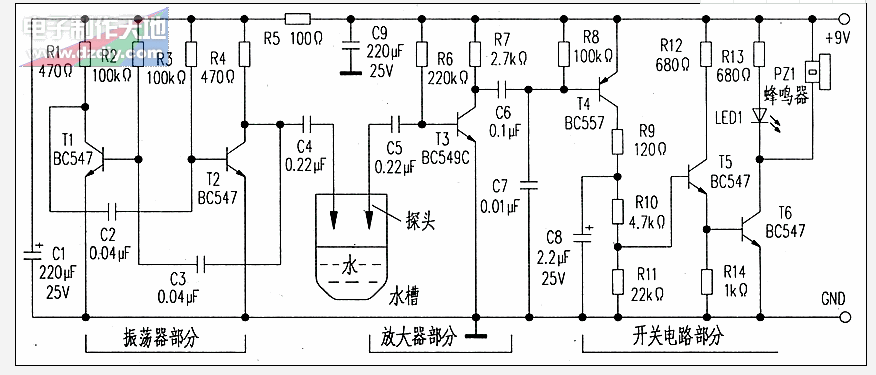

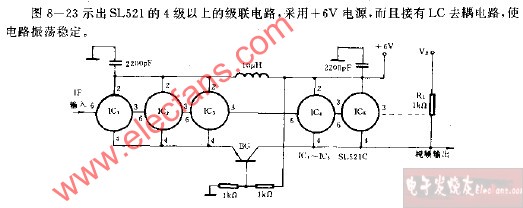

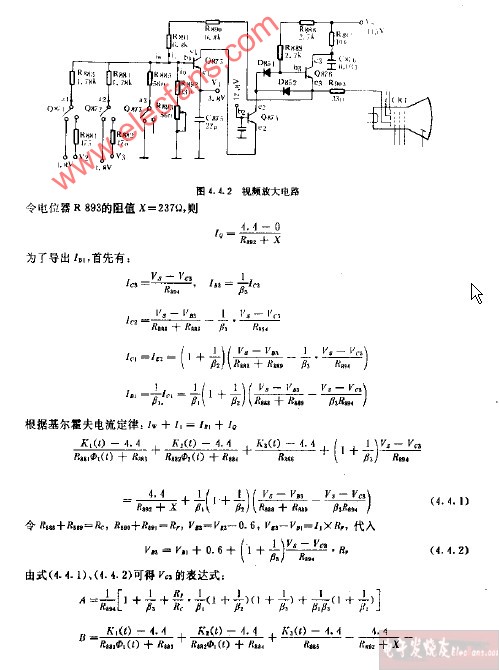

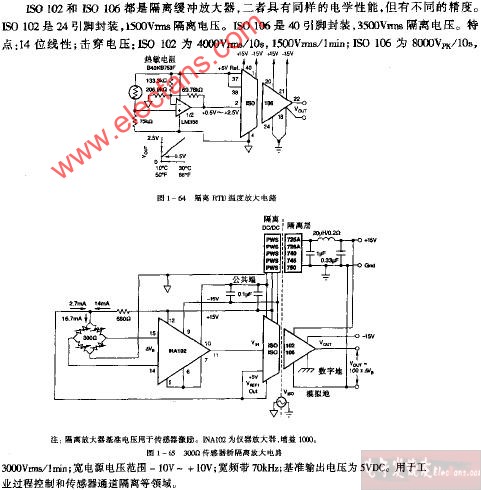

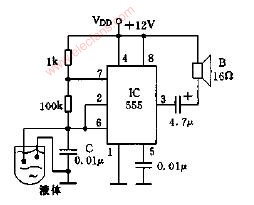

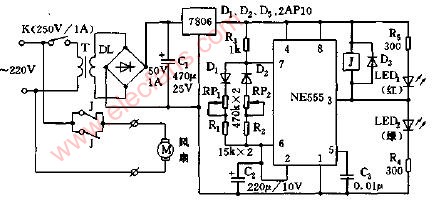

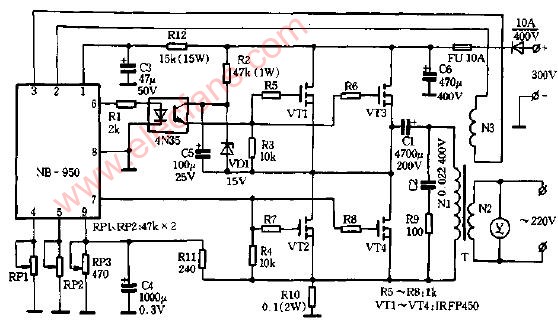

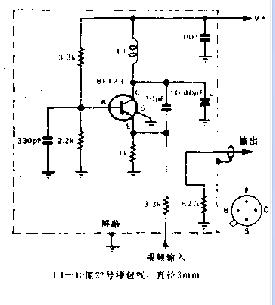

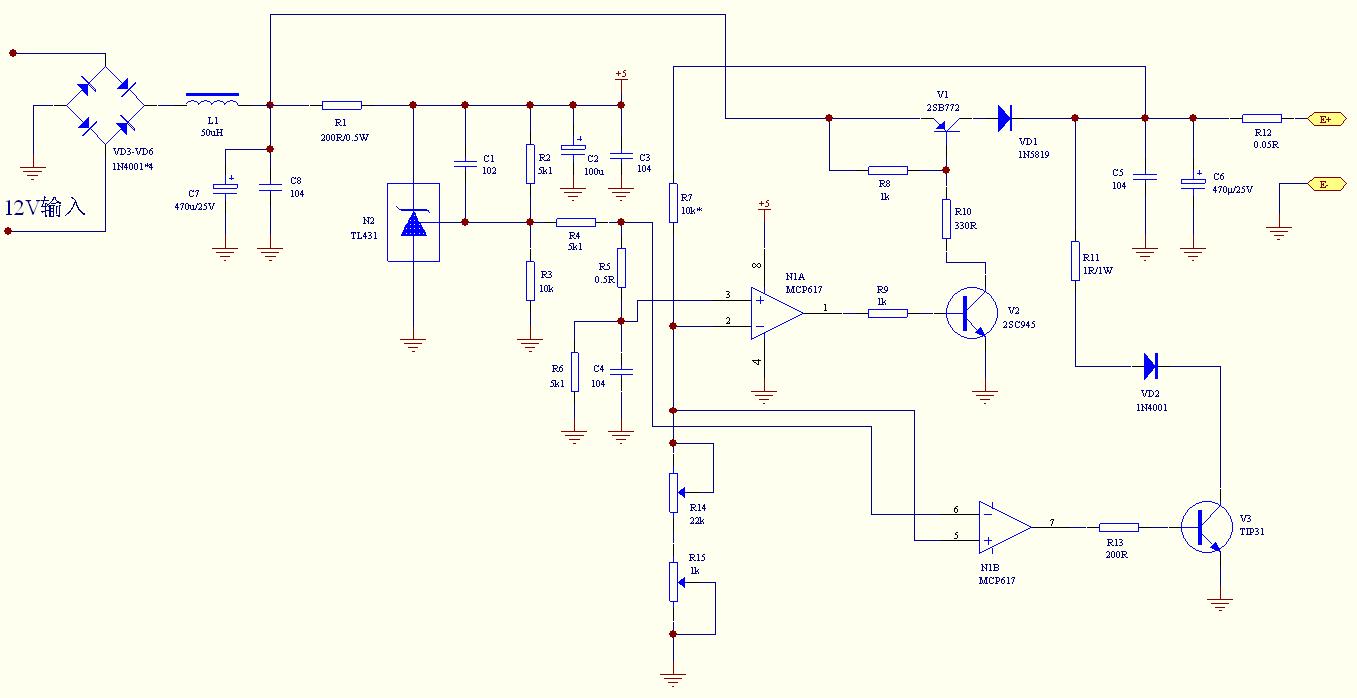

模擬視頻信號經(jīng)過鉗位校正、放大后,將信號送入到A/D轉換器,再經(jīng)FPGA鎖存后將視頻信號發(fā)送給DSP1;經(jīng)視頻同步分離電路,由LM1881分離出模擬視頻的行、場同步信號,用于控制視頻數(shù)據(jù)采集到DSP1,以便進行圖像處理。鉗位校正、視頻同步電路如圖1所示。模擬視頻經(jīng)運放輸入,將中心電平調(diào)到3.3V,加到 A/D輸入端。A/D轉換后的數(shù)據(jù)進入FPGA鎖存。運放均采用ADI公司的AD8047AR,A/D轉換器采用ADI公司的AD9050。AD9050 為10位A/D轉換器,取其高8位進入FPGA。采樣時鐘12MHz,與數(shù)字視頻信號相同。由FPGA對48MHz時鐘四分頻產(chǎn)生。

圖1 模擬視頻輸入轉換電路

攝像機的數(shù)字視頻信號為14對差分信號,經(jīng)FPGA將差分信號轉換為單端信號,并鎖存數(shù)據(jù)。每個象素14位,每幀320×240。

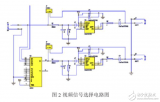

FPGA采用ALTERA公司的CYCLONE系列EP1C3T144C-6,配置芯片采用EPC2LC20。EP1C3T144C-6具有將差分信號轉單端信號的專用I/O口。鎖存在FPGA的數(shù)字,模擬兩路視頻信號根據(jù)工作模式選擇輸出到DSP1數(shù)據(jù)總線上,由DSP1讀入處理,數(shù)據(jù)速率與模擬視頻的采樣速率,數(shù)字視頻的數(shù)據(jù)速率相同。工作模式選擇,開關控制通過PIC9054引入到FPGA。

DSP處理器模塊

DSP處理器陣列模塊主要由4片高速高性能的DSP處理芯片ADSP-TS201S組成多DSP處理器系統(tǒng),ADSP-TS201S性能如下:

基本性能指標如下:

● 600MHz運行速度時,內(nèi)核指令周期1.67ns

● 24M bits片上DRAM,分為6個4M bits塊(128K words X 32 bits)

● 片內(nèi)雙運算模塊,每個都包含一個ALU、一個乘法器、一個移位器和一個寄存器組

● 雙整數(shù)ALU提供數(shù)據(jù)尋址和指針操作功能

● 片內(nèi)提供14通道DMA、外部口、4個鏈路口、SDRAM控制器、可編程標志引腳、2個定時器

● 片上仲裁系統(tǒng)可實現(xiàn)8個TigerSHARC DSP的無縫連接

● 內(nèi)部3條互相獨立的128位總線

● 外部數(shù)據(jù)總線64位,地址總線32位

● 每秒48億次40位寬的MAC運算或每秒12億次80位寬的MAC運算;1024點復數(shù)FFT(基2)時間15.7us

● 外部端口 1G字節(jié)每秒;鏈路口(每個)1G字節(jié)每秒

DSP處理器陣列模塊中DSP1是用來整理所收集到的視頻信號,并進行相應的預處理后,將數(shù)據(jù)分發(fā)送到后面的DSP,進行進一步的處理。

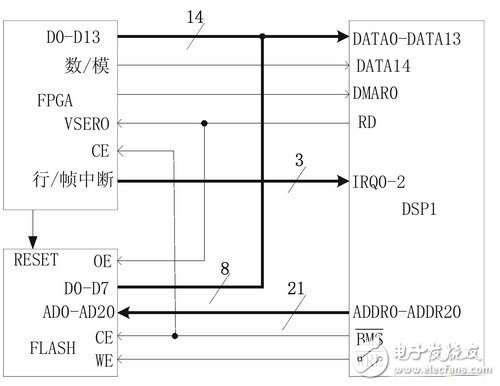

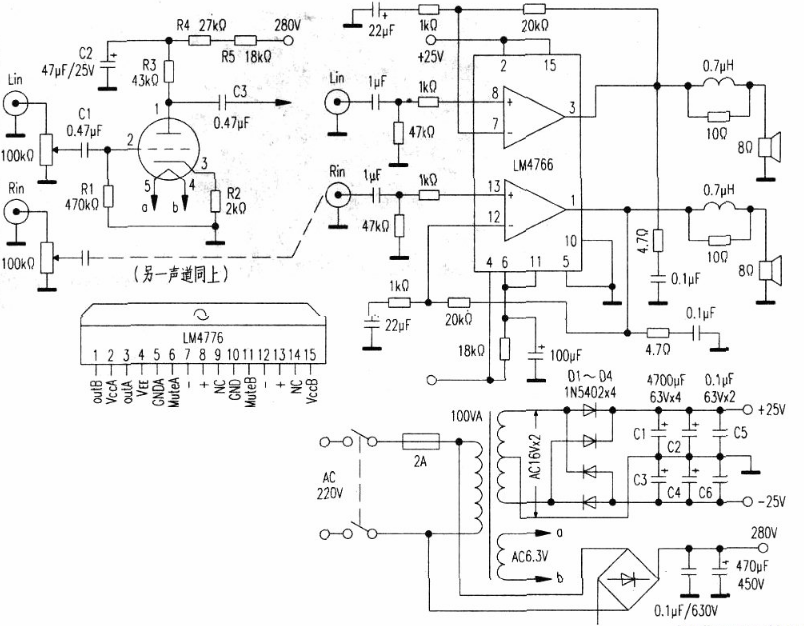

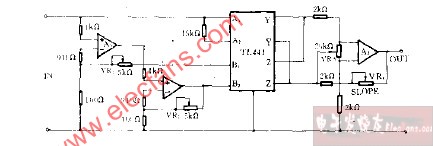

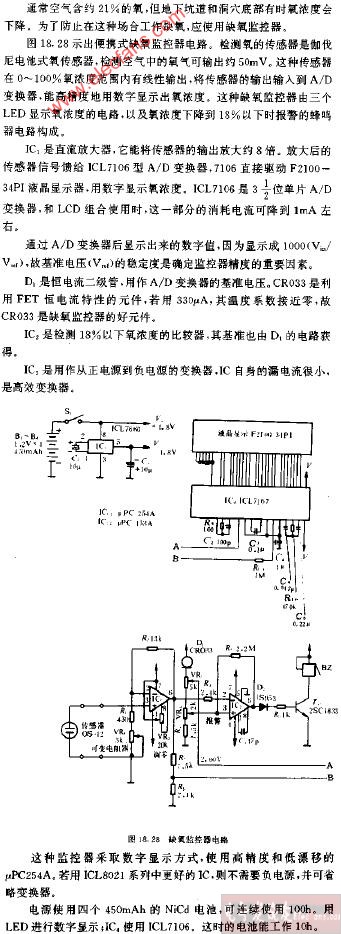

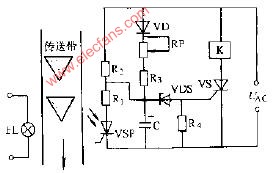

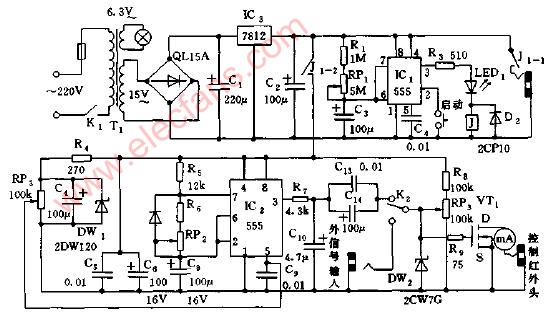

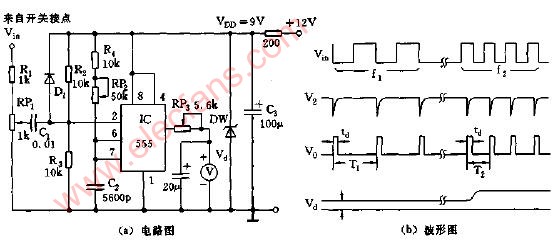

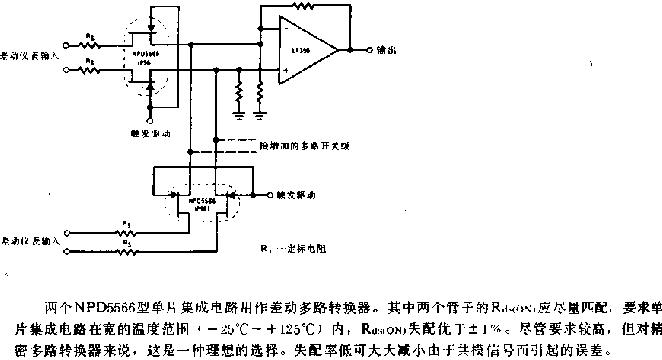

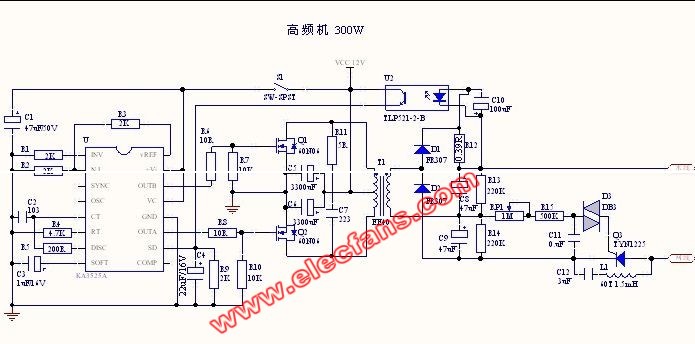

DSP1并行口應接FPGA輸出的視頻數(shù)據(jù),還要接FLASH,完成DSP加載。DSP1的IRQ0,IRQ1分別作視頻輸入的幀中斷和行中斷,接到FPGA。其連接電路如下圖3所示。

圖2DSP1與FPGA,F(xiàn)LASH 連接圖

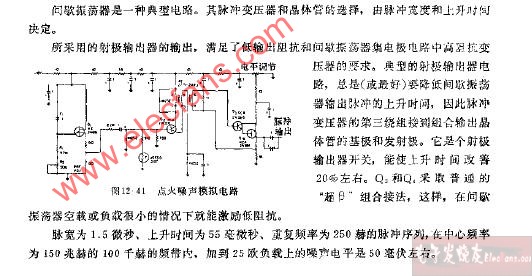

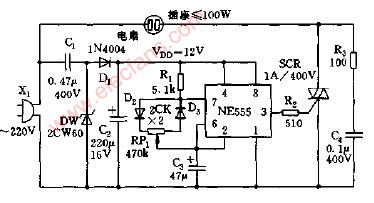

矩陣切換器電路

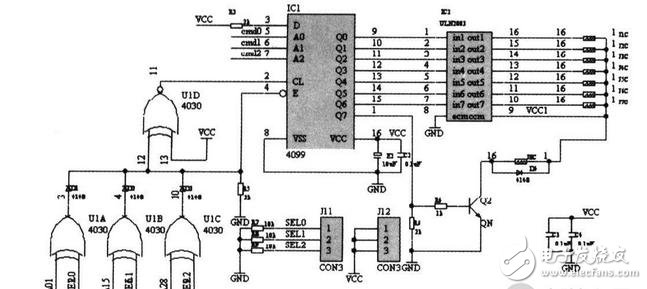

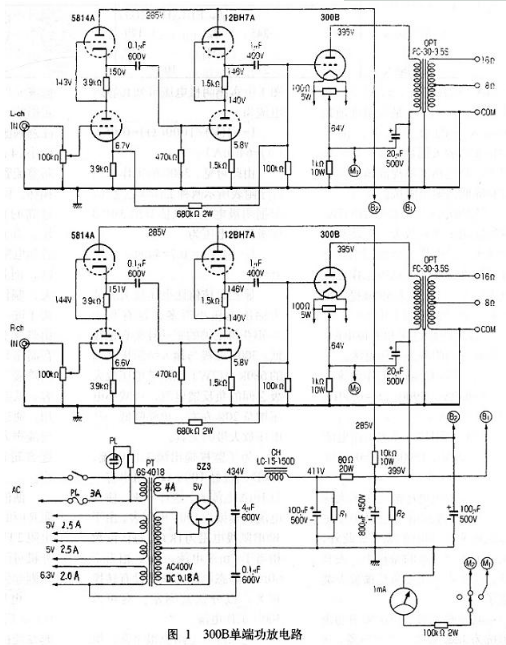

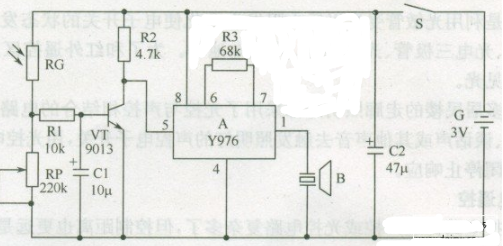

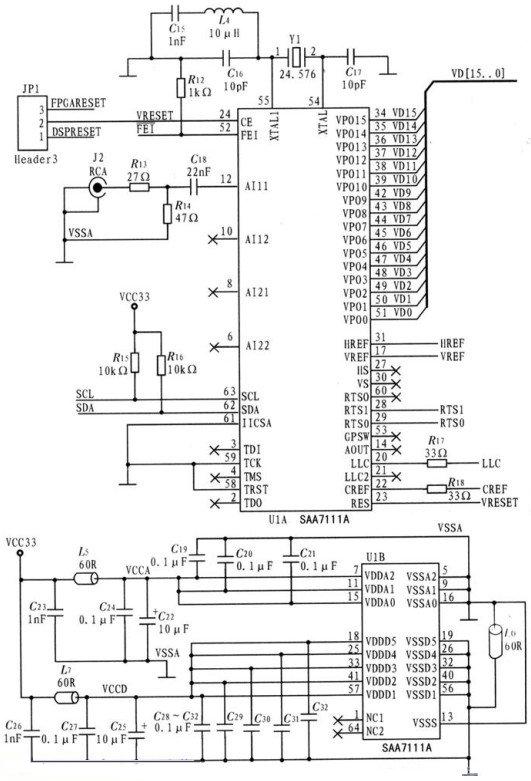

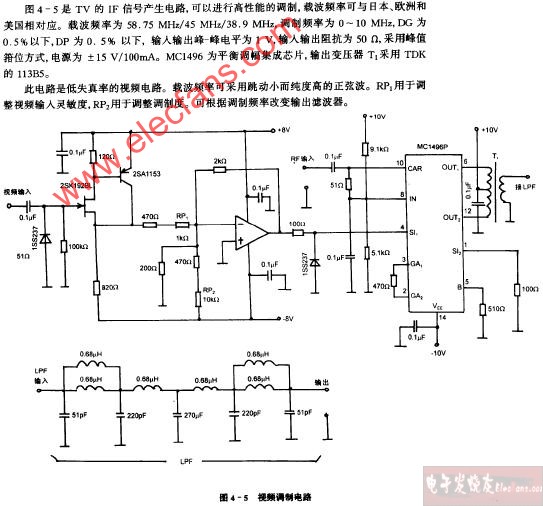

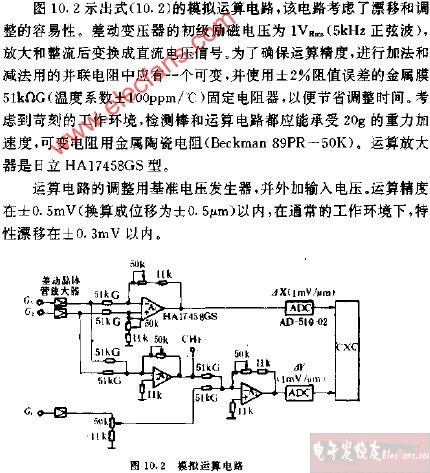

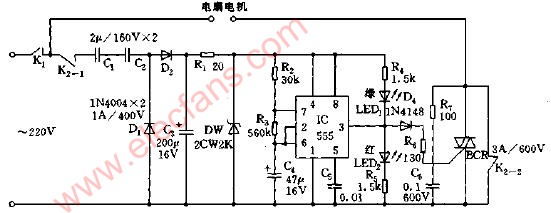

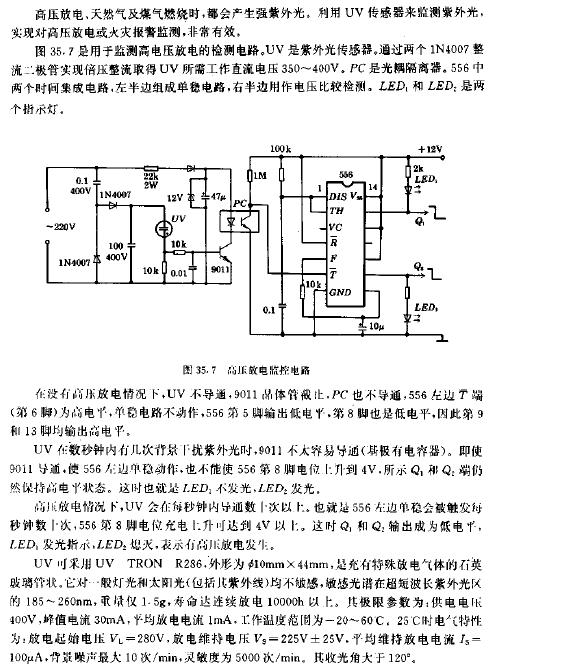

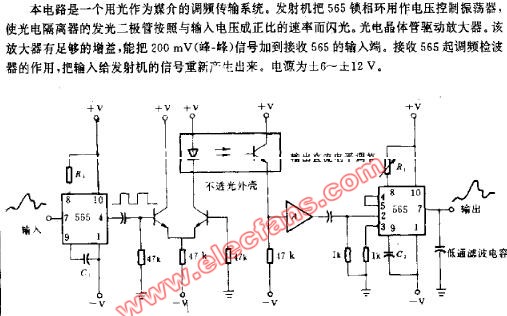

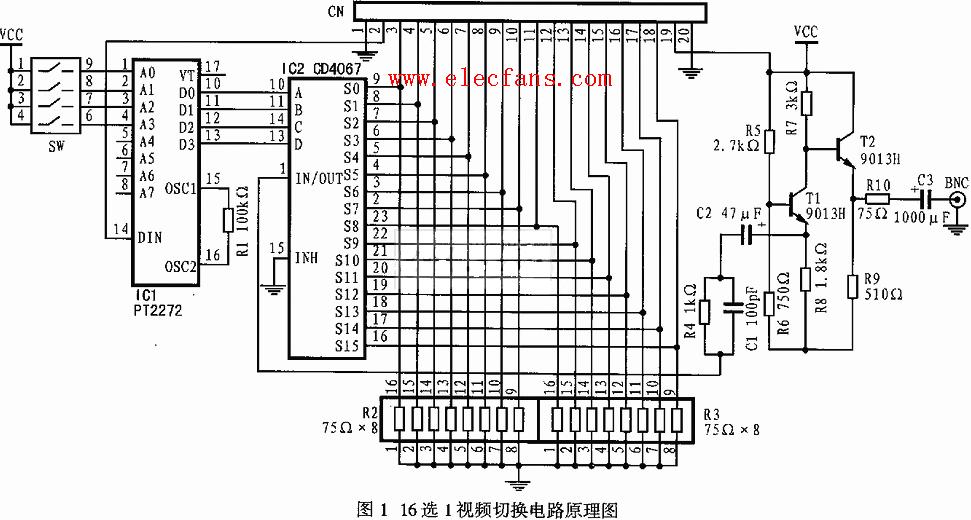

下面介紹的是容量為32路音視頻的監(jiān)控,為簡化設計,及調(diào)試、安裝、升級等的方便,32路音視頻不在一塊PCB板上處理,而是分成4塊子板,每塊子板處N8路音視頻,實現(xiàn)8路音視頻通道的8選1輸出功能,即4塊子板組成一個矩陣切換器,在同一時間實現(xiàn)32選4輸出功能。每塊子板的電路圖如圖3所示。

圖3 矩陣切換器電路

在圖中,J1…J8為繼電器線圈,用雙刀雙擲繼電器J4078實現(xiàn)音視頻的同時切換。J11、J12為跳線插座,該跳線為子板設置地址,當設置的子板地址與主控制器的子板選擇地址(A0、A1、A2)相同時,該子板塊的4099處于工作狀態(tài),這時,再通過主控制器的通道選擇指令(cmd0、 cmd1、cmd2)使J1…J8中任一繼電器完成切換動作,實現(xiàn)某一路音視頻的同時選通。

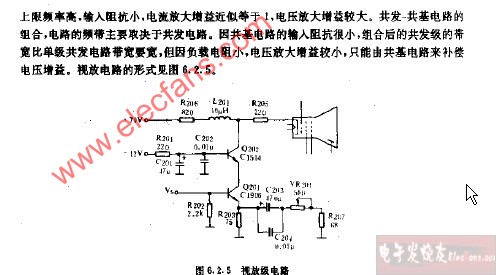

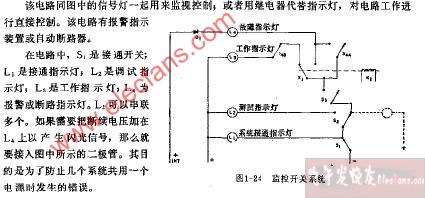

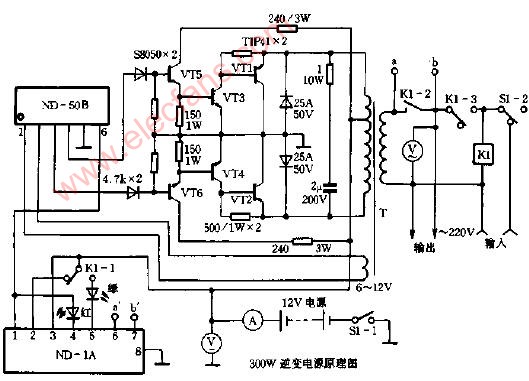

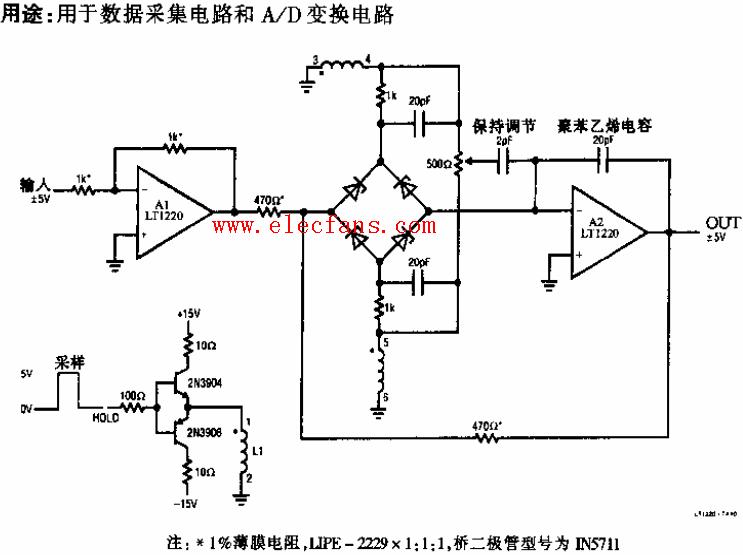

語音信號采集與處理電路

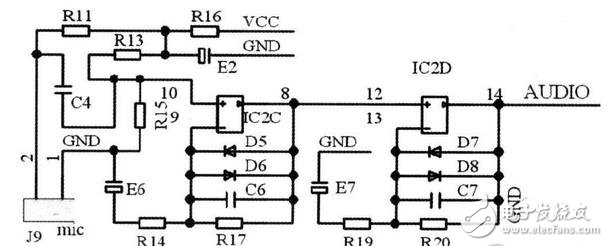

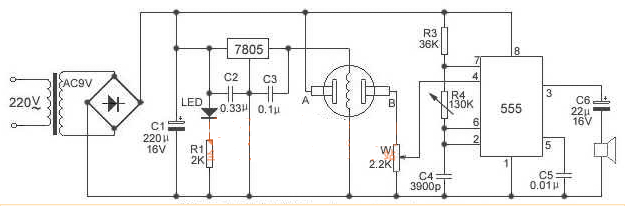

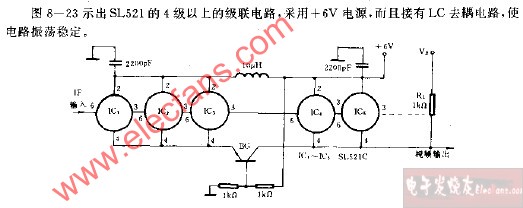

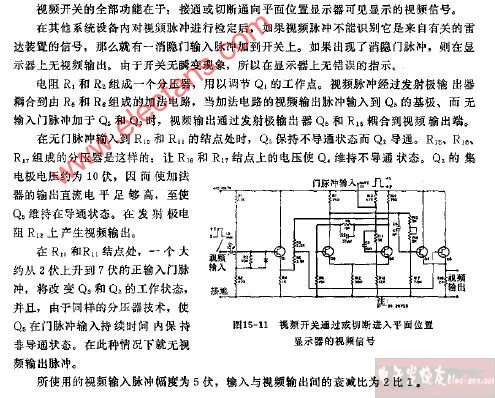

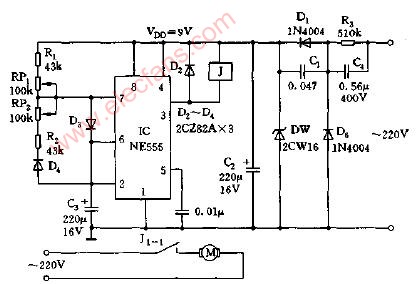

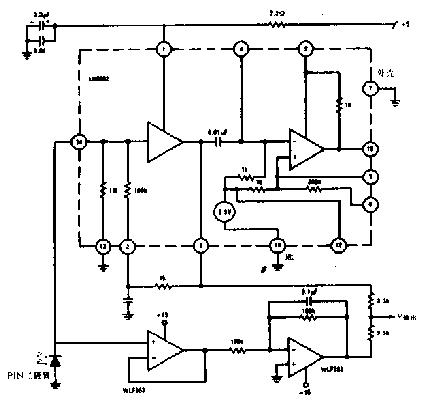

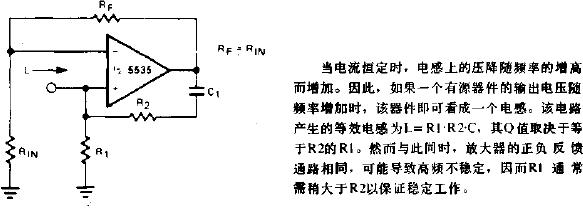

因為要采集教室各個位置(一般在20~50m2范圍內(nèi))的語音信號,使用普通的話筒放大電路顯然達不到要求。本系統(tǒng)采用對數(shù)放大電路進行語音放大,比較清晰地采集到了50m2范圍內(nèi)各個位置的語音信號。設計的對數(shù)放大電路如圖所示。IC2為運算放大器,系統(tǒng)選用LM358實現(xiàn)二級運算放大。

圖4 語音信號采集與處理電路

利用傳感技術和電子技術系統(tǒng)設計思路簡單、成本低廉、方便實用。對提高學生自主學習的自覺性,監(jiān)控自主學習設備和軟件平臺運行情況,防止人為破壞造成的不必要損失,提高設備運行的穩(wěn)定性和可靠性等起到了非常重要的作用。

編輯點評:本文簡單介紹了模擬視頻監(jiān)控采集電路的設計,模擬視頻信號經(jīng)過鉗位校正、放大后,將信號送入到A/D轉換器,再經(jīng)FPGA鎖存后將視頻信號發(fā)送給DSP1。能夠完成圖像的高速處理,實現(xiàn)圖像的實時顯示,目標跟蹤。在實際應用中該系統(tǒng)工作穩(wěn)定,達到預想效果。

電子發(fā)燒友《安防技術特刊》,更多優(yōu)質內(nèi)容,馬上下載閱覽

電子發(fā)燒友App

電子發(fā)燒友App

評論