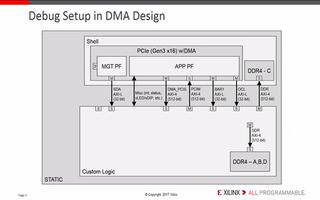

如何使用Vivado硬件管理器連接F1進(jìn)行定制邏輯設(shè)計(jì)

本視頻將向您展示為定制邏輯設(shè)計(jì)添加調(diào)試內(nèi)核的步驟。此外,它還包含一個(gè)演示,展示如何使用Vivado硬....

如何使用Carnegie Robotics 3D傳感器降低計(jì)算量

Carnegie Robotics的產(chǎn)品使無人機(jī)器人能夠感知和理解3D信息,從而使系統(tǒng)在工業(yè)和農(nóng)??....

Xilinx 16nm Kintex UltraScale+器件的性能、功耗和靈活性介紹

該視頻重點(diǎn)介紹了Xilinx 16nm Kintex UltraScale +器件中雙工作電壓的性能....

如何使用神經(jīng)網(wǎng)絡(luò)模型加速圖像數(shù)據(jù)集的分類

通過圖像分類示例,了解Xilinx FPGA如何加速機(jī)器學(xué)習(xí),這是關(guān)鍵的數(shù)據(jù)中心工作負(fù)載。

該演示....

Zynq UltraScale+ RFSoC的功能特點(diǎn)與應(yīng)用

在本演示視頻中,Xilinx討論了其Zynq?UltraScale+?RFSoC系列的產(chǎn)品詳細(xì)信息。

Virtex-7 x690T中PCI Express x8 Gen3端點(diǎn)功能的演示

在Virtex-7 x690T FPGA中首次公開演示集成PCI Express x8 Gen3端點(diǎn)....

如何使用report_cdc命令分析、調(diào)試和修復(fù)CDC問題

了解如何使用命令report_cdc分析,調(diào)試和修復(fù)設(shè)計(jì)中的CDC問題。

命令report_cdc....

如何構(gòu)建用戶空間的DMA功能的軟件系統(tǒng)

此會(huì)話描述了構(gòu)建允許來自用戶空間的DMA功能的軟件系統(tǒng)的過程。

這是使用帶有用戶空間應(yīng)用程序的字符....

如何將2014.x Ultrascale內(nèi)存IP級(jí)I/O遷移到2015.1版本中

了解將2014.x Ultrascale內(nèi)存IP級(jí)I / O約束遷移到2015.1版本所涉及的過程,....

Xilinx軟件命令行工具:XSCT開發(fā)和調(diào)試

了解如何使用XSCT,Xilinx軟件命令行工具進(jìn)行開發(fā)和調(diào)試。

該視頻演示了XSCT如何充當(dāng)Xi....

如何快速把握機(jī)器視覺的市場(chǎng)機(jī)會(huì)

網(wǎng)絡(luò)研討會(huì)將重點(diǎn)介紹Xilinx及其合作伙伴的IP核豐富套件如何通過生態(tài)系統(tǒng)使用戶能夠快速,輕松地把....

Xilinx工業(yè)物聯(lián)網(wǎng)系列研討會(huì):可編程技術(shù)在智能工廠中的應(yīng)用

本次研討會(huì)將向您系統(tǒng)地介紹工業(yè)物聯(lián)網(wǎng)(IIoT),重點(diǎn)關(guān)注可編程技術(shù)在智能工廠中的應(yīng)用,比如可用于實(shí)....

Zynq-7000可擴(kuò)展處理平臺(tái)的特點(diǎn)及應(yīng)用介紹

Xilinx處理平臺(tái)副總裁Vidya Rajagopalan和ARM物理IP部門技術(shù)副總裁Dipes....

如何使用Xilinx SDK創(chuàng)建Linux應(yīng)用程序,并進(jìn)行開發(fā)和調(diào)試

了解如何使用Xilinx SDK創(chuàng)建Linux應(yīng)用程序。

我們還將重點(diǎn)介紹和演示支持Linux應(yīng)用....

Vivado Design Suite搭配版本控制系統(tǒng)進(jìn)行使用

了解將Vivado Design Suite與版本控制系統(tǒng)配合使用的最佳實(shí)踐。

修訂控制系統(tǒng)用于嚴(yán)....

AMS技術(shù)何幫助減少器件數(shù)量,提高整體系統(tǒng)性能

該視頻演示了Xilinx模擬混合信號(hào)(AMS)技術(shù)如何幫助減少器件數(shù)量,提高整體系統(tǒng)性能,并增強(qiáng)Xi....

Vivado Design Suite 2015.3新增量編譯功能介紹

了解Vivado實(shí)現(xiàn)中2015.3中的新增量編譯功能,包括更好地處理物理優(yōu)化和自動(dòng)增量編譯流程。

Vivado Design Suite 2015.3的新功能介紹

了解Vivado實(shí)現(xiàn)中2015.3中的新增量編譯功能,包括更好地處理物理優(yōu)化和自動(dòng)增量編譯流程。

如何使用SDAccel編譯庫(kù)解決功能和語(yǔ)法錯(cuò)誤

SDAccel有一個(gè)集成的調(diào)試環(huán)境(使用gdb),它提供了一個(gè)以斷點(diǎn)和單步功能為中心的軟件調(diào)試視圖。....

UltraFast設(shè)計(jì)的建議方法及電路板和器件規(guī)劃介紹

介紹有關(guān)電路板和器件規(guī)劃的UltraFast設(shè)計(jì)方法建議。

本快速入門介紹了電路板布局建議,IO和....

Vivado Design Suite設(shè)計(jì)套件的UltraFast設(shè)計(jì)方法的介紹

UltraFast設(shè)計(jì)方法對(duì)您在Vivado Design Suite中的成功至關(guān)重要。

介紹Ul....

在Vivado中如何實(shí)現(xiàn)OpenCV設(shè)計(jì)

觀看視頻,了解OpenCV庫(kù)和其在一些典型應(yīng)用中的使用,以及Zynq-7000 SoC的優(yōu)點(diǎn)和如何實(shí)....

使用Vivado 2016.3中IBERT調(diào)試的好處及步驟

了解使用Vivado 2016.3中引入的系統(tǒng)內(nèi)IBERT進(jìn)行調(diào)試的好處,以及將其添加到設(shè)計(jì)中所需的....

采用Virtex-7 FPGA進(jìn)行DSP性能演示

ICHEC討論了FPGA對(duì)HPC應(yīng)用的適用性,并重點(diǎn)介紹了能夠利用特定FPGA上所有DSP的器件的最....