作為集成電路設(shè)計(jì)領(lǐng)域現(xiàn)場(chǎng)可編程門陣列 (FPGA) 技術(shù)的創(chuàng)造者之一,賽靈思一直積極推廣高層次綜合 (HLS) 技術(shù),通過這種能夠解讀所需行為的自動(dòng)化設(shè)計(jì)流程打造出可實(shí)現(xiàn)此類行為的硬件。賽靈思剛剛推出了一本專著,清晰介紹了如何使用 HLS 技術(shù)來創(chuàng)建優(yōu)化的硬件設(shè)計(jì)。

這本名為《FPGA 并行編程》的專著出自賽靈思首席工程師 Stephen Neuendorffer 以及來自 UCSD 的 Ryan Kastner 和來自 Cognex 的 Janarbek Matai。該書對(duì)于任何有興趣構(gòu)建 FPGA 系統(tǒng)的人來說都實(shí)屬具有實(shí)用意義的指南。對(duì)于高年級(jí)本科生和研究生的課程而言,本書也具有特殊價(jià)值。此外,這本書對(duì)于在職系統(tǒng)設(shè)計(jì)人員及嵌入式編程人員同樣非常實(shí)用。

該書讀者只要求具備 C/C++ 編程工作知識(shí),也就相當(dāng)于汽車駕駛員掌握自動(dòng)檔駕駛水平,而且讀者應(yīng)當(dāng)熟悉其他基本的計(jì)算機(jī)架構(gòu)概念。此外,該書還包含了大量實(shí)例代碼。我們強(qiáng)烈建議該書讀者打開Vivado HLS 并親自嘗試這些實(shí)例代碼。我們通過 Vivado WebPack Edition 提供免費(fèi)的 License,或者 Vivado System Edition 的 30 天免費(fèi)試用期。

此外,該書還提供一些類似教科書的功能,對(duì)于課堂教學(xué)尤其具有價(jià)值。例如,書中每章都會(huì)提出問題,向讀者提出挑戰(zhàn),有助于讀者在閱讀時(shí)鞏固對(duì)材料的理解。書中還提供了由加州大學(xué)圣迭戈分校 (UCSD) 開發(fā)并用于 HLS 課堂教學(xué)的有關(guān)項(xiàng)目。如欲獲得有關(guān)項(xiàng)目文件,講師可向 UCSD 提出申請(qǐng)。各項(xiàng)目在不同程度上都與書中某個(gè)章節(jié)有關(guān),包括針對(duì) FPGA 板的參考設(shè)計(jì),您可以隨時(shí)聯(lián)系賽靈思大學(xué)計(jì)劃(XUP)獲取。

正如您所預(yù)料的那樣,隨著所讀內(nèi)容的深入,每個(gè)項(xiàng)目的復(fù)雜性也會(huì)提升,因此本書應(yīng)該循序漸進(jìn)地閱讀。采用這樣的閱讀方法,讀者就能了解到例如 HLS 方法的優(yōu)化如何能直接應(yīng)用于特定應(yīng)用。每款應(yīng)用也將進(jìn)一步介紹如何編寫 HLS 代碼。不過,通過舉例法來教學(xué)也有其不足之處。首先,大多數(shù)應(yīng)用都需要一些額外的背景知識(shí),以便讀者更好地理解正在執(zhí)行的計(jì)算。要真正理解相關(guān)計(jì)算,通常需要對(duì)應(yīng)用的數(shù)學(xué)背景進(jìn)行廣泛的討論。這對(duì)只希望了解 HLS 基礎(chǔ)知識(shí)的讀者來說可能缺乏吸引力,不過 Neuendorffer 堅(jiān)信要想掌握實(shí)現(xiàn)最佳設(shè)計(jì)所必需的代碼重構(gòu)技巧,就必須有這樣深入的了解。

雖然《FPGA 并行編程》的章節(jié)安排是按照閱讀順序設(shè)計(jì)的,并且隨著讀者閱讀的深入,章節(jié)的復(fù)雜性也會(huì)提升,但是針對(duì)更高級(jí)的 HLS 用戶,如果只希望了解特定應(yīng)用領(lǐng)域,那么也可以直接閱讀個(gè)別章節(jié)。例如,對(duì)生成硬件加速分類引擎感興趣的讀者可跳至第十章,而無(wú)需閱讀此前的所有章節(jié)。

賽靈思強(qiáng)烈建議將 HLS 作為一種開發(fā) FPGA 集成電路的高效設(shè)計(jì)流程,從而構(gòu)建可在汽車、飛機(jī)、衛(wèi)星和其他新興技術(shù)領(lǐng)域中智能且高效工作的硬件。《FPGA 并行編程》將成為推進(jìn)此類產(chǎn)品開發(fā)的重要而高效的指南。歡迎將本書收入實(shí)驗(yàn)室的藏書之列以備不時(shí)之需。

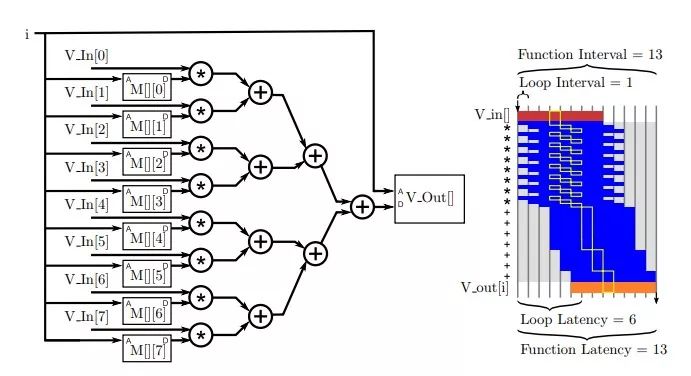

矩陣—矢量乘法架構(gòu),配合具體陣列分區(qū)和流水線。

已省略流水線寄存器,并將行為顯示在右側(cè)。

-

賽靈思

+關(guān)注

關(guān)注

33文章

1797瀏覽量

132343 -

硬件設(shè)計(jì)

+關(guān)注

關(guān)注

18文章

433瀏覽量

45198 -

C語(yǔ)言編程

+關(guān)注

關(guān)注

6文章

90瀏覽量

21620

發(fā)布評(píng)論請(qǐng)先 登錄

如何在Unified IDE中創(chuàng)建視覺庫(kù)HLS組件

使用AMD Vitis Unified IDE創(chuàng)建HLS組件

如何使用AMD Vitis HLS創(chuàng)建HLS IP

授時(shí)系統(tǒng)廠家,授時(shí)系統(tǒng)哪家好?賽思高精度授時(shí)系統(tǒng)助力華福證券授時(shí)服務(wù)新升級(jí)!

求書一本,希望充當(dāng)教材

NucleiStudio_IDE下調(diào)試一直報(bào)all ones錯(cuò)誤怎么解決?

【「極速探索HarmonyOS NEXT 」閱讀體驗(yàn)】 初印象:一本純血鴻蒙應(yīng)用開發(fā)入門的好書

名單公布!【書籍評(píng)測(cè)活動(dòng)NO.57】芯片通識(shí)課:一本書讀懂芯片技術(shù)

賽靈思低溫失效的原因,有沒有別的方法或者一些見解?

易靈思FPGA產(chǎn)品的主要特點(diǎn)

【「從算法到電路—數(shù)字芯片算法的電路實(shí)現(xiàn)」閱讀體驗(yàn)】+一本介紹基礎(chǔ)硬件算法模塊實(shí)現(xiàn)的好書

帶來全新辦公體驗(yàn)!思必馳發(fā)布AI辦公本Turbo

思必馳AI辦公本Turbo重磅發(fā)布

優(yōu)化 FPGA HLS 設(shè)計(jì)

思爾芯賽題正式發(fā)布,邀你共戰(zhàn)EDA精英挑戰(zhàn)賽!

賽靈思推出一本專著,介紹如何使用HLS技術(shù)來創(chuàng)建優(yōu)化的硬件設(shè)計(jì)

賽靈思推出一本專著,介紹如何使用HLS技術(shù)來創(chuàng)建優(yōu)化的硬件設(shè)計(jì)

評(píng)論