PCI Express (PCIe)即將于2021年迎來6.0規(guī)范,意味著其數據傳輸速率將高達64GT每秒并采用PAM-4調制。有消息指出,銅互連線路雖然覆蓋范圍較小,但使用壽命更長。

PCI特別興趣小組(SIG)正在為主流設計廠商提供PAM-4功能。目前,SerDes開發(fā)人員已經開始在56G以及更高速率的高端系統(tǒng)之上使用這項功能。著眼于最前沿,另一些組織已經開始研究112G規(guī)范,部分專家甚至表示200G銅鏈路也已經擁有了清晰的發(fā)展思路。

但困擾研究人員的永恒難題在于,鏈路速度越快,其傳播距離也就越短。有說法稱,通過采用更為昂貴的電路板印刷材料或者重新定時芯片能夠有效緩解這類難題。而另一大考量因素,則是在采用PAM-4的同時需要配合正向糾錯(FEC)塊,但后者會提升延遲水平。

為了實現(xiàn)升級,系統(tǒng)設計師已經將目光轉向服務器與網絡設備內部的有線鏈路,希望避免因引入重新定時芯片或者優(yōu)質電路板材料而帶來的成本增長。SIG目前仍在爭論其6.0規(guī)范的延遲設定,一位專家表示其至少需要與延遲僅為數十納秒的DRAM相匹配。

PAM-4與FEC都是PCIe規(guī)范中的新產物,而在此前的規(guī)范當中,一直依賴于更為寬松的非歸零(NRZ)技術。

SIG主席Al Yanes表示,“這項工作頗具挑戰(zhàn)性。我們將從各個角度進行探索——包括材料、連接器等等,但這些都有其對應成本……問題的核心在于PHY以及模擬與誤碼率,但我們很幸運,因為我們的組織當中有著眾多睿智的工程師人才。”

作為6.0規(guī)范,Gen6方案將需要向下兼容全部早期PCIe規(guī)范,以確保主板與網卡能夠在不同的時間段內逐步完成演進。但Yanes也指出,提供一項幫助產品在NRZ與PAM-4方案之間轉換的規(guī)范本身,同樣會帶來“成本負擔”。

大型云計算服務供應商正是此次提速工作當中的重要驅動因素之一。SIG在上個月完成了32 GT每秒 Gen5規(guī)范,并已經開始為AI加速器、、數據中心處理器以及存儲系統(tǒng)提供芯片產品。此外,在大型數據中心內掀起的由400 G到800 G的網絡升級行動,也推動了市場對于快速互連方案的需求。

Yanes指出,“在我們與電氣工作組就Gen6進行面對面討論之前,我們先休息了一個月,因為現(xiàn)在的這一切都與PHY有關。”所謂PHY,也就是高度模擬化的物理層模塊。

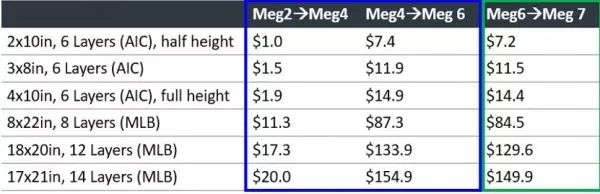

升級PC板材料的成本很高,Meg7可能要到明年或者更晚才能獲得認證。

雖然PCIe與其它銅纜互連方案正在保持著高速發(fā)展,但未來的道路正變得愈發(fā)艱難。為了能夠實現(xiàn)與前幾代升級相同的提升效果,工程師們必須采用更好的電路板材料或者引入重新定時芯片——這兩種方案通常都成本不菲。

在PCIe 1.0的時代,在主流FR4板上可發(fā)送的信號距離高達20英寸,甚至能夠直接穿越兩個連接器。而基于現(xiàn)有16 GT每秒PCIe 4.0規(guī)范的高端產品信號,可能在抵達一個連接器之前就已經消失。

從Gen4規(guī)范開始,由于設計多樣化程度越來越高,SIG決定停止報告規(guī)范中所支持的信號傳輸距離。相反,新的規(guī)范以眼狀圖的形式為良好信號定義出高度與寬度。此外,新規(guī)范還提供關于信號丟失問題的粗略指導——Gen4為28 dB、Gen5為36 dB。預計Gen6還將具有類似的損耗,但具體定義尚未公布。

談到對Gen6的預期,來自Keysight公司的一位SIG董事會成員表示,“我們還不清楚特定設計的串擾、連接器反映以及所使用的具體材料——目前還有太多未知因素。”

為了削減成本,各OEM廠商正越來越多地傾向利用短電纜對安裝在系統(tǒng)之內多塊小板上的組件進行連接。

HPE公司研究員Michael Krause在與合作伙伴們分享系統(tǒng)設計思路時表示,“舉例來說,相較于設計一塊與機箱等長的主板,我們完全可以在系統(tǒng)當中隔離出一個個很小的機械裝置,其中只能容納插槽與DIMM,并利用線纜跨越任意距離將其連接起來。目前已經有很多平臺供應商都正在或者即將轉向這種模塊化設計方式。”

模塊化服務器能夠利用有線鏈路實現(xiàn)成本削減。

Kraus認為,OEM廠商需要對目前的幾種小型電路板及連接器進行標準化,從而在提高產量的同時降低新方案的制造成本。他補充稱,一部分標準化組織已經在對其外形進行定義。

Yanes指出,“我們在外部PCIe布線方面沒能取得多少進展,但我聽說有一些成員已經開始使用內部布線方案——其實二十年之前,人們普遍認為布線是一種差勁的解決方式。”

在年度SIG大會上,不少IP與測試供應商都展示了自己的Gen4與Gen5設計演示方案。Synopsys公司的工程師表示,該公司擁有160份Gen4 IP許可,匱包括來自初創(chuàng)企業(yè)Habana的AI加速器。

在年度SIG大會上,Marvell公司的一支IP小組展示了x4 Gen5測試模塊的工作演示,未來其有可能成為固態(tài)硬盤控制器的一部分。英特爾方面也表示,其將在2021年支持Gen5處理器。

Synopsys公司的一位工程師指出,目前已經有多家客戶在實際芯片與產品當中使用Gen5 IP,而且主要集中在16納米及以下的高端產品當中。PLDA描述了其面向兩臺橋接交換機銷售的Gen5 IP,且計劃在今年4月之前投入實際使用。

-

芯片

+關注

關注

459文章

52145瀏覽量

435930 -

pcb

+關注

關注

4351文章

23405瀏覽量

406616 -

數據傳輸

+關注

關注

9文章

2002瀏覽量

65658 -

PCIe

+關注

關注

16文章

1322瀏覽量

84656

原文標題:PCIe正在為64G躍升進行籌備

文章出處:【微信號:cunchujie,微信公眾號:存儲界】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

PCIe插槽秒變M.2存儲倉!免拆機維護神器M.2 NVMe轉PCIe 4.0 x4 硬盤抽取盒!#pcie

Teledyne LeCroy發(fā)布Summit M64 PCIe協(xié)議分析儀

Teledyne LeCroy推出Summit M64 PCIe協(xié)議分析儀/訓練器

TeledyneLeCroy推出新PCIe協(xié)議分析儀Summit M64

慧榮正在開發(fā)4nm PCIe 6.0 SSD主控芯片

Vivo籌備新子品牌Jovi,疑似新機現(xiàn)身Geekbench

如何選擇適合的PCIe配置

pcie 4.0與pcie 5.0的區(qū)別

pcie接口類型及其應用

PCIe的最新發(fā)展趨勢

如何測試PCIe插槽的速度

PCIe 4.0與PCIe 3.0的性能對比

高級顧問宣布離職!OpenAI解散“AGI籌備”團隊

全球首發(fā)!openKylin RISC-V 64G鏡像上線,支持中科通量AI PC

PCIe正在為64G躍升進行籌備 已經擁有清晰的發(fā)展思路

PCIe正在為64G躍升進行籌備 已經擁有清晰的發(fā)展思路

評論