卷積神經(jīng)網(wǎng)絡(luò)仿造生物的視知覺(jué)(visual perception)機(jī)制構(gòu)建,可以進(jìn)行監(jiān)督學(xué)習(xí)和非監(jiān)督學(xué)習(xí),其隱含層內(nèi)的卷積核參數(shù)共享和層間連接的稀疏性使得卷積神經(jīng)網(wǎng)絡(luò)能夠以較小的計(jì)算量對(duì)格點(diǎn)化(grid-like topology)特征,例如像素和音頻進(jìn)行學(xué)習(xí)、有穩(wěn)定的效果且對(duì)數(shù)據(jù)沒(méi)有額外的特征工程(feature engineering)要求。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613910 -

音頻

+關(guān)注

關(guān)注

29文章

3019瀏覽量

83010 -

神經(jīng)網(wǎng)絡(luò)

+關(guān)注

關(guān)注

42文章

4806瀏覽量

102728

發(fā)布評(píng)論請(qǐng)先 登錄

基于賽靈思FPGA的卷積神經(jīng)網(wǎng)絡(luò)實(shí)現(xiàn)設(shè)計(jì)

卷積神經(jīng)網(wǎng)絡(luò)—深度卷積網(wǎng)絡(luò):實(shí)例探究及學(xué)習(xí)總結(jié)

解析深度學(xué)習(xí):卷積神經(jīng)網(wǎng)絡(luò)原理與視覺(jué)實(shí)踐

什么是深度學(xué)習(xí)?使用FPGA進(jìn)行深度學(xué)習(xí)的好處?

基于FPGA的深度卷積神經(jīng)網(wǎng)絡(luò)服務(wù)優(yōu)化和編譯測(cè)試

如何通過(guò)FPGA實(shí)現(xiàn)深度卷積網(wǎng)絡(luò)(3)

如何采用FPGA技術(shù)實(shí)現(xiàn)深度卷積網(wǎng)絡(luò)(2)

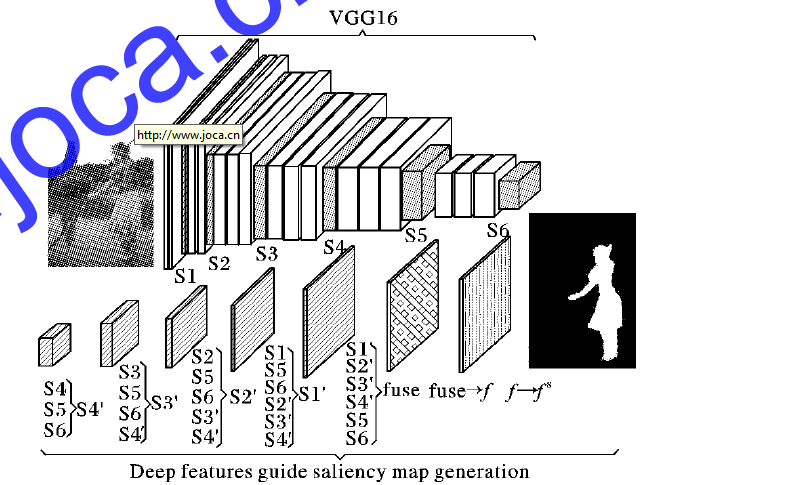

使用深度卷積神經(jīng)網(wǎng)絡(luò)實(shí)現(xiàn)深度導(dǎo)向顯著性檢測(cè)算法

如何用OpenCL實(shí)現(xiàn)FPGA上的大型卷積網(wǎng)絡(luò)加速?

如何用FPGA技術(shù)實(shí)現(xiàn)深度卷積網(wǎng)絡(luò)(7)

如何用FPGA技術(shù)實(shí)現(xiàn)深度卷積網(wǎng)絡(luò)(7)

評(píng)論