靈活的多通道數(shù)字化儀,帶有開放式FPGA,用于實(shí)時(shí)數(shù)字信號(hào)處理

Teledyne SP Devices推出ADQ12DC -- 一款具有開放式FPGA架構(gòu)、功能更豐富靈活的數(shù)據(jù)采集卡,是原始設(shè)備制造商(OEM)產(chǎn)品集成的理想選擇。

ADQ12DC采用雙通道或四通道配置,可實(shí)現(xiàn)性能優(yōu)異且經(jīng)濟(jì)高效的系統(tǒng)設(shè)計(jì)。同時(shí),緊湊的模塊化形態(tài)和高精度同步功能可實(shí)現(xiàn)多通道、高密度采集方案,使ADQ12DC成為多通道系統(tǒng)的完美選擇。

ADQ12DC的通用模擬前端(AFE)支持各種探測(cè)器,因此可用于多種應(yīng)用,如雷達(dá)、激光雷達(dá)、掃頻式斷層掃描儀等等。ADQ12DC具有12位分辨率和每通道1 GS/s的采樣率,無(wú)需申請(qǐng)出口許可,保證產(chǎn)品可用性,交付周期更短。

其產(chǎn)品優(yōu)勢(shì)包括:

直流耦合AFE,具有可編程直流偏置電壓和700 MHz模擬輸入帶寬;

功能強(qiáng)大的開放式Xilinx Kintex 7 K325T FPGA,部分資源可用于定制實(shí)時(shí)的算法應(yīng)用;

2 GB的板載內(nèi)存,高達(dá)3.2 GB/s的數(shù)據(jù)傳輸速率,將數(shù)據(jù)快速傳輸?shù)街鳈C(jī);

硬件觸發(fā)功能及高度精確的多通道同步功能;

用于脈沖峰值檢測(cè)和波形累加平均的獨(dú)立固件選項(xiàng);

采用經(jīng)濟(jì)高效的緊湊型單插槽PCIe x8 Gen 2總線。

Teledyne SP Devices的數(shù)字化儀產(chǎn)品經(jīng)理Jan-Erik Eklund評(píng)論說(shuō):“先進(jìn)的AFE,可定制的實(shí)時(shí)信號(hào)處理算法和高數(shù)據(jù)傳輸速率的結(jié)合,使得該產(chǎn)品非常適合用于當(dāng)今市場(chǎng)上最具挑戰(zhàn)性的應(yīng)用領(lǐng)域。”

-

數(shù)據(jù)采集

+關(guān)注

關(guān)注

40文章

7138瀏覽量

116359 -

數(shù)字化儀

+關(guān)注

關(guān)注

0文章

153瀏覽量

18219

發(fā)布評(píng)論請(qǐng)先 登錄

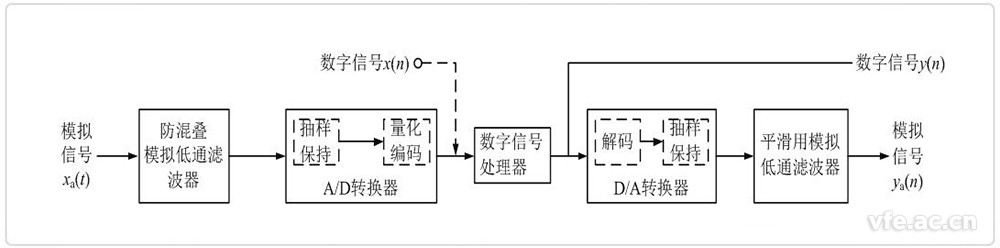

數(shù)字信號(hào)處理的基本組成及其特點(diǎn)?

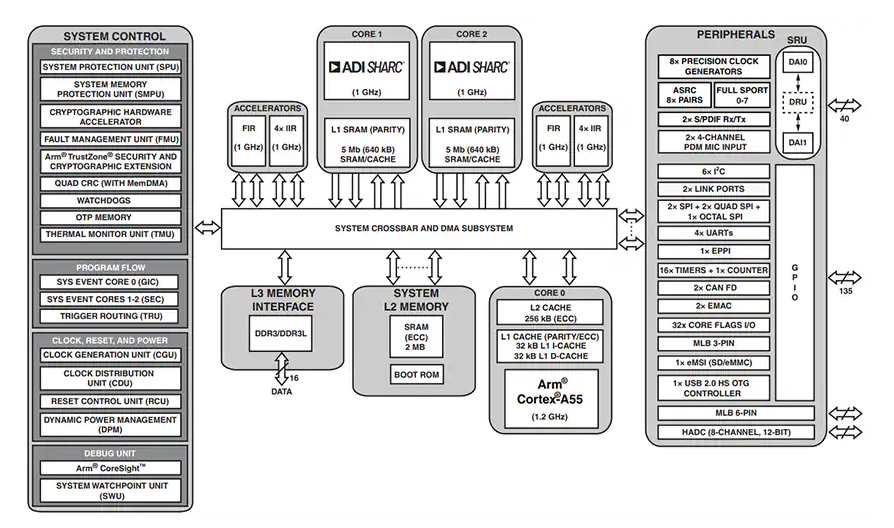

Analog Devices Inc. ADSP-SC598雙SHARC+?數(shù)字信號(hào)處理器數(shù)據(jù)手冊(cè)

HXS320F28027數(shù)字信號(hào)處理器(32位RISC-V DSP)

進(jìn)群免費(fèi)領(lǐng)FPGA學(xué)習(xí)資料!數(shù)字信號(hào)處理、傅里葉變換與FPGA開發(fā)等

想用MATLAB實(shí)時(shí)讀取采集到的數(shù)字信號(hào),怎么操作?

將低成本、高性能的ADSP-21065L數(shù)字信號(hào)處理器用于數(shù)字音頻應(yīng)用

adc與數(shù)字信號(hào)處理的關(guān)系

實(shí)時(shí)數(shù)據(jù)與數(shù)字孿生的關(guān)系

數(shù)字信號(hào)和模擬信號(hào)的特點(diǎn)及應(yīng)用

數(shù)字信號(hào)是離散的還是連續(xù)的

數(shù)字信號(hào)是什么信號(hào)的組合

數(shù)字信號(hào)包括哪些 數(shù)字信號(hào)的特點(diǎn)是什么

數(shù)字信號(hào)處理與通信原理之間的關(guān)系

SMJ320C6701-SP數(shù)字信號(hào)處理器數(shù)據(jù)表

SMV320C6727B-SP浮點(diǎn)數(shù)字信號(hào)處理器數(shù)據(jù)表

Teledyne SP Devices推出ADQ12DC 用于實(shí)時(shí)數(shù)字信號(hào)處理

Teledyne SP Devices推出ADQ12DC 用于實(shí)時(shí)數(shù)字信號(hào)處理

評(píng)論