聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

芯片

+關(guān)注

關(guān)注

459文章

52089瀏覽量

435244 -

ADI

+關(guān)注

關(guān)注

148文章

46016瀏覽量

257946 -

安全

+關(guān)注

關(guān)注

1文章

344瀏覽量

36072

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

AD7124邏輯供電能否大于AVDD?

HI,最近想用AD7124做設(shè)計(jì),想采集真雙極性的電源,選了分離電源±1.8V供電。因?yàn)橥ㄐ诺闹骺?b class='flag-5'>芯片邏輯電平是3.3V,所以IOVDD用了3.3V供電。我看規(guī)格書種有寫,IOVDD不超過3.6V

發(fā)表于 04-15 06:20

模數(shù)轉(zhuǎn)換器 SIG7124 國產(chǎn)平替 AD7124-4,替代 AD7124-4

共創(chuàng)國產(chǎn)高精度模數(shù)轉(zhuǎn)換器芯片平替新生態(tài)

而且因?yàn)?fully compatible,板子拿來,換個(gè)芯片,性能更好 MCU 不用改 c code。

SIG7124

1.17SPS

發(fā)表于 04-10 16:23

求助,關(guān)于NXP S32K3xx硬件板的SIL測(cè)試問題求解

我們?cè)趪L試使用 恩智浦 S32K3xx 硬件板為我們的模型創(chuàng)建 SIL 測(cè)試框架時(shí)遇到問題。錯(cuò)誤消息“錯(cuò)誤:模型配置為創(chuàng)建 SIL 模塊,所選硬件板不支持該模塊。要解決此問題,請(qǐng)?jiān)凇芭?/div>

發(fā)表于 04-01 08:15

NAGIOS XI的硬件要求

? 概覽 準(zhǔn)備好最大化您的網(wǎng)絡(luò)正常運(yùn)行時(shí)間和性能了嗎?NagiosXI是您的解決方案。但在深入研究之前,讓我們確保您擁有合適的硬件來支持您的特定監(jiān)控需求。 要求 下表根據(jù)節(jié)點(diǎn)(主機(jī))與服務(wù)比率 1

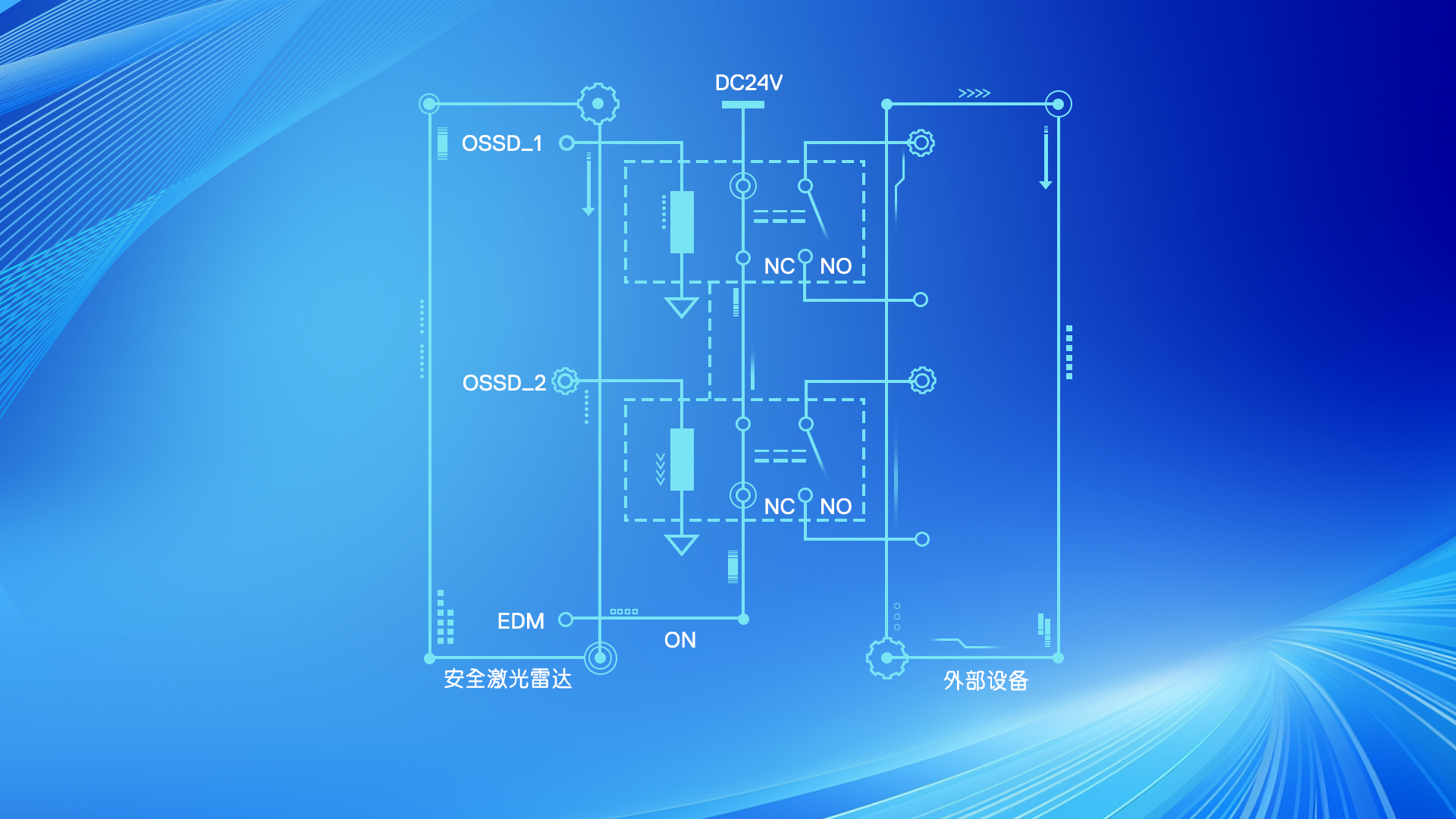

產(chǎn)品介紹 滿足功能安全認(rèn)證要求:SIL 2安全防護(hù)型激光雷達(dá)GS1-5

的SIL 2、PL d、Type 3 權(quán)威認(rèn)證,?表明產(chǎn)品符合 IEC 61508、IEC 62061、ISO13849 和 IEC 61496 標(biāo)準(zhǔn)的要求。 2D 270° 功能安

兩片AD7124的spi可以并在一起嗎,分別片選。

兩片AD7124-8 芯片的spi接口能夠并聯(lián)在一起嗎?使用兩個(gè)GPIO引腳做片選信號(hào),目前這樣設(shè)計(jì)的,一片芯片的CS引腳已經(jīng)強(qiáng)制拉高了,另外一篇讀回來全部是0。不知道是電路本身有問題,還是不能這樣設(shè)計(jì)

發(fā)表于 09-21 18:03

具有集成電源的低輻射信號(hào)隔離器可滿足CISPR 32要求

電子發(fā)燒友網(wǎng)站提供《具有集成電源的低輻射信號(hào)隔離器可滿足CISPR 32要求.pdf》資料免費(fèi)下載

發(fā)表于 09-07 11:28

?0次下載

AD7124單次轉(zhuǎn)換速率突然變慢是為什么

AD7124程序中根據(jù)設(shè)定的次數(shù)進(jìn)行單次轉(zhuǎn)換,發(fā)現(xiàn)有時(shí)候單次轉(zhuǎn)換的速率會(huì)變很慢,這是為什么呢

發(fā)表于 08-07 10:56

AD7124-8按照19200輸出速率設(shè)置,實(shí)際五千不到怎么解決?

AD7124-8 直接說設(shè)置,

{0x01, 0x04C0, 2, 1}, 全功率,狀態(tài)和數(shù)據(jù)一起傳輸

{0x09, AD7124_CH_EN |AD7124

發(fā)表于 08-01 07:12

AD7124的程序如何將它導(dǎo)出成hex格式呢?

/platforms/SDP_K1/這個(gè)等。它的程序我也在網(wǎng)上下載下來了。參見附件。

EVAL-AD7124-3e1005bd4d41.zip

打開后是這樣的,

我的問題是,如果這個(gè)文件確實(shí)是用于AD7124的程序

發(fā)表于 07-23 08:13

AD7124-8手冊(cè)里沒提到上電時(shí)序,評(píng)估板原理圖是有上電時(shí)序的,那電路設(shè)計(jì)時(shí)是否需要上電時(shí)序?

AD7124評(píng)估板中的AVDD先上電,而后IOVDD才上電。但數(shù)據(jù)手冊(cè)中沒有體現(xiàn),實(shí)際設(shè)計(jì)電路時(shí)候是否需要這樣設(shè)計(jì)呢?

還有一個(gè)問題,這里為啥中等功率模式的均方根值噪聲明明小于全功率模式,為啥它

發(fā)表于 07-04 08:31

AD7124-8內(nèi)部溫度傳感器如何讀取,通道配置如何設(shè)置呢?

] - 0x800000) * 10 / 13584 - 2725; //讀AD7124內(nèi)部溫度,精度0.5°C

發(fā)現(xiàn)溫度比芯片表面溫度總是低了1.5°C左右,我哪里做錯(cuò)了,請(qǐng)告訴我正常的設(shè)置,多謝!

發(fā)表于 07-04 06:52

可滿足SIL2對(duì)硬件容錯(cuò)要求的AD7124芯片

可滿足SIL2對(duì)硬件容錯(cuò)要求的AD7124芯片

評(píng)論