基于MCU的設計面臨越來越激進的系統要求。無論是超低功耗,高性能還是兩者的難度組合,提供滿足當今激進目標的設計都是一項艱巨的任務。基于MCU的設計中最常見的操作之一是數據移動和數據傳輸功能的有效實現,這對于達到低功耗或高處理目標至關重要。詳細了解支持快速高效數據傳輸的現代MCU中包含的各種功能對于創建最佳MCU設計至關重要。

基礎知識

數據移動可以從一個功能塊到另一個功能塊,或關閉-chip使用標準接口。片上和片外傳輸通常涉及標準外設或存儲器接口。現在許多外圍設備都包含更高級別的功能,這些功能可以獨立于CPU運行。一個例子是將數據本地緩沖到外設,以便在方便的數據包中完成傳輸,從而最大限度地減少CPU開銷。

使用特殊的數據傳輸資源可以有效地完成片上數據移動。例如,外設和存儲器之間的數據傳輸可以使用智能直接存儲器訪問(DMA)功能完成。 CPU只需要參與設置傳輸參數(例如存儲器位置,傳輸長度和有效外設),并在傳輸完成時通知。 CPU可以在傳輸數據時執行其他任務,也可以將其置于低功耗模式以節省功耗。

許多現代MCU都包含先進的片上總線結構,有助于支持多個數據傳輸同時發生。當多個數據流同時移動時,可以實現最高的數據傳輸帶寬。此外,在這些情況下,與順序執行數據傳輸相比,功耗通常要低得多。現代MCU中還包含許多其他功能和功能,可幫助實現高效的數據傳輸。這里不可能說明所有這些,但我們將回顧一些最常見的功能。一旦了解了這些,通過擴展,將清楚如何使用其他功能來提高設計中的數據傳輸效率。我們將看看四個關鍵示例,了解如何提高數據傳輸效率:智能USB外設如何降低CPU開銷,智能DMA如何獨立管理復雜數據移動要求,低功耗模式如何在數據傳輸過程中提高電源效率,以及先進的片上總線矩陣如何支持多個同步數據傳輸功能。我們還將看到,當這些功能結合使用時,甚至可以實現更高的效率。

智能外設:USB示例

USB是一個很好的示例外設,用于顯示數據傳輸的可能改進。早期的USB實現最大吞吐量僅為1.5 Mb/秒,標準的一些元素基于這種慢速數據。隨著標準的更高性能版本的出現以及更廣泛的應用程序的定位,USB外設實現需要變得更具創造性。特別是,接近12 Mbit/s全速USB標準的理論最大值需要一些差異化的功能。 Atmel為XMEGA MCU的USB外設實現增加了幾項功能,可顯著提高效率。這些功能也很好地說明了可以與其他類型的外設一起使用的類似技術,以提高數據傳輸效率。

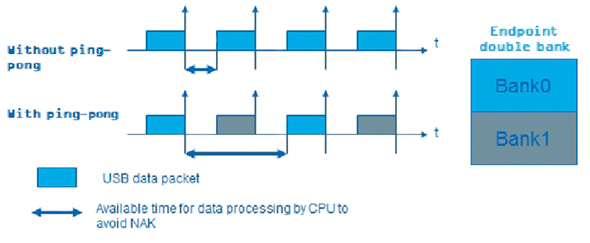

通常,單個內存緩沖區用于外設數據傳輸。如果數據緩沖區已滿,MCU將以NAK(否定確認)消息進行響應。收到NAK后,主機將等待并稍后重試傳輸。它將繼續重試,直到MCU可以成功接收數據。 Atmel XMEGA MCU使用乒乓緩沖區來消除此問題。乒乓緩沖區使用兩個存儲區進行數據傳輸。當一個銀行滿員時,主機可以將數據傳輸到另一個銀行。兩個緩沖區之間的交替消除了重試并提高了整體數據帶寬。此外,如圖1所示,在乒乓配置中使用兩個存儲體,使MCU有更多時間處理數據。如沒有乒乓球的圖所示,CPU只能處理傳輸之間的數據。通過乒乓,CPU可以在傳輸周期的一部分期間處理數據,并降低NAK被要求“趕上”數據處理要求的可能性。

圖1 :乒乓數據緩沖提高了效率(由Atmel提供)。

有助于提高Atmel XMEGA MCU數據傳輸效率的另一個關鍵特性是多數據包緩沖傳輸模式。當通過USB端口傳輸的數據包超過全速USB的BULK傳輸模式中允許的最大值(64字節)時,使用此模式。在包含此功能之前,需要在主機上拆分數據包,然后在接收器處合并,從而導致CPU負載增加。多數據包緩沖功能為USB外設添加專用硬件,以便在數據包大小大于最大USB數據包大小時自動執行數據包拆分和合并。請注意,此模式還減少了所需的中斷次數,因為只有在整個傳輸結束時才需要中斷CPU。這意味著CPU可以處理其他任務或進入睡眠模式,直到整個傳輸完成并準備好進行處理。

結合乒乓緩沖和多傳輸模式可以提高傳輸帶寬5.6 Mb/s(在沒有任何特性的基線BULK傳輸實現中)為8.7 Mbits/s。也許更重要的是,在使用這兩種功能的情況下,CPU負載從46%(在基線中)降低到僅9%。這些功能的結合使用可以在性能和功耗方面實現出色的改進,這正是智能外設可為您的設計帶來的好處。在下一個設計中尋找關鍵外圍設備的類似功能。有關更多信息,Atmel提供有關XMEGA USB連接的產品培訓模塊。

使用智能DMA進行高效的數據傳輸

大多數設計人員熟悉的第一個面向數據傳輸的特殊功能可能是直接內存訪問(DMA)。此塊可以自動將數據從源移動到目標。第一代DMA傳輸功能只不過是一個地址寄存器,它可以與一個小型狀態機一起遞增,以管理存儲器的讀寫信號。現代DMA控制器包括高級功能,可以從最復雜的數據傳輸操作中盡可能地卸載CPU。 Renesas RX621 MCU系列DMA實現是一個很好的例子,可以看到一些可用于數據傳輸功能的更高級功能。

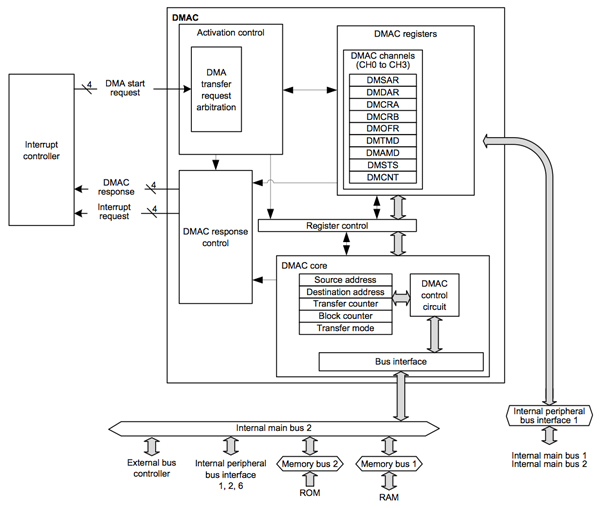

RX621 MCU DMA控制器(圖2)可以連接到中斷控制器,以便中斷驅動數據轉移是可能的。例如,智能外設可以緩沖數據,直到數據包可用于傳輸。它可以向DMA控制器發出中斷,并且數據包可以移動到主存儲器以供CPU處理。在大量數據包可用之前,CPU可能不需要處理數據,因此DMA控制器可以等到已經傳輸了足夠的數據包以便向CPU發出啟動中斷。請注意DMA與外設數據緩沖區,較大的主內存緩沖區和集成中斷系統的使用如何協同工作以消除CPU數據傳輸開銷。您可以通過將算法與MCU中的自主數據傳輸資源相匹配來實現顯著的效率提升。

圖2:Renesas RX621 DMA控制器框圖(由Renesas提供)。

RX621 DMA控制器具有四個獨立通道和多種尋址模式,無需CPU干預即可支持復雜的數據傳輸。例如,在DMA傳輸期間使用偏移量添加會跳過存儲器序列中的地址。這允許在目的地地址處自動收集分散的源數據元素。您甚至可以使用偏移添加功能實現復雜的操作,如矩陣翻轉(數據元素的X和Y位置交換)。當所有需要的數據連續存儲時,這些類型的操作可以為非常有效的CPU處理分段數據。如果CPU需要不按順序訪問數據,則緩存未命中可能會顯著降低處理效率。尋找類似的機會來收集數據,以便在數據處理算法的“內部循環”中實現高效的CPU訪問。

RX621還包括兩個其他DMA功能,可進一步提高數據傳輸效率,數據傳輸控制器(DTC)和外部存儲器DMA控制器(EXDMA)。 DTC是類似DMA的功能,但數據傳輸信息(起始地址,傳輸長度等)作為激活向量存儲在主存儲器中。這允許支持更復雜的數據傳輸操作。一旦當前傳輸完成,可以通過自動移動到新的激活向量來實現傳輸鏈。通過管理傳輸記錄中的各種鏈接,可以定義復雜的數據傳輸操作,然后根據所需操作的需要將其鏈接在一起。 CPU開銷最小化,因為它只需要在傳輸啟動之前管理鏈接配置數據的設置和拆除EXDMA子系統專為外部存儲器總線傳輸而設計。它具有兩個通道和普通DMA控制器的許多常規功能。另外一種傳輸模式Cluster Transfer可以有效地用于管理復雜的數據緩沖結構。雙地址模式用于有效地同時進行兩次數據傳輸。一次數據傳輸將數據集從一個位置移動到集群存儲區域。第二次傳輸用于將數據從群集區域移動到不同的存儲區域。這種方法可以簡化網絡數據包和視頻幀的數據結構管理,從而消除CPU實現常見的緩沖區管理功能。尋找更專業的DMA控制器功能,因為MCU變得更加注重應用。

使用低功耗模式提高數據傳輸效率

實例表明,通過消除CPU甚至復雜的數據傳輸操作中的低級別參與,有很多機會減少CPU開銷。這引出了一個問題,“如果不需要實現數據傳輸操作,CPU應該做什么?”在某些情況下,將CPU操作與數據傳輸重疊是有效的。通常捕獲大量數據然后讓CPU執行算法的處理和控制部分。如果可以捕獲下一個數據集,則通過使用外設和DMA控制器在CPU對先前數據集進行計算時實現數據傳輸,有效處理帶寬顯著增加。如果您發現CPU足夠強大,只需要一小部分處理能力,那么將CPU置于低功耗模式可能是有意義的,直到需要進行數據處理。

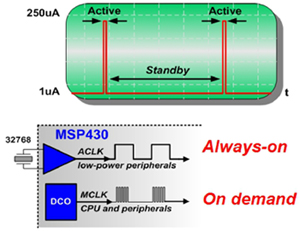

德州儀器MSP430 MCU系列具有多種低功耗模式,可用于在算法的一部分不需要CPU時切斷功率。如圖3底部所示,低功耗模式下有兩個時鐘源:按需高速數字控制振蕩器(DCO)源時鐘,MCLK和始終開啟的低速外設時鐘,ACLK。在活動模式下,MCU處于最高功率狀態。兩個時鐘都處于活動狀態,MCU的功耗約為250μA。在CPU關閉模式下,CPU關閉且時鐘均打開,功耗為35μA。在待機模式下,CPU和DCO時鐘關閉,而ACLK打開。在此模式下,功耗為0.8μA。最后,在全關模式下,CPU和時鐘關閉,功耗僅為0.1μA。通過減少CPU處于活動模式的時間,并且如果待機功率足夠低,則可以最小化由圖3頂部曲線下面積表示的總功率。

圖3:TI MSP430有功功率,待機功耗和快速時鐘喚醒時間(由德州儀器提供)。

在Active Power中花費的時間不僅取決于所需的處理時間量,還取決于轉換進入和退出低功耗狀態所需的時間。在TI MSP430上(有關更多信息,請參閱TI產品培訓模塊),MCLK可在200 ns內激活,使喚醒時間幾乎瞬間完成。這種快速喚醒時間意味著等待時鐘變為活動狀態所浪費的功率更少,因此可以立即開始處理。快速處理能力,快速喚醒時間和低功耗模式下的低功耗是高效MCU設計的“最佳點”。確保在MCU設計中仔細考慮這些元素。

使用片上總線矩陣進行多個同步數據傳輸

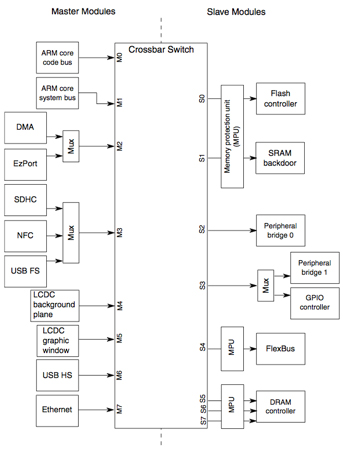

在前面的示例中您可能已經考慮過的一個可能的瓶頸,其中有大量的同時數據傳輸正在發生,要求多個片上總線有效地承載所有這些數據流量。具有高效多總線實現的MCU的一個例子是飛思卡爾Kinetis K70 MCU。 K70使用縱橫開關(如圖4所示)連接各種總線主模塊和總線從模塊。圖左側的八個總線主站可以連接到圖右側的八個從站。請注意,某些主服務器共享端口。例如,DMA和EzPort共享主端口M2。這些主設備永遠不會同時處于活動狀態,因此共享相同的主端口并不會發生沖突。

在某些多總線實現中,主設備可以連接到哪個從設備存在限制。 Kinetis K70實現了縱橫開關,因此每個主設備都可以連接到每個從設備。這支持大量重疊的數據傳輸。特別是Kinetis K70的一個應用是針對需要大量數據傳輸的優化,是觸摸屏LCD圖形用戶界面(GUI)。圖4中的圖表顯示LCD控制器背景平面和LCD控制器圖形窗口都具有單獨的主設備。還有多個DRAM控制器從設備,因此兩個LCD主設備都可以訪問DRAM中自己的內存緩沖區。這顯著降低了管理GUI顯示的CPU開銷。

圖4:飛思卡爾Kinetis K70縱橫交換機支持重疊數據傳輸(由飛思卡爾提供)。

縱橫交換機上的其他主機也可以重疊操作以提高效率。例如,以太網主設備可以通過DRAM控制器直接向/從DRAM傳輸數據,而DMA控制器則管理速度較慢的外設和片上存儲器之間的傳輸。算法可以根據處理要求輕松優化,而不會遇到連接不太良好的總線系統會造成的人為瓶頸。有關更多信息,請參閱飛思卡爾Kinetis產品培訓模塊。

總結

具有特殊數據傳輸功能和智能外設的MCU可以實現非常高水平的數據傳輸效率。但是,由于數據傳輸是絕大多數MCU設計中最常用的功能,因此了解如何有效地使用這些功能對于實現低功耗和高性能的積極設計目標至關重要。本文中說明的示例可以擴展到各種其他數據傳輸功能,因此您可以達到設計所需的效率水平。

-

mcu

+關注

關注

146文章

17806瀏覽量

359576 -

控制器

+關注

關注

114文章

16933瀏覽量

182667 -

存儲器

+關注

關注

38文章

7625瀏覽量

166239

發布評論請先 登錄

SPI數據傳輸緩慢問題求解

捷多邦的IoT PCB:數據傳輸的未來

MCU分布式模塊化自動測量單元:數據傳輸與處理能力如何?

信道帶寬與數據傳輸速率關系

MPU數據傳輸協議詳解

ptp對實時數據傳輸的影響

PCIe數據傳輸協議詳解

socket 數據傳輸效率提升技巧

CAN總線數據傳輸速率設置

LORA模塊的數據傳輸速率

網絡數據傳輸速率的單位是什么

通過數據傳輸滿足MCU激進系統的設計

通過數據傳輸滿足MCU激進系統的設計

評論