隨著PCB工作速率的提高與一些區(qū)域緊耦合布線,串?dāng)_crosstalk和阻抗impedance檢查變得越來越有必要。傳統(tǒng)的基于路的分析不能滿足精度要求。需要三維全波電磁場仿真工具來模擬與頻率相關(guān)的復(fù)雜的PCB結(jié)構(gòu),然而對整板進行有限元電磁場分析并不現(xiàn)實,而且得到的S參數(shù)不能直觀的反映系統(tǒng)的串?dāng)_水平。

Xpeedic Heracles工具集成了一種全新的混合求解器技術(shù),提高了速度和精度,并嵌入了新的串?dāng)_評估標準來處理S參數(shù)從而評估系統(tǒng)的串?dāng)_水平。Heracles允許工程師在幾小時內(nèi)完成對整板信號的串?dāng)_分析掃描。這顯著地減少了評估的時間,能夠讓設(shè)計更快通過審核。

簡介

隨著高速I/O接口的數(shù)據(jù)速率不斷提高,如以太網(wǎng)、PCI Express、DDR、USB、SATA/SAS等,串?dāng)_對高速PCB設(shè)計人員帶來了巨大的挑戰(zhàn)。無法準確捕獲串?dāng)_可能會產(chǎn)生信號/ 電源完整性問題和EMC等問題。如果能準確模擬串?dāng)_并評估其影響,則可以減少設(shè)計迭代,再配套恰當(dāng)?shù)膬?yōu)化,將有效加快產(chǎn)品上市的速度。

串?dāng)_存在于高速PCB Layout的不同區(qū)域,而其中很重要的來源是連接器和封裝下的過孔引腳區(qū)域。由于過孔的復(fù)雜性需要冗長的仿真計算量,傳統(tǒng)的PCB設(shè)計中基本忽略對過孔引腳串?dāng)_影響的評估。同時, PCB layout的復(fù)雜3D特性,幾乎不可能用分析或經(jīng)驗的方法來準確模擬這些區(qū)域中的串?dāng)_。工程師一般會選擇三維全波電磁場求解器,如有限元法,它可以準確地評估過孔間,過孔與布線、布線間的串?dāng)_。然而,3D全波EM仿真不僅設(shè)置起來非常麻煩,而且相當(dāng)耗時。 因此,用強力EM仿真來執(zhí)行全板crosstalk掃描總是讓人望而卻步。

Xpeedic Heracles混合求解器利用PCB的層疊結(jié)構(gòu)特性,采用區(qū)域分解的思想來降低問題的復(fù)雜性,實現(xiàn)對全板串?dāng)_分析掃描速度的提升。串?dāng)_掃描首先從用戶配置的信號網(wǎng)絡(luò)掃描開始。工具會自動抽取via區(qū)域和BGA或connector下方扇出區(qū)域,因為這些區(qū)域高速信號相互之間以及與低速信號電源地孔之間的布線很容易不合理而造成大的串?dāng)_。仿真的頻段可根據(jù)用戶選擇的 net的數(shù)據(jù)速率自動確定,之后軟件將合理切割出來的區(qū)域用混合求解器進行全波求解。衡量串?dāng)_大小的方法有對比ICN(串?dāng)_噪聲的積分)和時域的TDT,只需將從S參數(shù)計算得到的值與pass /warning /failure門限作對比就可知串?dāng)_情況。串?dāng)_結(jié)果可以通過圖表或者曲線的形式來展現(xiàn),工具也將結(jié)果和實際的layout之間做了鏈接交互,用不同顏色來告知用戶對應(yīng)的問題位置 。對于其余的高速網(wǎng)絡(luò),該流程自動重復(fù)就可實現(xiàn)全板串?dāng)_掃描。通過使用該工具自動SI驗收流程,用戶能夠在幾小時內(nèi)實現(xiàn)完整的全板串?dāng)_掃描,從而顯著縮短布局后檢查時間,將時間留給布局優(yōu)化并確保全板覆蓋。

背景

當(dāng)信號在互連結(jié)構(gòu)中傳輸時會產(chǎn)生串?dāng)_,這些結(jié)構(gòu)包括PCB的通孔走線、封裝和連接器,也會與相鄰的互連產(chǎn)生邊緣和臨近相互作用。 從電路的角度來看,串?dāng)_是由互連之間的互感和互容引起的。 通常這些結(jié)構(gòu)的電感和電容矩陣可由2D準靜態(tài)場求解器計算。

對于多條傳輸線組成的結(jié)構(gòu),單位長度的RLGC參數(shù)可以快速獲得,然后放到電路仿真器中如HSPICE。 然而,均勻?qū)w的假設(shè)使得該方法不足以模擬復(fù)雜的3D PCB結(jié)構(gòu),并且準靜態(tài)假設(shè)忽略了高頻效應(yīng),這對于高速系統(tǒng)變得越來越重要。 另一方面,三維全波求解器能夠解決復(fù)雜的三維結(jié)構(gòu)并捕獲頻率相關(guān)的損耗,色散,輻射以及大多數(shù)其他電磁現(xiàn)象。 缺點是它需要更多的專業(yè)知識才能使用,通常需要數(shù)小時,有時需要數(shù)天來模擬,并且輸出的是表格形式的S參數(shù),這需要額外的后處理流程才能用于串?dāng)_分析評估。對于具有過孔和走線的多層PCB結(jié)構(gòu),三維場求解器非常耗時間與存儲。 特別是對于串?dāng)_分析,越來越多的過孔和布線需要被考慮。 因此急需一個更有效率的EM求解器技術(shù)。

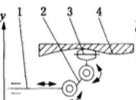

Xpeedic Heracle工具采用了全新的基于區(qū)域分解的混合求解器Hybrid Solver,與傳統(tǒng)的3D求解器相比,它可以保持3D仿真精度的同時亦有顯著的加速。 首先,它將3D PCB結(jié)構(gòu)分解為多個層,具有純過孔的層使用via solver求解,具有過孔和布線的層則通過3D FEM求解。最終將這些結(jié)果級聯(lián)來獲得最終的S參數(shù)。 Hybrid Solver技術(shù)如圖1所示,對于一般過孔結(jié)構(gòu),它比傳統(tǒng)求解器已經(jīng)表現(xiàn)出一個數(shù)量級的加速。

圖1 Hybrid Solver 圖示

實現(xiàn)高速PCB的全板串?dāng)_掃描

Xpeedic Heracles實現(xiàn)全板串?dāng)_掃描的流程如圖2所示。

圖2 Heracles 全板串?dāng)_掃描的流程

Heracles串?dāng)_掃描工具從Allegro->Xpeedic->Heracles中啟動。第一步,用戶定義高速接口的規(guī)范protocols和相應(yīng)的通過/失敗的標準,工具中內(nèi)嵌了廣泛應(yīng)用的的高速互聯(lián)接口掃描配置如 PCI-E, SAS, DDR等,用戶可以直接調(diào)用;第二步,工具根據(jù)定義好的規(guī)范對PCB板進行掃描,找到高速接口相應(yīng)的RefDes和net,圖3給出了第一步和第二步的有相關(guān)界面;第三步,工具會給每個串?dāng)_分析組產(chǎn)生仿真模型,并逐一進行EM仿真;第四步,收集S參數(shù)進行后處理,得到每個net的定量的串?dāng)_值并生成表格,通過與定義的規(guī)范的比較來給出通過/失敗的判斷。

圖3 Heracles 設(shè)置界面

圖4 Heracles 串?dāng)_結(jié)果顯示

從EM仿真中獲得計算后的S參數(shù)來定量的分析串?dāng)_,Heracles提供了兩種方法。首先針對給定的victim/aggressor設(shè)置,提取近端串?dāng)_(NEXT)和遠端串?dāng)_(FEXT)的S參數(shù),一種是通過對頻域的NEXT和FEXT的S參數(shù)進行FFT得到時域的TDT,取其最大值的總和,另一種是在頻域中,直接計算ICN(串?dāng)_噪聲的積分)來量化串?dāng)_水平。 ICN已經(jīng)被引入進IEEE 802.3標準中。 它將串?dāng)_的大小表示為頻域中的串?dāng)_噪聲相對于被傳輸信號的功率譜的加權(quán)和。 近端ICN,遠端ICN以及ICN總和的定義如下:

實現(xiàn)全板DRC+的高級規(guī)則掃描

Heracles除了提供了強大的全板串?dāng)_掃描,還集成了多種DRC+的高級幾何規(guī)則掃描,比如:

?背鉆backdrill檢查

?接地完整性檢查

?trace necking檢查

?impedance掃描

總結(jié)

Heracles集成了一種新穎的混合求解器技術(shù),與傳統(tǒng)的3D求解器相比,該技術(shù)可以顯著提高3D仿真速度。同時,我們還通過頻域和時域中的后處理S參數(shù)開發(fā)了用于量化串?dāng)_水平的串?dāng)_指標。 結(jié)合這兩種技術(shù),工程師可以在幾小時內(nèi)按計劃實現(xiàn)全板串?dāng)_掃描,從而顯著縮短layout后的審核時間,實現(xiàn)layout優(yōu)化并確保及時簽核。

-

pcb

+關(guān)注

關(guān)注

4349文章

23400瀏覽量

406375 -

信號完整性

+關(guān)注

關(guān)注

68文章

1432瀏覽量

96404 -

電磁場

+關(guān)注

關(guān)注

0文章

797瀏覽量

47847

原文標題:針對高速PCB設(shè)計信號完整性簽核的快速全板串?dāng)_掃描

文章出處:【微信號:Xpeedic,微信公眾號:Xpeedic】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

混合電路和模塊技術(shù)簡史

一種適用于模擬/數(shù)字混合信號環(huán)境的接地技術(shù)

Nexar如何為FPGA設(shè)計提供一種全新的方法?

一種求解關(guān)鍵路徑的新算法

一種求解電大平臺天線互耦的時域積分方程快速算法

集成電路模塊布局問題的一種有效算法

一種實用的機器人控制器力/位混合控制技術(shù)

Xpeedic Heracles工具集成了一種全新的混合求解器技術(shù)

Xpeedic Heracles工具集成了一種全新的混合求解器技術(shù)

評論