了解如何對寄存器資源進行編碼,以便您的設(shè)計具有更少的控制集并以更高的系統(tǒng)速度運行,避免最常見的編碼錯誤,從而降低設(shè)備利用率和系統(tǒng)速度。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關(guān)注

關(guān)注

1643文章

21979瀏覽量

614493 -

賽靈思

+關(guān)注

關(guān)注

33文章

1796瀏覽量

132142 -

編碼

+關(guān)注

關(guān)注

6文章

967瀏覽量

55527

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

spartan 6 14位LVDS 反序列化

spartan 6系列的FPGA 與14位ADC 輸出LVDS信號 怎么實現(xiàn)1:14的串轉(zhuǎn)并呢?iserdes2 在ise里面最高只能實現(xiàn)8位啊

發(fā)表于 04-25 15:20

瑞蘇盈科FPGA CoaXPress解決方案,重構(gòu)地面遠程視頻編碼器性能邊界

(現(xiàn)場可編程門陣列)憑借其獨特的硬件可編程特性和強大的并行處理能力,為地面遠程視頻編碼器帶來了新的突破,成為構(gòu)建可靠、高性能遠程監(jiān)控系統(tǒng)的核心技術(shù)方案。解決方案在

FPGA Verilog HDL語法之編譯預(yù)處理

Verilog HDL語言和C語言一樣也提供了編譯預(yù)處理的功能。“編譯預(yù)處理”是Verilog HDL編譯系統(tǒng)的一個組成部分。Verilog HDL語言允許在程序中使用幾種特殊的命令(它們不是一般

一文詳解Verilog HDL

Verilog HDL(Hardware Description Language)是一種硬件描述語言,用于從算法級、門級到開關(guān)級的多種抽象設(shè)計層次的數(shù)字系統(tǒng)建模。現(xiàn)實生活中多用于專用集成電路

編碼器類型詳解:探索不同編碼技術(shù)的奧秘

編碼器類型詳解:探索不同編碼技術(shù)的奧秘 在自動化、機器控制和數(shù)據(jù)處理等領(lǐng)域,編碼器作為關(guān)鍵的傳感器組件,扮演著至關(guān)重要的角色。它們通過將物理位置、速度或方向轉(zhuǎn)換為電信號,為各種設(shè)備提供

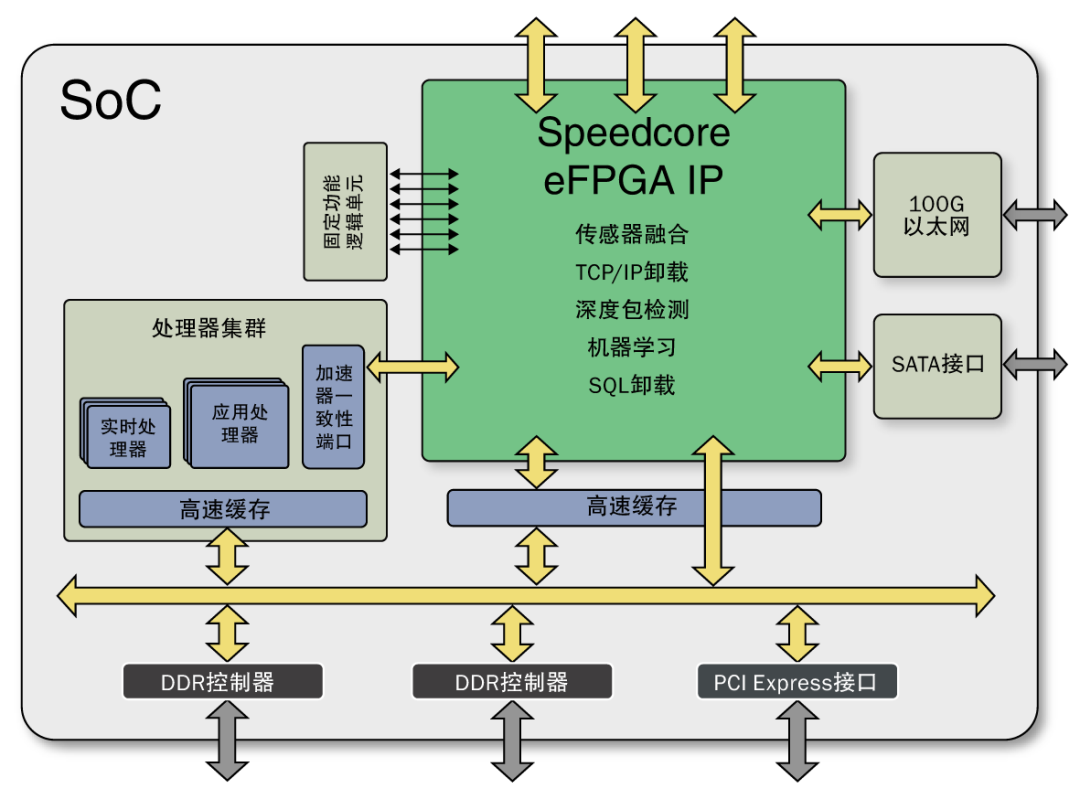

Achronix Speedcore eFPGA的特性和功能

Speedcore嵌入式FPGA(embedded FPGA,eFPGA)知識產(chǎn)權(quán)(IP)產(chǎn)品是Achronix公司于2016年推出的顛覆性技術(shù),并于當年開始向最終客戶交付,目前出貨量

Xilinx 7系列FPGA PCIe Gen3的應(yīng)用接口及特性

Xilinx7系列FPGA集成了新一代PCI Express集成塊,支持8.0Gb/s數(shù)據(jù)速率的PCI Express 3.0。本文介紹了7系列FPGA PCIe Gen3的應(yīng)用接口及一些特性

Verilog HDL的基礎(chǔ)知識

本文繼續(xù)介紹Verilog HDL基礎(chǔ)知識,重點介紹賦值語句、阻塞與非阻塞、循環(huán)語句、同步與異步、函數(shù)與任務(wù)語法知識。

FPGA Verilog HDL代碼如何debug?

今天給大俠帶來在FPAG技術(shù)交流群里平時討論的問題答疑合集(十一),以后還會多推出本系列,話不多說,上貨。

FPGA技術(shù)交流群目前已有十多個群,QQ和微信均覆蓋,有需要的大俠可以進群,一起交流學(xué)習(xí)

發(fā)表于 09-24 19:16

FPGA芯片架構(gòu)和資源有深入的理解,精通Verilog HDL、VHDL

、計算機相關(guān)專業(yè),具有良好的專業(yè)基礎(chǔ)知識。

2.工作年限不限,有工作經(jīng)驗或優(yōu)秀應(yīng)屆畢業(yè)生亦可。

3.對FPGA芯片架構(gòu)和資源有深入的理解,精通Verilog HDL、VHDL編程語言,熟悉時序約束、時序分析

發(fā)表于 09-15 15:23

FPGA Verilog HDL有什么奇技巧?

今天給大俠帶來在FPAG技術(shù)交流群里平時討論的問題答疑合集(九),以后還會多推出本系列,話不多說,上貨。

交流問題(一)

Q:Verilog 有什么奇技淫巧?

A:在 Verilog 中,以下這些

發(fā)表于 09-12 19:10

Spartan6 引腳輸出電壓求教

用Spartan-6 FPGA驅(qū)動ADC AD9265,由于原理圖設(shè)計問題(SVDD=1.8V) ,部分引腳控制線(AD9265的DFS引腳)接收的電平標準應(yīng)該是1.8V,但是所有FPGA的VCCO

發(fā)表于 06-27 10:12

FPGA | Xilinx ISE14.7 LVDS應(yīng)用

。

同時,Xilinx器件內(nèi)部信號內(nèi)部還提供了100歐姆電阻匹配,可參考Spartan-6 FPGA SelectIO Resources(UG381)

補充:

若要實現(xiàn)高速通信的場合,可以

發(fā)表于 06-13 16:28

Spartan-6 FPGA HDL編碼技術(shù)的特性介紹

Spartan-6 FPGA HDL編碼技術(shù)的特性介紹

評論