1、前言

集成電路具有體積小,重量輕,引出線和焊接點少,壽命長,可靠性高,性能好等優點,同時成本低,便于大規模生產。它不僅在工、民用電子設備如收錄機、電視機、計算機等方面得到廣泛的應用,同時在軍事、通訊、遙控等方面也得到廣泛的應用。

但隨著半導體工藝的不斷發展和通信技術的不斷提高,以超大規模、高集成度和復雜性為特征的通信集成電路芯片物理設計,相比于普通的消費類產品芯片(如LED芯片,FLASH芯片等),在超深亞微米工藝下面臨著更為嚴峻的挑戰:一、工藝特征尺寸的不斷縮小、電源電壓的不斷降低、電源噪聲對芯片性能的影響日益凸顯,已成為超大規模通信集成電路物理設計中一個不可忽視的問題;二、高速通信集成電路芯片的時序對于芯片制造過程中產生的偏差越來越敏感,精確的電路模型及準確的時序分析方法成為制約通信集成電路芯片能否實現快速時序收斂的關鍵;三、通信集成電路芯片通常需要支持各種高速接口電路的應用,從而造就了獨特的時鐘樹拓撲結構——網狀時鐘樹,而通信芯片固有的超大規模的特性更加重了這種復雜高速時鐘樹優化的難度;四、隨著數據傳輸速度和容量的不斷提高、信道噪聲對信號質量的影響越來越大,高速串并/并串轉換器(HighSpeedSerdes,HSS)的抗噪性、傳輸信道數量及其建模仿真的精確度成為影響通信系統設計的重要因素。IBM針對這些通信芯片的物理設計難點,較為詳細地介紹了相應的解決方案。

2、物理設計難點分析及解決方案

微電子技術發展的基本特征就是遵循摩爾定律。器件特征尺寸不斷地縮小,但在尺寸縮小的同時,要保證芯片的高性能/價格比,低成本,可靠性高。針對該物理設計難點,IBM提出了相應的解決方案,具體介紹如下。

2.1 電源噪聲分析

任何電源及輸電線都存在內阻,正是這些內阻引起電源的噪聲干擾。如果沒有內阻存在,無論何種噪聲都會被電源短路吸收,在線路中不會建立起任何干擾電源。當芯片上的信號開始跳變時,如由0到1,電源網絡的階躍響應會如圖1所示。最低電壓值由芯片上的靜態電容值與翻轉電容值的比例決定,跳變后的諧振則為典型的LC諧振,靜態電壓降則是平均功率的體現,由網絡中的寄生電阻導致。穩態的交流響應與工作頻率相關,其波動的電壓值隨著工作頻率的增加而減小.

由于大規模通信集成電路芯片通常帶有各種復雜的高速接口,并在整個產品的工作過程中要求有很高的可靠性,因此芯片的電源設計起著極其關鍵的作用。為保證芯片的電源完整性,在芯片的設計流程中必須對IO的同步開關噪聲SSN(SimultaneousSwitchNoise)、芯片上的動態電源噪聲、靜態壓降、ESD(Electro-StaticDischarge)靜電保護以及電遷移EM(ElectroMigration)進行有效的檢查和簽收。

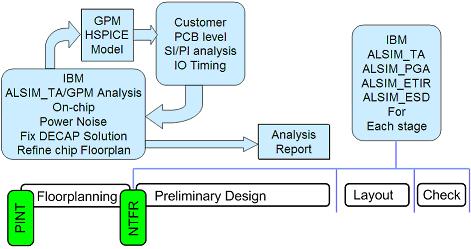

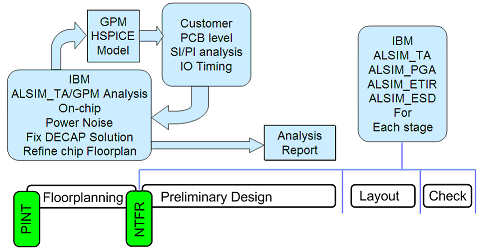

在進行超大規模集成電路的設計過程中,IBM有一套完整的流程對電源噪聲進行分析(如圖1所示),能夠在芯片的布局階段盡早發現和解決芯片布局與電源設計上存在的問題,以減少設計反復的時間。電源噪聲檢查在芯片設計過程中是一個重要的簽收環節,完整的設計和分析流程保證了IBM能夠提供高質量的專用集成電路芯片。

圖1 電源噪聲分析流程

IBM的電源噪聲分析流程貫穿了整個芯片設計過程,包含了兩個噪聲評審會議和一系列分析工具。在芯片布局之前,噪聲分析小組會和項目的物理設計工程師一起召開PINT(Post-IDRNoiseTeamReview)會議,對芯片的設計規格進行審查,找出設計中可能存在的風險,提出在布局時需注意的事項,讓物理設計工程師在布局前對整個芯片的電源噪聲情況有所了解,避免由于電源噪聲無法滿足而反復修改布局,造成不必要的浪費。在芯片布局階段,負責電源噪聲分析的工程師緊跟芯片布局的變化,充分利用IBM的GPM(GenericPackageModel)和ALSIM(AustinLinearSimulator)系列工具及時評估芯片的電源噪聲。

GPM是一個可以快速分析IO同步開關噪聲的建模和分析工具。GPM針對芯片中包含IO的局部區域建立HSPICE模型,其中包含通用的封裝RLC模型,芯片上的電源分配網絡,IO驅動器模型和模擬一般邏輯電路翻轉的等效模型。GPM的分析流程可以簡單總結為以下幾個步驟:一、使用AutoGPM在芯片上自動找到IO最密集的區域,然后生成Hspice的網表;二、在網表中填入仿真所需要的參數;三、分析仿真結果,可調整電容數量來滿足動態壓降的要求。由于GPM分析不需要成熟的芯片布局,建模和仿真速度快,因此可以盡早分析IO對電源噪聲的影響,為芯片的IO布局提供快速的參考,評估IO所需的電源濾波方案,避免在設計中形成電源噪聲的熱點。一旦芯片布局確定,GPM模型可以代表實際芯片的IO翻轉情況,該模型可以交付客戶,讓客戶聯合系統的板級模型進行芯片、封裝和PCB的信號完整性分析和時序分析。分析的結果可以幫助客戶在芯片設計早期評估系統的性能,同步地進行PCB的設計,確定更加合理的芯片時序約束。

ALSIM_TA(TransientAnalysis)是一個高效的全芯片動態電源噪聲仿真分析工具。相對于GPM側重于對整個芯片進行局部仿真,ALSIM_TA更著重于分析芯片的全局噪聲情況,其主要工作在兩種模式下,Floorplan(可以在設計的早期來運行,為設計的布局提供指導,有效地減少Iteration) 和FinalAnalysis(當設計已基本成型時,基于規劃好的電源網絡,封裝的寄生參數,準確的電流波形和頻率信息,這時ALSIM_TA就可以進行更為精確的噪聲分析。)分析流程可以簡單歸納為以下幾個步驟:一、建立電流模型;二、建立電源網絡分布模型并簡化;三、將各模型和封裝參數結合,進行暫態仿真分析。仿真過程中使用了芯片的封裝模型,片上電源網絡模型和代表各種邏輯電路翻轉的電流波形。通過ALSIM_TA仿真可以得到整個芯片電源噪聲峰峰值,動態壓降等信息在芯片上的分布情況,并以二維圖形直觀地顯示(如圖2所示)。ALSIM_TA的結果可以直觀地評估芯片的布局和電源濾波方案對電源噪聲的影響。

圖2 ALSIM_TA仿真結果

根據早期的ALSIM_TA和GPM分析結果,物理設計工程師可以盡早優化芯片布局,通過增加噪聲源和噪聲敏感的器件之間的距離,增加片上去耦電容等方式獲得較好的噪聲性能。

:

-

電源

+關注

關注

185文章

18262瀏覽量

254976 -

芯片

+關注

關注

459文章

52153瀏覽量

436020 -

集成電路

+關注

關注

5418文章

11943瀏覽量

367073

發布評論請先 登錄

單片機之間的通信方式/難點/解決方案

新唐針對BMS提出完整解決方案

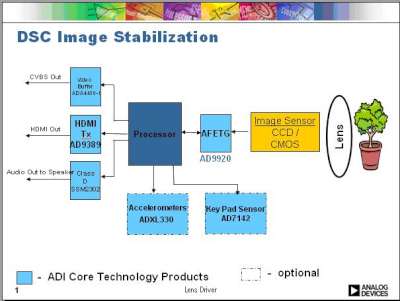

世平集團所代理產線ADI針對DSC提出一系列解決方案

R&S對WiMAX物理層的測試解決方案

專家提出MicroLED顯示屏幕的全彩化解決方案

ADI提出針對伺服電機控制的解決方案

新唐針對BMS提出完整解決方案

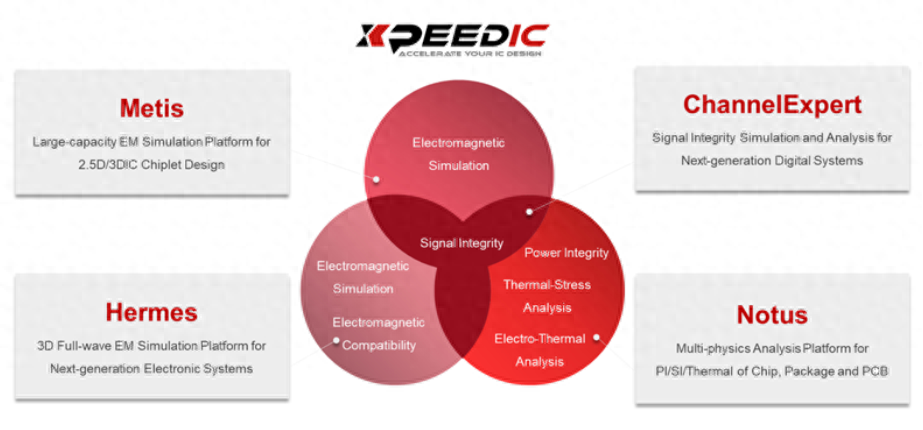

DesignCon2024 | 芯和半導體發布針對下一代電子系統的“SI/PI/多物理場分析”EDA解決方案

芯和半導體最新發布“SI/PI/多物理場分析”EDA解決方案

針對物理設計難點進行分析及提出解決方案

針對物理設計難點進行分析及提出解決方案

評論