在低于40納米的超深亞微米VLSI設(shè)計(jì)中,時鐘樹網(wǎng)絡(luò)在電路時序收斂、功耗、PVT變異容差和串?dāng)_噪聲規(guī)避方面所起的作用要更重要得多。高性能DSP芯片會有大量關(guān)鍵時序路徑,會要求時鐘偏斜超低的全局時鐘分布。兩點(diǎn)間時鐘偏斜若不合要求,特別是如果這些點(diǎn)間還存在數(shù)據(jù)路徑的話,可能會限制時鐘頻率或?qū)е鹿δ苄藻e誤。

本文中所描述的是以500MHz時鐘頻率運(yùn)行的DSP核心,多數(shù)時序關(guān)鍵路徑都有超過20級的邏輯層。考慮到時鐘抖動率和建立時間,滿足高頻需求真的是項(xiàng)非常具有挑戰(zhàn)性的任務(wù)。如果使用傳統(tǒng)時鐘樹設(shè)計(jì)方法,我們至多能獲得全局時鐘偏斜為150ps的時鐘樹。而在早期STA階段,我們會發(fā)現(xiàn)由于時鐘偏斜不平衡而導(dǎo)致的從-100ps到0ps的建立時序違規(guī)高達(dá)1萬多條。這些均使得偏斜較低的時鐘設(shè)計(jì)方法成為了一種迫切需要,而且還要求這種方法應(yīng)能夠改善時鐘PVT變異容差并降低功耗。

用以衡量DSP時鐘樹分布結(jié)果質(zhì)量(QOR)的參數(shù)主要有三個:一是RC分布擴(kuò)展;二是插入延時擴(kuò)展;三是同級延時擴(kuò)展。我們將比較新時鐘設(shè)計(jì)方法與傳統(tǒng)方法,產(chǎn)生時鐘衡量指標(biāo)。

時鐘設(shè)計(jì)

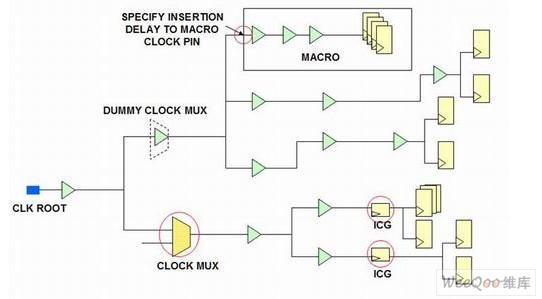

本文中40nm 500MHz DSP設(shè)計(jì)使用了一種可覆蓋整個功能塊的單節(jié)點(diǎn)、雙相全局時鐘,在這個案例下我們將其稱為CLK。DSP的時鐘結(jié)構(gòu)如圖1所示,CLK可驅(qū)動超過 5.3萬的觸發(fā)器,因此我們建議采用一種有效的設(shè)計(jì)方法來創(chuàng)建更魯棒的低偏斜時鐘。

圖1 DSP功能塊的時鐘結(jié)構(gòu)

時鐘緩沖器選擇

驅(qū)動強(qiáng)度超低和超高的時鐘緩沖器都是隱藏的。

隱藏超高驅(qū)動強(qiáng)度單元有以下優(yōu)勢:降低由于打開關(guān)閉高驅(qū)動單元而導(dǎo)致的局部時鐘樹功耗和動態(tài)IR違規(guī);縮短每級時鐘的有效網(wǎng)路長度。

隱藏超低驅(qū)動強(qiáng)度單元有以下優(yōu)勢:減少時鐘樹根上緩沖器總數(shù);避免EM問題的潛在風(fēng)險(xiǎn)性。它也將帶來一些劣勢,比如:可能潛在地提高時鐘插入延時;可能導(dǎo)致同樣插入延時具有更高時鐘樹功耗(同時減輕局部動態(tài)IR降熱點(diǎn))。

在此我們還禁用了時鐘樹反相器(CTI),因?yàn)樗鼘?dǎo)致毫無差別的時鐘樹拓?fù)浣Y(jié)構(gòu)。而且我們還發(fā)現(xiàn)微捷碼工具用來創(chuàng)建只有緩沖器(buffer-only)的時鐘樹拓?fù)浣Y(jié)構(gòu)會比用來創(chuàng)建混合型時鐘樹拓?fù)浣Y(jié)構(gòu)更有效。

時鐘斜率控制

非可控性斜率違規(guī)不僅會導(dǎo)致時鐘插入延時的增加和電學(xué)DRC違規(guī),而且還會造成不符合通道熱載流子規(guī)則的設(shè)計(jì)違規(guī)。在本文中,我們使用了以下兩種方法來控制好時鐘斜率:

1)限制每個時鐘樹單元(icg、ctb) 的扇出。

2) 在CTS過程中使用微捷碼Talus命令明確定義時鐘樹斜率范圍,當(dāng)依據(jù)全局‘斜率’范圍所設(shè)置的斜率范圍還不如這個范圍嚴(yán)格時則以這個范圍為準(zhǔn)。

force limit slew $m/mpin:clk -clock 250p -context $m

增強(qiáng)區(qū)別于微捷碼自帶“fix clock”的選項(xiàng)/方法

微捷碼提供了一個名稱為‘fix clock’的可預(yù)先創(chuàng)建時鐘插入腳本。微捷碼自帶CTS圍繞兩個命令為中心:i)“run route clock”(RRC) ,創(chuàng)建初始時鐘樹;ii) “run gate clock”(RGC),調(diào)整RRC所創(chuàng)建的時鐘樹。

RRC有個默認(rèn)值為2.0的隱藏選項(xiàng)。時鐘樹布線器可根據(jù)這個選項(xiàng)的指示,通過2.0因子超速驅(qū)動時鐘單元,其效果會比根據(jù)其時序弧報(bào)告指示來得更好。雖然這個選項(xiàng)可能用于高驅(qū)動單元時是極為理想,但當(dāng)高驅(qū)動單元處于隱藏狀態(tài)時它達(dá)不到最佳結(jié)果。如果我們發(fā)現(xiàn)時鐘樹處于緩沖狀態(tài)時,那可能就是出于這項(xiàng)功能的原因。

對該設(shè)計(jì)進(jìn)行的各項(xiàng)實(shí)驗(yàn)均顯示出,這種開關(guān)的最佳值為1.5。在本文中,微捷碼自帶CTS腳本通過編輯可加入這個隱藏的開關(guān)。

到RRC的最后,默認(rèn)使用標(biāo)準(zhǔn)全局和信號布線器執(zhí)行時鐘布線。微捷碼自帶CTS中標(biāo)準(zhǔn)全局和信號布線器用于65納米以上設(shè)計(jì)可能已足夠準(zhǔn)確,但若用于40納米設(shè)計(jì)則還需要在RGC之前執(zhí)行精確的詳細(xì)布局和高強(qiáng)度全局布線,這樣才可確保到時RGC時有準(zhǔn)確的時序信息來調(diào)整時鐘偏斜。

RGC后,建議再進(jìn)行一次詳細(xì)布局和高強(qiáng)度全局布線來完成RGC中新添加的時鐘偏斜緩沖器的布局,這樣才能為CTS后進(jìn)一步時序優(yōu)化提供必要時序信息。

時鐘串?dāng)_規(guī)避

在本文中,一直使用非默認(rèn)時鐘網(wǎng)路規(guī)則來降低串?dāng)_影響。如下所示,選擇較高M(jìn)ET層進(jìn)行時鐘網(wǎng)路布線:

rule layer preference Mn clock /sr70

rule layer preference Mn+1 clock /sr70

我們一直建議采用具有2倍寬和3倍間距的NDR(Non-default Rule)來降低耦和度。事實(shí)證實(shí),這對PTSI有很大幫助。微捷碼工具中所定義的非默認(rèn)規(guī)則。這種規(guī)則只應(yīng)用于MET3及更高層,同樣還只應(yīng)用于時鐘網(wǎng)絡(luò)中非葉級網(wǎng)路。

時鐘分析

時鐘分析是采用已開發(fā)的腳本,產(chǎn)生時鐘樹分布指標(biāo),*估時鐘樹的結(jié)果質(zhì)量(QOR)。

RC分布擴(kuò)展

RC延時分布是可用以改善設(shè)計(jì)期間時鐘樹魯棒性的第一個指標(biāo)。時鐘樹RC延時百分比等于互連線延時在每個接收端(sink)總插入延時中所占比率。

對于每個時鐘網(wǎng)路:

%RC delay = [RC delay ]/[RC delay + Gate delay]

窄(<10%)分布意味著良好的跨角點(diǎn)時鐘延時追蹤。互連線在時鐘路徑占主導(dǎo)地位與門在時鐘路徑占主導(dǎo)地位相交疊的機(jī)率比較小。這種分析不包括數(shù)據(jù)路徑時鐘樹。

圖2顯示了一種更好的RC擴(kuò)展分析 。在圖3中,采用了微捷碼自帶CTS的NOM角點(diǎn)RC擴(kuò)展率在25%以上,而圖2的則在15%左右。在圖3中,MAX 角點(diǎn)RC擴(kuò)展率在10%左右,而圖2的則在5%左右。

圖 2 使用新時鐘設(shè)計(jì)方法的RC擴(kuò)展

圖3 使用微捷碼自帶CTS的RC擴(kuò)展

插入延時擴(kuò)展

插入延時分布是可用以改善設(shè)計(jì)期間時鐘樹魯棒性的第二個指標(biāo)。不同角點(diǎn)的插入延時通過使用以下方法實(shí)現(xiàn)w.r.t WEAK角點(diǎn)(QC_MAX)標(biāo)準(zhǔn)化。

1) 每個時鐘接收端的插入延時是依據(jù)不同角點(diǎn)來計(jì)算的。稱呼延時為,Di,corner

2) 一個角點(diǎn)的插入延時率等于每個接收端插入延時除以WEAK角點(diǎn)插入延時。

Ri,corner = Di,corner/Di,WEAK

3) 上述插入延時率的平均值是針對每個角點(diǎn)來計(jì)算。

Avgcorner= ∑iRi,corner/N, 在此N系指接收端的數(shù)量

4) 每個接收端的插入延時率等于每個角點(diǎn)平均率的標(biāo)準(zhǔn)值。

NRi,corner=Ri,corner/Avgcorner

5) 現(xiàn)在,{NRi,corner}的劃分如圖4和圖5所示。WEAK角點(diǎn)結(jié)構(gòu)位于y=1這一條直線。

圖4顯示了一個50ps的較低擴(kuò)展,這意味著更好的跨角點(diǎn)延時追蹤。在圖5中,微捷碼自帶CTS結(jié)果顯示了超過150ps的較高擴(kuò)展。

圖4使用新時鐘設(shè)計(jì)方法的插入延時擴(kuò)展

圖5使用微捷碼自帶CTS的插入延時擴(kuò)展

同級延時擴(kuò)展

同級延時分布是可用以*估設(shè)計(jì)期間時鐘樹魯棒性的第三個指標(biāo)。它是通過以下程序進(jìn)行計(jì)算:

1)對于每個接收端,讓Di,corner 作為插入延時,讓Li 作為時鐘樹深度。

2) 每個接收端平均級延時為

Si,corner=Di,corner/Li

級被定義為一個緩沖器和其驅(qū)動的互連線。

3) 計(jì)算所有“平均級延時”的全局平均值,

ESDcorner= ∑iSi,corner/N

4) 計(jì)算同級延時,

ESi,corner=Di,corner/ESDcorner

5) 理想上,每個接收端應(yīng)可跨角點(diǎn)地?fù)碛型鹊募墧?shù),例如,對于接收端j,

ESj,corner1=ESj,corner2=…

圖6和圖7所展示的例子是相同級數(shù)以及兩種實(shí)現(xiàn)方式的擴(kuò)展。在圖6中,ESD擴(kuò)展擁有從18到23的一種更好分布。在圖7中,微捷碼自帶CTS結(jié)果顯示了從27到37的一種分布。

圖6使用新時鐘設(shè)計(jì)方法的 ESD擴(kuò)展

圖7使用微捷碼自帶CTS的ESD擴(kuò)展

新時鐘設(shè)計(jì)方法已經(jīng)實(shí)施于40納米DSP核心。事實(shí)證明,使用這種方法的CTS單元門數(shù)要比使用微捷碼自帶CTS工具的少了17%。魯棒性低偏斜時鐘樹分布現(xiàn)已成功實(shí)現(xiàn)。實(shí)驗(yàn)結(jié)果顯示,新設(shè)計(jì)方法在降低保持緩沖器門數(shù)方面可起到很好效果。同時這種設(shè)計(jì)方法還可用于H-tree時鐘結(jié)構(gòu)。未來工作中,我們還將部署更多分析來改善功耗。

-

dsp

+關(guān)注

關(guān)注

555文章

8138瀏覽量

354979 -

時鐘

+關(guān)注

關(guān)注

11文章

1875瀏覽量

132798 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2031瀏覽量

61839

發(fā)布評論請先 登錄

ADC08500 ADC最高采樣率是500MHZ,請問差分時鐘管腳CLK+/CLK-輸入時鐘是否可以大于500MHZ?

請問ADC08500差分輸入時鐘可以大于500MHZ嗎 ?

為什么ADS5402的采樣頻率與輸入時鐘頻率范圍不一樣?

用于儀表的500MHz時鐘合成器評估板AD9911 PCB

請問有什么辦法可以使Spartan 6 PLL 500MHz時鐘供內(nèi)部使用?

用于SY89533L 33至500MHz高速時鐘合成器的評估板

用于SY89532L 33至500MHz高速時鐘合成器的評估板

如何讀取源同步DDR數(shù)據(jù)與500MHz時鐘?

EL5462 pdf datasheet (500MHz L

EL5462 pdf datasheet (500MHz L

DC696A LT5546EUF | 具有VGA和I/Q解調(diào)器和寬基帶帶寬的500MHz IF接收器

實(shí)現(xiàn)40納米DSP核心500MHz的頻率時鐘設(shè)計(jì)

實(shí)現(xiàn)40納米DSP核心500MHz的頻率時鐘設(shè)計(jì)

評論