圖像邊緣檢測是圖像處理的一項基本技術(shù),在工業(yè)、醫(yī)學、航天和軍事等領(lǐng)域有著廣泛的應(yīng)用。圖像處理的速度一直是一個難題。雖然DSP具備指令流水線特性和很高的處理速度,但其速度仍然很受限制,而利用高速可編程邏輯器件FPGA/CPLD來設(shè)計圖像邊緣檢測器可以很好的克服這個問題,是一種全新的解決方案。

1 圖像邊緣檢測算法

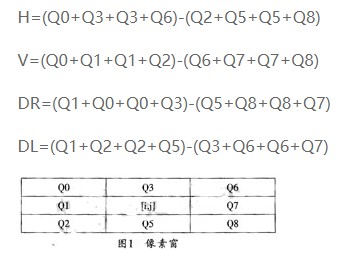

用于圖像邊緣檢測的算法很多,諸如Rorberts算子、Sobel算子、Prewitt算子、Laplaceian算子等,由于Sobel算法只涉及到加法操作,并且可以取得很好的效果,所以是最常用的邊緣檢測算法。由于圖像在邊緣附近會出現(xiàn)灰度上的突變,所以,Sobel邊緣檢測方法以原始圖像灰度為基礎(chǔ),并通過考察圖像每個像素在某個領(lǐng)域內(nèi)灰度的變化,然后利用邊緣鄰近的一階導數(shù)最大值來檢測邊緣,再設(shè)置權(quán)重來檢測水平、垂直、左對角、右對角等各個不同方向上密度幅度的不同來實現(xiàn)邊沿檢測。圖1所示是一個3×3像素的舉例,其水平、垂直、左對角和右對角圖像上密度幅度的變化可以表示為:

其中,H、V、DL、DR用于計算梯度的大小和方向,而梯度的大小可由正式給出一個普遍的估計值:

Magnitude=Max(H,V,DR,DL)

這樣,通過對圖像灰度作直方圖分析,便可以給出區(qū)分度閥值,如果Magnitude大于這個閥值,則該像素為邊界像素,否則為一般像素。

2 系統(tǒng)設(shè)計

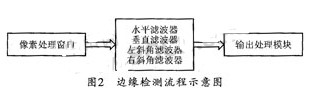

該邊緣檢測器以ALTERA公司的FLEX10K20芯片為核心器件。由圖像傳感器獲取的圖像經(jīng)前端處理器處理即可得到3×3像素圖形數(shù)據(jù),然后送入各個濾波器進行濾波,最后將有關(guān)結(jié)果送輸出處理模塊處理后輸出。

邊緣檢測的關(guān)鍵是求出四個方向的圖像梯度數(shù)據(jù)絕對值的最大值,同時判別最大值出現(xiàn)的方向,其內(nèi)部結(jié)構(gòu)如圖3所示,邊緣檢測的核心部分包括濾波器FILTER、比較器COMPARE、邊界判斷器JUDGE和寄存器等。

2.1 濾波器的設(shè)計

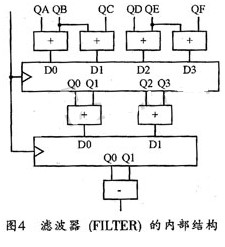

濾波器(FILTER)的設(shè)計可采用兩級并行流水線方案,其內(nèi)部結(jié)構(gòu)如圖4所示。圖中的QA、QB、QC、QD、QE、QF對應(yīng)接上Q0、Q3、Q6、Q2、Q5、Q8表示水平方向濾波,其輸出則為H_FILTER。垂直方向濾波器、左對角濾波器和右對角濾波與水平方向濾波器類似。為了提高加法運算的速度,加法器的設(shè)計可選用超前進位加法器。

2.2 比較器的設(shè)計

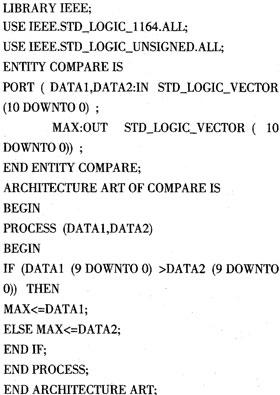

比較器模塊的功能是比較兩個輸入值以得到其最大值。其VHDL源程序如下:

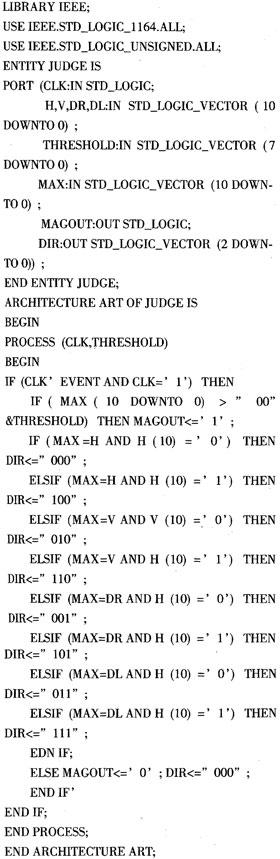

2.3 邊界判斷器的設(shè)計

邊界判斷器JUDGE的功能是根據(jù)區(qū)分度閥值、四個濾波器的輸出及其最大值進行邊界的判斷。其VHDL源程序如下:

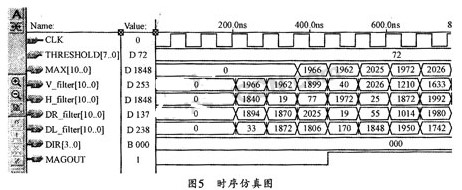

3 仿真分析

事實上,對于圖像邊緣檢測中的sobel算法來說,若使用FPGA來設(shè)計,則H、V、DR、DL四個方向的濾波可以全部并行。另外,由于每個方向的濾波器設(shè)計時均采用一級四路并行加法器與一級雙路并行加法器相串聯(lián),因此,算上兩級串行比較器。實際上,整個過程只有四級串行結(jié)構(gòu)。

4 結(jié)束語

對于本文所設(shè)計的系統(tǒng),假設(shè)使用40 MHz的系統(tǒng)時鐘,則處理一個像素點的時間約100 ns,也就是說,處理一張800×600的圖像所用的時間不到50 ms。由此可見,該設(shè)計可大大提高圖像邊沿檢測的處理速度。

-

dsp

+關(guān)注

關(guān)注

555文章

8141瀏覽量

355124 -

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613939 -

cpld

+關(guān)注

關(guān)注

32文章

1257瀏覽量

170969

發(fā)布評論請先 登錄

可編程邏輯器件

可編程邏輯器件發(fā)展歷史

PLD可編程邏輯器件

可編程邏輯器件基礎(chǔ)及應(yīng)用實驗指導書

什么是PLD(可編程邏輯器件)

基于可編程邏輯器件的數(shù)字電路設(shè)計

EDA技術(shù)與應(yīng)用(可編程邏輯器件)

可編程邏輯器件FPGA/CPLD結(jié)構(gòu)與應(yīng)用

電可編程邏輯器件EPLD是如何設(shè)計的

可編程邏輯器件測試

利用高速可編程邏輯器件的圖像邊緣檢測器的解決方案

利用高速可編程邏輯器件的圖像邊緣檢測器的解決方案

評論