隨著數字化與測井技術的發展,對測井系統的穩定性、可靠性、兼容性、可升級性等性能提出了更高的要求,本文提出了一種適用于測井系統設備的CPCI(Compact PCI)高性能數據采集板卡硬件設計方案,能夠有效地處理來自井下的復雜信號,并通過256 MB/s 高速CPCI總線橋接到主控設備。

本板卡實現的主要功能是井下Encoder(深度脈沖)、Tension(張力)、MMD(Magnetic Mark Detection)和CCL(Casing Collar Locator)等信號的實時采集,采集數據在DSP中完成預處理,通過CPCI總線送入主控制器分析使用,此外,板卡還實現上電自診斷,關鍵數據在FRAM中的及時存儲,RS232 串口定時發送深度數據和接收控制命令等其他功能。

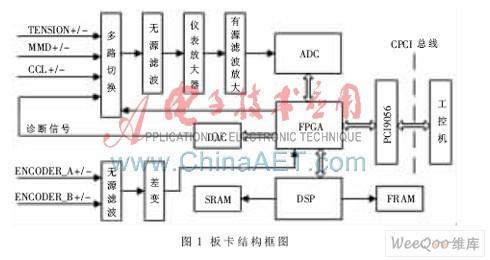

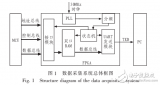

1 板卡總體結構

整個板卡由FPGA、PCI橋片、DSP、A/D和D/A五大部分組成,其中FPGA選用Altera公司高性能低功耗Cyclone III系列芯片,PCI橋片選用PLX公司32 bit 66 MHz PCI9056芯片,DSP選用TI公司TMS320F2812芯片,A/D選用ADI公司16 bit 200 kS/s高精度高速采集芯片AD974,板卡結構框圖如圖1所示。該板卡工作過程是:板卡上電后,PCI9056向FPGA發出指令控制D/A產生診斷信號,診斷信號經由板卡各級模擬通路后環回到FPGA,然后FPGA把采集到的診斷信號送入DSP,DSP再通過FPGA把數據送回CPCI總線,完成整個板卡硬件的自診斷。自診斷完成后,D/A處于非工作狀態,各信號由井下電纜送入,經過多級濾波放大后進行A/D采集,FPGA完成Tension、MMD和CCL等信號的采集和Encoder信號的處理,最終把數據送入DSP進行預處理,經DSP處理好的數據由CPCI總線送回主控制器。

2 板卡硬件設計

2.1 FPGA控制器的總體設計

本板卡的數字系統共有2個主控制器,分別為數據采集板卡上的DSP和CPCI總線上的CPU主控機,板卡使用PCI9056橋片實現CPCI總線與局部總線間的轉化, DSP與CPCI總線通過中斷方式實現數據交換。其中FPGA調用QUARTUS軟件自帶IP核實現32 KB雙口RAM,并把雙口RAM分成大小相等的兩部分,一部分用于CPCI總線向DSP傳輸數據,另一部分用于DSP向CPCI總線傳輸數據,避免了總裁的使用和數據的丟失。FPGA作為數據采集板卡數據中轉站的同時,主要實現A/D數據的采集,Encoder脈沖信號的去抖動處理、計數和相位判斷。FPGA實現功能框圖如圖2所示。

2.2 A/D數據采集模塊設計

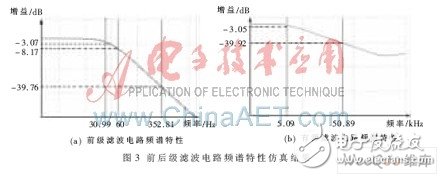

Tension、MMD和CCL等信號均是來自井下的低頻微弱小信號,并且由于井下環境復雜,信號容易被干擾,處理不當容易造成數據失效,所以本板卡對三種信號在模擬電路上做了多級濾波放大處理。經實際環境測試,三路信號的主要輸入干擾集中在60 Hz以上,因此在輸入端設計40 Hz、70 Hz和120 Hz三階RC濾波電路做前級濾波處理,使濾波器具有窄的過渡帶,有效的濾除60 Hz以上的干擾信號,避免干擾信號進一步放大無法濾除,圖3(a)為前級濾波電路的頻譜特性仿真結果。為了便于信號的采集,需設計運放電路將信號放大至A/D量程范圍,這就不可避免會引入PCB、運放等造成的中高頻噪聲,所以在信號進入A/D前做了進一步有源濾波處理,圖3(b)為有源濾波器的頻譜特性仿真結果。實際測試結果也證明經過多級濾波,電路抗干擾能力明顯增強。

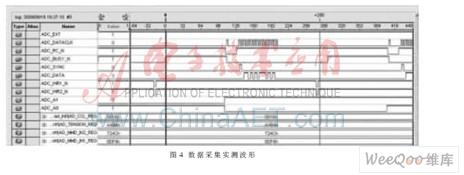

本設計選用了高速高精度ADC AD974芯片,在4個通道間以輪詢方式進行采樣,每個通道的實際采樣轉換率為50 kS/s,在FPGA中設置一個數據更新寄存器,進行每一次數據采集完成的實時跟蹤。此種工作方式是否能可靠穩定地采集數據關鍵有兩點,一是外部時鐘頻率是否適中,本設計采用12 MHz的頻率,二是要保證A/D內部的采樣時間(Acquisition Time)不能小于1 μs,并且4個通道在輪詢切換時,地址鎖存信號WR1和WR2要在采樣前一個周期設置完成。

AD974在板卡上電后用Quartus II SignalTap實時觀測的時序如圖4所示。其中ADC_A0和ADC_A1為A/D4個通道地址編碼信號,ADC_WR0_N和ADC_WR1_N為地址鎖存信號,低電平有效,當前鎖存地址作為下一次采集通道有效地址。當ADC_RC_N信號置為低電平時A/D開始將采集到的模擬信號向數字信號轉換,并在此時送出一個時鐘周期的ADC_DATACLK信號,使能A/D同步信號,此時如果A/D空閑則ADC_BUSY_N信號自動拉低,表示A/D已經開始轉換數據,隨后將ADC_RC_N置高并送出采樣時鐘信號,便可在ADC_DATA上開始讀前一次轉換完成的數據。當本次A/D數據轉換完成后ADC_BUSY_N信號將自動置高,表明A/D本次轉換完成,進入下一次模擬信號采樣。

2.3 Encoder信號處理模塊設計

Encoder信號在實際設備上分為兩路信號,分別為A信號和B信號,當井下設備上提時A信號相位超前B信號90°,當井下設備下放時A信號相位滯后B信號90°,脈沖信號的數量體現測井設備在井下的深度,此信號是測井系統的重要信號之一,如果測量不準, 可能會導致測井資料作廢, 甚至帶來生產事故。實測Encoder信號從井下設備傳送到地面時,會有尖峰脈沖干擾引入,所以本板卡在硬件上采用RC無源濾波器去除信號的尖峰脈沖,通過FPGA在軟件上對信號進行去抖動處理、計數和相位判斷,能夠準確計數并與系統時鐘同步。

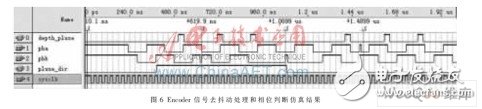

FPGA中對Encoder脈沖信號的去抖動處理和相位判斷設計電路見圖5,其中depth_pluse為去抖動后的脈沖信號,結合depth_dir完成脈沖計數,當depth_dir為正時,計數脈沖自加,depth_dir為負時,脈沖計數自減。本文用QUARTUS軟件自帶仿真工具對Encoder信號做的仿真波形,見圖6,如波形所示,在時間節點619.9 ns、1.069 9 μs和1.489 9 ?μs處分別對A信號和B信號加入了干擾脈沖,但結果表明本設計可以對干擾脈沖完全濾除。

本文給出了一種高性能測井數據采集板卡的設計方法,板卡在設計中,模擬部分采用多級濾波、高精度A/D,使得數據采集穩定可靠,Encoder深度脈沖信號在硬件濾波的基礎上做了軟件優化處理,明顯增強了抗干擾能力,數字部分采用FPGA和DSP相結合,使板卡具有很高的靈活性、可靠性和可升級性。經大量測試,板卡運行穩定,并在實際系統中得到應用。

-

FPGA

+關注

關注

1643文章

21954瀏覽量

613939 -

芯片

+關注

關注

459文章

52145瀏覽量

435925 -

數據采集

+關注

關注

40文章

6929瀏覽量

115665 -

總線

+關注

關注

10文章

2947瀏覽量

89331 -

CPCI

+關注

關注

7文章

72瀏覽量

33284

發布評論請先 登錄

基于PCI總線的微弱信號采集模塊的設計方案

數據采集卡/分布式采集模塊/無線通訊采集模塊/嵌入式系統

基于FPGA的數據采集控制器IP核的設計方案和實現方法研究

基于FPGA的高速數據采集系統該怎么設計?

基于ARM和FPGA的微加速度計數據采集設計方案

一種測井數據采集系統設計

DSP+FPGA實現測井數據采集系統

CPCI數據總線接口的設計與實現

基于CPCI總線與FPGA芯片的測井數據采集智能IO板卡設計方案

基于CPCI總線與FPGA芯片的測井數據采集智能IO板卡設計方案

評論