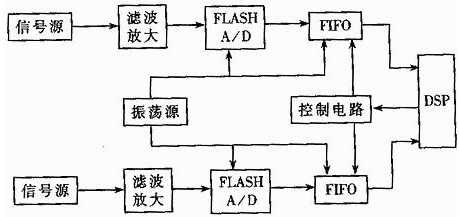

在高速數據采集系統中,若A/D轉換器直接與微處理器MCU相接,則因高速A/D的轉換速率較高,迫使MCU不斷地讀取轉換結果,因而就占用了MCU大部分的I/O帶寬,降低了MCU的工作效率。在此情況下通常都會加緩存器,這樣“模/數轉換器緩存器一處理器”就成為一種通用模式。下面就介紹如何利用FIFO芯片CY7C4255V實現高速高精度模/數轉換器AD767l與LPC2200系列ARM處理器的接口。

1 、器件簡介

1.1 模/數轉換器AD7671

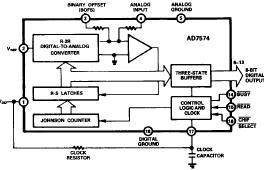

AD767l是采樣速率達1Msps的16位逐次逼近型高速高精度模/數轉換器,采用5V單電源供電,并能提供單極性和雙極性兩種輸入方式,可適用不同的輸入范圍;它還提供校準與誤差校正電路、內部時鐘、8位或16位并行口和1個串行口。AD7671能夠達到16位分辨率,而且無失碼,最大積分非線性誤差(INL)僅為2.5 LSB,能夠滿足各種高精度應用的要求。

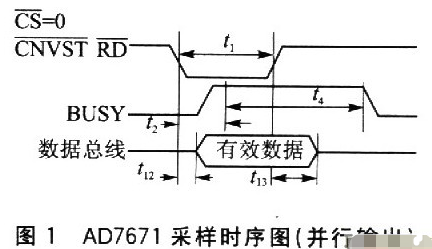

通常情況下,AD7671有兩種數據讀取方式:一種是在數據轉換完成后,讀取轉換的數據;另一種是在數據轉換的過程中,讀取上一次轉換完成的數據。圖l中的時序圖描述了后一種情況,即主控制器發出CNVST信號后,檢測BUSY信號。當BUSY信號置為高電平時,讀取由上一個轉換過程所轉換的數據。

1.2 FIFO芯片CY7C4255V

FIFO(First In First Out)簡單說就是指先進先出。作為一種新型大規模集成電路,FIFO芯片以其靈活、方便、高效的特性,逐漸在高速數據采集、高速數據處理、高速數據傳輸以及多機處理系統中得到越來越廣泛的應用。CY7C455V是Cypress公司的3.3V高速,低功耗的FIFO,芯片容量為8K18位,最高工作速率為100MHz(最短讀/寫時間為10ns),輸入/輸出端口由單獨的時鐘和使能信號控制,具有“空”、“滿”、“半滿”和可編程的“幾乎空”、“幾乎滿”標志。

CY7C4255的18位輸入/輸出端口由單獨的時鐘和使能信號控制。輸入端口由一連續寫時鐘(WCLK)和寫使能信號(WEN)控制,當寫使能WEN有效時,數據在每個時鐘周期WCLK信號的上升沿被連續寫入FIFO存儲器中。同樣,輸出端口由一連續讀時鐘(RCLK)和讀使能信號(REN)控制,而且有一個輸出使能引腳(OE)。如果是單時鐘操作,則讀/寫時鐘可連接在一起;在異步讀/寫應用中,兩個時鐘可以是獨立的,時鐘頻率最高可達100 MHz。利用芯片提供的級聯輸入(WXI、RXI)、級聯輸出(WXO、RXO)和首先加載(FL)引腳可進行深度擴展。

1.3 ARM處理器LPC2210

LPC2210是基于一個支持實時仿真和嵌入式跟蹤的16/32位144腳ARM7TDMI-S核的微控制器。它內部包含ARM7TDMI-S核與片內存儲器控制器接口的ARM7局部總線、與中斷控制器接口的AMBA高性能總線(AHB)和連接片內外設功能的VLSI外設總線(VPBARM AMBA總線的兼容超集)。LPC2210具有16KB片內靜態RAM;片內外設與器件引腳的連接由引腳連接模塊控制,該模塊由軟件進行控制以符合外設功能與引腳在特定應用中的需求;通過外部存儲器接口可將存儲器配置成4組,每組的容量高達16MB,數據寬度為8/16/32位;具有2個32位定時器(帶4路捕獲和4路比較通道)、PWM單元(6路輸出)、實時時鐘和看門狗;多個串行接口包括2個16C550工業標準UART、高速I2C接口(400kb/s)和2個SPI接口;多達76個通用I/O口(可承受5V電壓),12個獨立外部中斷引腳EIN和CAP功能。

2 、接口電路

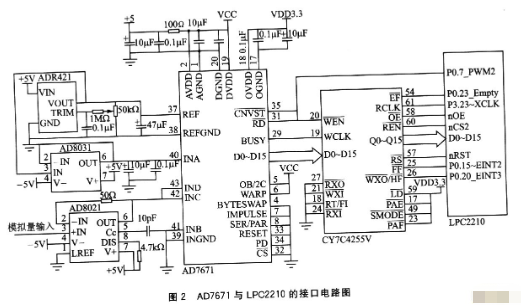

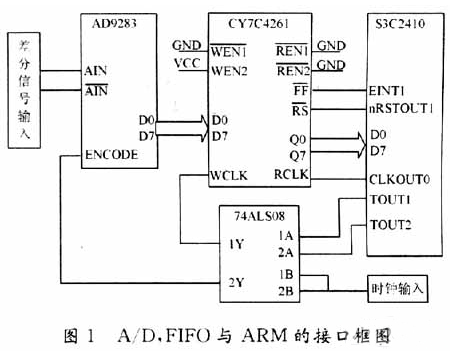

利用FIFO芯片CY7C4255V實現AD7671與LPC2210的接口電路,如圖2所示。圖中,AD7671的輸入范圍已經配置成士5V,其數據端口采用高速并行接口;接口的數據讀取模式設置為圖l所示的模式,其中+5V和一5V分別是模擬電壓。由于CY7C11255V與LPC2210的數據接口的電壓為3.3V,所以將3.3V數字電壓輸入到OVDD引腳,這樣AD7671的數據接口電壓就可以與FIFO芯片的數據接口相兼容。ADR421為AD7671提供了+2.5V的基準電壓;AD7671的模擬輸入端,采用了由低噪聲系數的激勵放大器ADS02l構成的驅動電路來驅動A137671。

A/D轉換結果輸出直接與FIFO數據輸入端D0~D15相連}轉換控制由ARM處理器的一個PWM輸出端產生所需的采樣頻率的采樣控制信號,該信號同時作為 FIFO的輸入使能端的控制。AD767l的BUSY輸出端作為FIFO的輸入時鐘(WCLK)控制信號,當轉換結束時 BUSY(WCLK)由低變高,此時FIFO寫使能WEN有效,轉換數據就在WCLK(BUSY)信號的上升沿被寫入FIFO 存儲器中。LPC2210 ARM處理器總線數據寬度配置為 16位,由EMC總線的片選信號nCS2、輸出使能信號 nOE、時鐘輸出XCLK來控制FIFO的數據讀取。FIFO 的半滿(HF)、全滿(FF)標志與ARM的2個中斷引腳相連,可通過編程在實際應用中選擇使用;EF接ARM的 PO.23引腳作為FIFO的空查詢引腳。

3、結語

采用FIFO器件作為高速A/D與ARM處理器間的數據緩沖,具有電路結構簡單、性能可靠等優點;同時提高了處理器的工作效率,使控制更加方便。

責任編輯:gt

-

處理器

+關注

關注

68文章

19799瀏覽量

233463 -

芯片

+關注

關注

459文章

52145瀏覽量

435854 -

fifo

+關注

關注

3文章

400瀏覽量

44602

發布評論請先 登錄

基于FIFO存儲器實現AD轉換器與ARM的接口設計

多通道模/數轉換器AD7890與DSP的接口設計

采用I2C總線的ADS1100型16位模/數轉換器的設計

高速模數轉換器與TMS320C6000DSP接口的FIFO實現

基于12位模/數轉換器與FIFO芯片的數據采集處理系統

基于FIFO存儲器實現高速AD轉換器與ARM處理器的接口設計

通過采用FIFO芯片實現模/數轉換器和ARM處理器的接口設計

通過采用FIFO芯片實現模/數轉換器和ARM處理器的接口設計

評論