引 言

微機(jī)保護(hù)裝置是指微機(jī)系統(tǒng)構(gòu)成的數(shù)字式繼電保護(hù)裝置。在我國煤礦井下高壓(6kV)供電系統(tǒng)中,絕大多數(shù)屬于變壓器中性點(diǎn)絕緣運(yùn)行方式(三相三線制),通過動力電纜送電。煤礦井下環(huán)境惡劣,空間狹窄,動力電纜長期處在潮濕、淋水、腐蝕的環(huán)境中,散熱條件差,絕緣性能易下降,經(jīng)常發(fā)生單相漏電或單相接地故障。這種故障引起正常相電壓升高,若不及時斷電,會造成多相短路,迫使供電中斷,并使電力故障進(jìn)一步擴(kuò)大。高壓防爆開關(guān)微機(jī)保護(hù)裝置是安裝在高壓防爆開關(guān)中,對井下電纜和用電設(shè)備的單相漏電或單相接地、短路、過流、絕緣監(jiān)視、過欠壓等故障進(jìn)行綜合保護(hù)的一種裝置,能快速切除故障回路,防止事故擴(kuò)大,通知維護(hù)人員及時排查故障源并排除。因此,對高壓防爆開關(guān)微機(jī)保護(hù)裝置提出很高的可靠性要求: 在故障發(fā)生時能快速動作;在未故障時,不能誤動。然而,高壓開關(guān)通斷感性負(fù)載(井下電器設(shè)備主要是電動機(jī)等感性負(fù)載)時刻,開關(guān)觸點(diǎn)拉弧會產(chǎn)生很強(qiáng)的電磁干擾和浪涌干擾,嚴(yán)重程度可造成CPU的程序跑飛。這種電磁干擾是高壓防爆開關(guān)微機(jī)保護(hù)系統(tǒng)的頭號強(qiáng)干擾源,主要通過電源線和交流互感器摸入通道侵入微機(jī)保護(hù)系統(tǒng)。微機(jī)保護(hù)系統(tǒng)長期工作在這種強(qiáng)電磁干擾中,抗干擾性能成為衡量微機(jī)保護(hù)系統(tǒng)的重要指標(biāo)之一。

提高微機(jī)保護(hù)裝置的抗干擾性能的根本途徑是阻塞共模干擾的耦合通道,提高敏感回路的抗干擾能力,合理設(shè)計(jì)接地泄放回路等措施。電磁兼容性(EMC)設(shè)計(jì)是一個復(fù)雜的系統(tǒng)工程,從硬件上考慮抗干擾設(shè)計(jì)是非常必要的,但想從硬件上完全消除干擾是不可能的。還要從軟件上考慮數(shù)字濾波等,很難做到盡善盡美。國內(nèi)科技人員在單片機(jī)系統(tǒng)、微機(jī)測控系統(tǒng)的抗干擾技術(shù)等方面做了很多研究工作,發(fā)表大量的抗干擾技術(shù)論文,可分為兩大類。一類是從硬件電路阻塞干擾信號的入侵通道,如模擬通道加前置濾波器、電源輸入加電源濾波器、開關(guān)入與出加光耦隔離、pCB布局和布線的抗干擾技術(shù)、接地技術(shù)和屏蔽技術(shù)等等;另一類是軟件抗干擾措施,包括數(shù)字濾波、指令冗余、軟件陷阱、軟硬件看門狗等。硬件措施抗干擾是拒干擾信號于門外,是電磁兼容性設(shè)計(jì)的主攻方向。軟件抗干擾是在硬件尚未失效前提下,利用軟件的靈活性設(shè)計(jì)來抵消干擾的影響,只能起到輔助的抗干擾作用。關(guān)于微機(jī)保護(hù)裝置的控制出口可靠性設(shè)計(jì)的文獻(xiàn)很少,歸納起來,防止控制出口失控的常用措施有兩種: 硬件冗余設(shè)計(jì)和軟件冗余設(shè)計(jì)。硬件冗余設(shè)計(jì)基本方法是采用雙或多CPU結(jié)構(gòu),一個負(fù)責(zé)保護(hù)的啟動,另一個CPU負(fù)責(zé)保護(hù)的執(zhí)行。兩個CPU相“與”才開始控制出口。軟件冗余設(shè)計(jì)主要采用以下措施:

(1)設(shè)置多重跳閘命令,分多條控制指令來執(zhí)行分閘,在每條指令之間執(zhí)行一段核對程序,設(shè)置相應(yīng)的標(biāo)志位。CPU核對標(biāo)志位相符后才執(zhí)行下一條指令,否則初始化重來。

(2)設(shè)置當(dāng)前輸出狀態(tài)寄存器的狀態(tài)信息,系統(tǒng)運(yùn)行自檢程序循環(huán)查詢測試這些狀態(tài),若發(fā)現(xiàn)干擾出錯,及時糾正輸出通道的出錯信息。

多CPU結(jié)構(gòu)設(shè)計(jì)是防止保護(hù)誤動,提高微機(jī)保護(hù)系統(tǒng)可靠性的一種有效措施,但采用多CPU結(jié)構(gòu)使硬件結(jié)構(gòu)復(fù)雜,調(diào)試繁瑣,成本高,而且當(dāng)多CPU同時程序跑飛時,同樣造成控制出口失控,有可能引起誤動。軟件冗余設(shè)計(jì)是在程序運(yùn)行正常情況下提出的(即假設(shè)CPU運(yùn)行程序正確,沒有出軌),如果程序跑飛,已經(jīng)執(zhí)行不到軟件冗余設(shè)計(jì)程序,則控制出口處于失控狀態(tài),既使看門狗電路起作用,使CPU復(fù)位重新回到正常程序,經(jīng)歷的時間最短也要幾毫秒。在這段時間內(nèi),干擾信號足以引起控制出口的誤跳閘。顯然,上述兩種方法并不能完全確保繼電保護(hù)控制出口的可靠性和安全性。

對微機(jī)保護(hù)系統(tǒng)來說,最重要的一點(diǎn)就是當(dāng)強(qiáng)干擾引起程序跑飛后,不能引起繼電保護(hù)控制出口的誤動作。筆者在研制KJ118型礦用變電所遠(yuǎn)程監(jiān)控系統(tǒng)配套的高壓防爆開關(guān)微機(jī)保護(hù)系統(tǒng)中,針對繼電保護(hù)控制出口的特點(diǎn),創(chuàng)造性地提出采用CPLD技術(shù),加強(qiáng)微機(jī)保護(hù)控制出口的可靠性研究,成功設(shè)計(jì)出一種基于CPLD的抗干擾微機(jī)保護(hù)控制出口硬件電路。文中介紹的這種基于CPLD控制接口抗干擾設(shè)計(jì)的新方法,比多CPU結(jié)構(gòu)更簡單,更經(jīng)濟(jì),可靠性更高,不依賴于CPU本身的抗干擾性能,即使CPU程序跑飛,控制接口仍有很高抗干擾性能,不會產(chǎn)生誤跳閘電平,徹底解決繼電保護(hù)系統(tǒng)控制出口的可靠性問題。

CPLD技術(shù)在微機(jī)保護(hù)裝置中應(yīng)用的優(yōu)越性

CPLD(complex programmable logic device,復(fù)雜可編程邏輯器件)與FPGA(field programmable gate array,現(xiàn)場可編程門陣列)是兩大可編程ASIC(application specific intergrate dcircuit)芯片,都可用VHDL(very high speed intergrate dcircuit hardware description language)進(jìn)行描述和編程下載。CPLD門陣列規(guī)模較FPGA小,CPLD主要結(jié)構(gòu)是基于乘積項(xiàng),易于實(shí)現(xiàn)較復(fù)雜的組合邏輯。CPLD的邏輯宏單元較FPGA少,較多的觸發(fā)器時序邏輯用FPGA較合適。FPGA主要結(jié)構(gòu)是基于SRAM的查表項(xiàng),雖然電路結(jié)構(gòu)配置靈活,但延時不可預(yù)測,實(shí)際傳輸延時要大于CPLD。CPLD采用EEpROM編程技術(shù),掉電配置信息不丟失。FPGA采用SRAM工藝開關(guān)技術(shù),上電通過在線可重配置方式對FPGA進(jìn)行功能配置,理論上可無限次配置,并可實(shí)現(xiàn)真正意義上的在線可配置,但掉電配置信息丟失,必須借助串行EEpROM、單片機(jī)等進(jìn)行上電的重配置。對于I/O數(shù)量和觸發(fā)器數(shù)目不太大的應(yīng)用場合,CPLD在使用方便性和編程的保密性均優(yōu)于FPGA。

微機(jī)保護(hù)系統(tǒng)中的數(shù)字組合邏輯電路和時序邏輯電路規(guī)模均不大,宜采用CPLD芯片實(shí)現(xiàn),有利于微機(jī)保護(hù)系統(tǒng)的微型化和智能化設(shè)計(jì)。

微機(jī)保護(hù)裝置控制接口設(shè)計(jì)

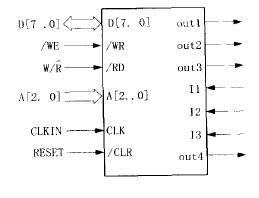

微機(jī)保護(hù)系統(tǒng)的控制接口由I/O接口和微型繼電器組成,典型電路是將分合閘繼電器分成2級,第1級控制第2級。第2級控制主回路的分合閘接觸器。原理框圖如圖1所示。

2級繼電器有利于隔離主回路的分合閘接觸器通斷產(chǎn)生的干擾。

合閘指令執(zhí)行順序?yàn)椋篛UT1→OUT2→OUT4。分閘指令執(zhí)行順序?yàn)椋篛UT1→OUT3→OUT4。如果I/O接口直接由CPU控制,當(dāng)CPU受干擾程序跑飛或CPU芯片出故障使I/O接口失控,正巧產(chǎn)生分合閘所需的電平時,繼電保護(hù)控制出口就不可避免地發(fā)生誤動。

圖1繼電保護(hù)控制出口原理

因此,繼電保護(hù)控制出口的閉鎖和冗余度設(shè)計(jì)是防止控制出口誤動的關(guān)鍵所在。嚴(yán)格監(jiān)視分合閘多重命令的執(zhí)行順序,不允許無序分合閘命令通過,是防止控制出口誤動的根本措施。分合閘多重命令的有序執(zhí)行,可以看作一個狀態(tài)變化序列,用CPLD狀態(tài)機(jī)對這個狀態(tài)序列進(jìn)行監(jiān)控,就能杜絕無序狀態(tài)的通過,實(shí)現(xiàn)控制出口的無干擾控制。

基于CPLD狀態(tài)機(jī)的抗干擾控制接口設(shè)計(jì)

設(shè)計(jì)一個基于DSP的高壓開關(guān)柜微機(jī)綜合保護(hù)系統(tǒng)時,用一片CPLD芯片實(shí)現(xiàn)圖1所示的I/O接口,并設(shè)計(jì)一個有限狀態(tài)機(jī),對狀態(tài)輸入I1,I2,I3進(jìn)行監(jiān)控,狀態(tài)機(jī)輸出作為總分合閘命令的允許和禁止信號。基于CPLD的微機(jī)保護(hù)控制接口如圖2 所示。

圖2微機(jī)保護(hù)的CPLD控制接口

分合閘多重命令的狀態(tài)編碼

狀態(tài)機(jī)有3位二進(jìn)制輸入,共有23=8種狀態(tài)。采用二進(jìn)制編碼方式(Binary coded)將控制接口的初始狀態(tài)S0到所有可能的狀態(tài)變遷,列成一張編碼表,如表1 所示。狀態(tài)編碼表是編寫VHDL程序的基礎(chǔ)。

表1微機(jī)保護(hù)控制接口狀態(tài)機(jī)編碼表

狀態(tài)機(jī)設(shè)計(jì)

狀態(tài)機(jī)的時鐘頻率為5MHz。復(fù)位信號/Reset來自DSP微機(jī)保護(hù)裝置的系統(tǒng)復(fù)位信號,對狀態(tài)機(jī)的狀態(tài)初始化。

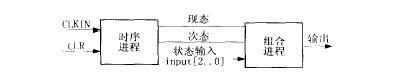

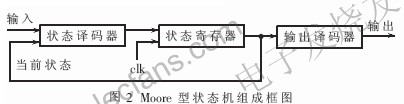

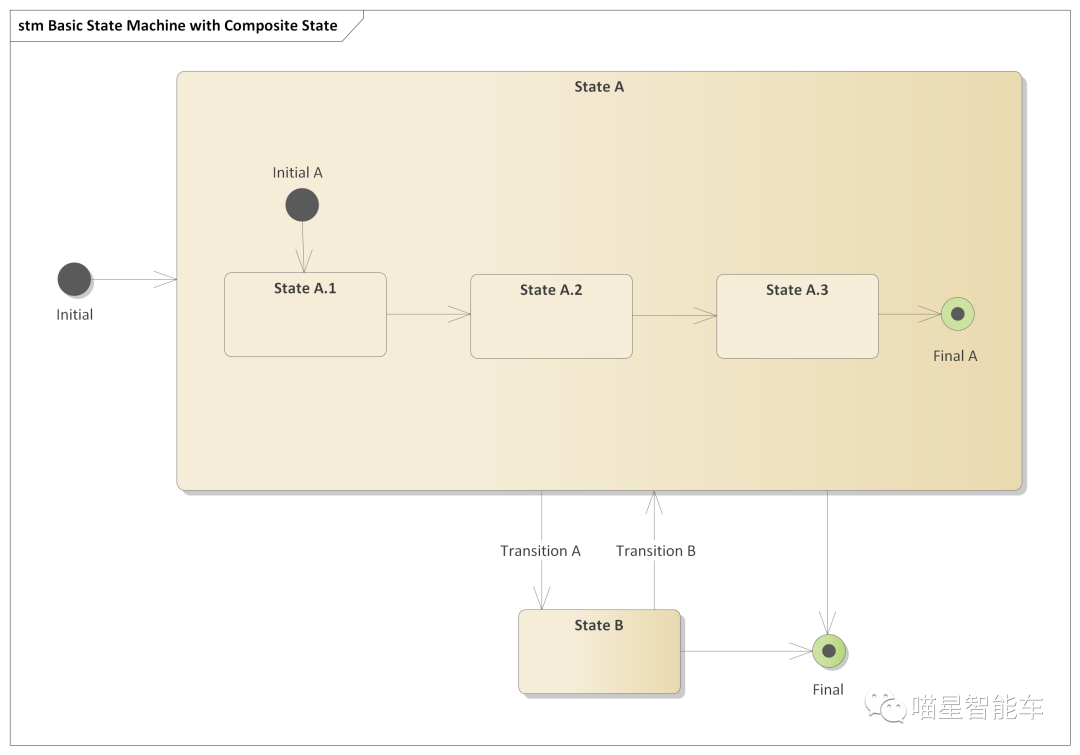

狀態(tài)機(jī)的設(shè)計(jì)可采用單進(jìn)程,雙進(jìn)程,3進(jìn)程等進(jìn)行編寫,根據(jù)微機(jī)保護(hù)控制接口的應(yīng)用特點(diǎn)宜采用雙進(jìn)程來描述狀態(tài)機(jī),即一個時序進(jìn)程和一個組合進(jìn)程。時序進(jìn)程負(fù)責(zé)舊次態(tài)到新現(xiàn)態(tài)的轉(zhuǎn)換,以及異步復(fù)位。組合進(jìn)程完成根據(jù)現(xiàn)態(tài)決定狀態(tài)機(jī)輸出的變化,根據(jù)狀態(tài)輸入來決定新的次態(tài)。雙進(jìn)程狀態(tài)機(jī)的邏輯框圖如圖3所示。

圖3雙進(jìn)程狀態(tài)機(jī)邏輯圖

狀態(tài)機(jī)的行為及代碼是一種流程控制代碼,很容易用VHDL語言中的CASE語句和IF語句加以實(shí)現(xiàn)。時序進(jìn)程與組合進(jìn)程之間利用現(xiàn)態(tài)信號和次態(tài)信號進(jìn)行同步通信。

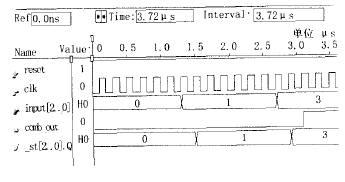

狀態(tài)機(jī)仿真波形

利用Altera公司的EDA工具軟件MAX+plus對用VHDL語言設(shè)計(jì)的狀態(tài)機(jī)進(jìn)行時序仿真,仿真波形如圖4所示。

圖4狀態(tài)機(jī)仿真波形

CPLD狀態(tài)機(jī)抗干擾控制原理分析

基于CPU的微機(jī)系統(tǒng)是按指令周期順序執(zhí)行機(jī)器指令的,一旦受干擾程序出軌,則CPU不按事先編好的流程執(zhí)行程序,出現(xiàn)死機(jī),通常的對策是設(shè)置看門狗使CPU硬件復(fù)位,使CPU重新運(yùn)行正常程序,但是從CPU死機(jī)到看門狗復(fù)位一般要經(jīng)歷幾毫秒到1~2s,這段失控時間,繼電保護(hù)控制出口的狀態(tài)是不可預(yù)測的,足以對繼電保護(hù)系統(tǒng)構(gòu)成危害,嚴(yán)重情況就是發(fā)生誤動。而基于CPLD的狀態(tài)機(jī)系統(tǒng),狀態(tài)變換周期只有一個時鐘周期,若時鐘頻率為5MHz,時鐘周期為012Ls。若狀態(tài)機(jī)受干擾進(jìn)入非法狀態(tài)再轉(zhuǎn)入合法狀態(tài),只需2個時鐘周期,即幾百納秒,不足以對狀態(tài)機(jī)系統(tǒng)運(yùn)行造成危害。可見,用CPLD狀態(tài)機(jī)控制微機(jī)繼電保護(hù)的控制接口,就能實(shí)現(xiàn)無干擾控制,獲得繼電保護(hù)系統(tǒng)的高可靠性控制。

就DSP芯片與CPLD芯片的可靠性比較而言,DSP的外圍接口繁多,輸入信號有模擬和數(shù)字,電壓有模擬電壓和數(shù)字電壓,CPLD只有數(shù)字接口,電壓單一,受外界干擾損壞的可能性比DSP小的多。另外,CPLD狀態(tài)機(jī)含有多個進(jìn)程,就相當(dāng)于包含有并行運(yùn)算的“多CPU”功能,對不合格的輸入,裁決狀態(tài)機(jī)輸出0。因此,筆者認(rèn)為,雙CPU控制硬件冗余設(shè)計(jì)遠(yuǎn)不如CPLD狀態(tài)機(jī)的控制接口可靠性高。

結(jié) 論

用Altera公司的MAX7000系列的EMp7128SLC84-15實(shí)現(xiàn)繼電保護(hù)控制接口,與TMS320F240DSP芯片總線直接相連,DSP執(zhí)行合閘或分閘多重命令時,不需要插入等待周期,只需要連續(xù)執(zhí)行3條合閘或分閘指令,CPLD狀態(tài)機(jī)就能立即決定是否允許總執(zhí)行命令通過。試驗(yàn)表明: 用CPLD實(shí)現(xiàn)的繼電保護(hù)控制接口具有速度快,占用硬件體積小,接口簡單,可靠性高等特點(diǎn)。

該接口應(yīng)用到基于TMS320F240的高壓開關(guān)柜數(shù)字綜合保護(hù)裝置中,隨KJ118型礦用變電所遠(yuǎn)程監(jiān)控系統(tǒng)于2003年10月在徐州礦務(wù)局旗山煤礦井下采區(qū)變電所投運(yùn),進(jìn)行工業(yè)性試驗(yàn),正常運(yùn)行至今已超過半年以上。采區(qū)變電所現(xiàn)場高爆開關(guān)就地人工分合閘操作、地面主機(jī)遙控命令分合閘以及故障保護(hù)跳閘試驗(yàn)表明,從未發(fā)生因高壓開關(guān)分合閘操作等強(qiáng)電磁干擾引起CPU程序出軌而誤動,表現(xiàn)出非常高的可靠性。

文中用全新的CPLD狀態(tài)機(jī)方法研究微機(jī)保護(hù)系統(tǒng)的控制可靠性問題,對于瞬變干擾信號有很強(qiáng)的濾波性。雖然從防范微機(jī)保護(hù)系統(tǒng)程序出軌采用一些軟件措施有一定效果,但是并不能真正解決程序出軌期間控制口的失控問題,而文中提出的CPLD狀態(tài)機(jī)控制接口真正解決了這一問題,可以推廣到各種微機(jī)控制系統(tǒng)的抗干擾控制接口設(shè)計(jì)中去。

-

芯片

+關(guān)注

關(guān)注

459文章

52487瀏覽量

440632 -

cpld

+關(guān)注

關(guān)注

32文章

1257瀏覽量

171488 -

cpu

+關(guān)注

關(guān)注

68文章

11076瀏覽量

217012

發(fā)布評論請先 登錄

狀態(tài)機(jī)“毛刺”的產(chǎn)生及消除方法

如何設(shè)計(jì)自動駕駛系統(tǒng)的狀態(tài)機(jī)

FPGA/CPLD狀態(tài)機(jī)穩(wěn)定性研究

基于微機(jī)保護(hù)控制接口裝置實(shí)現(xiàn)CPLD抗干擾設(shè)計(jì)

微機(jī)系統(tǒng)軟件抗干擾的方法

CPLD狀態(tài)機(jī)抗干擾控制原理是什么

微機(jī)控制系統(tǒng)抗干擾設(shè)計(jì)試題題型相關(guān)資料下載

微機(jī)系統(tǒng)軟件抗干擾的方法

PLC控制系統(tǒng)應(yīng)用的抗干擾問題研究

單片機(jī)控制系統(tǒng)的抗干擾設(shè)計(jì)資料

利用狀態(tài)機(jī)實(shí)現(xiàn)對tlc5620dac控制.

狀態(tài)模式(狀態(tài)機(jī))

微機(jī)保護(hù)系統(tǒng)控制的CPLD狀態(tài)機(jī)的抗干擾控制接口設(shè)計(jì)

微機(jī)保護(hù)系統(tǒng)控制的CPLD狀態(tài)機(jī)的抗干擾控制接口設(shè)計(jì)

評論