引 言

數(shù)字信號處理領(lǐng)域中FFT算法有著廣泛的應(yīng)用。目前現(xiàn)有的文獻大多致力于研究利用FFT算法做有關(guān)信號處理、參數(shù)估計、F+FT蝶形運算單元與地址單元設(shè)計、不同算法的FFT實現(xiàn)以及FFT模型優(yōu)化等方面。而FPGA廠商Altera公司和Xilinx公司都研制了FFT IP核,性能非常優(yōu)越。在FFT的硬件實現(xiàn)中,需要考慮的不僅僅是算法運算量,更重要的是算法的復雜性、規(guī)整性和模塊化,而有關(guān)利用FFT IP核實現(xiàn)FFT算法卻涉及不多。這里從Altera IP核出發(fā),建立了基4算法的512點FFT工程,對不同參數(shù)設(shè)置造成的誤差問題進行分析,并在EP2C70F896C8器件上進行基于Quartus II的綜合仿真,得到利用FFT IP核的FFT算法高效實現(xiàn),最后利用Matlab進行的計算機仿真分析證明了工程結(jié)果的正確性。

1 算法原理

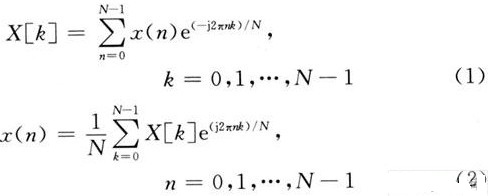

FFT算法是基于離散傅里葉變換(DFT),如式(1)和式(2):

求和運算的嵌套分解以及復數(shù)乘法的對稱性得以實現(xiàn)。其中一類FFT算法為庫利一圖基(Cooley-Tukey)基r按頻率抽選(DIF)法,將輸入序列循環(huán)分解為N/r個長度為r的序列,并需要logr N級運算。算法的核心操作是蝶型運算,蝶型運算的速度直接影響著整個設(shè)計的速度。

基4頻域抽取FFT算法是指把輸出序列X(k)按其除4的余數(shù)不同來分解為越來越短的序列,實現(xiàn)x(n)的DFT算法。FFT的每一級的運算都是有N/4個蝶形運算構(gòu)成,第m級的一個蝶形運算的四節(jié)點分別為Xm(k),Xm(k+N/4m),Xm(k+2N/4m)以及Xm(k+3N/4m),所以每一個蝶形運算結(jié)構(gòu)完成以下基本迭代運算:

式(3)~式(6)中:m表示第m級蝶形算法;k為數(shù)據(jù)所在的行數(shù);N為所要計算的數(shù)據(jù)的點數(shù);WN為旋轉(zhuǎn)因子。

將輸入序列循環(huán)分解為4點序列的基4分解,使用4點FFT在乘法上更具優(yōu)勢,Altera的:FFT兆核選用的就是基4運算,若N是2的奇數(shù)冪的情況下,F(xiàn)FT IP核則自動在完成轉(zhuǎn)換的最后使用基2運算。

2 FFT兆核(IP)函數(shù)

FFT Core支持4種I/O數(shù)據(jù)流結(jié)構(gòu):流(Stream-ing)、變量流(Variable Streaming)、緩沖突發(fā)(BufferedBurt)、突發(fā)(Burst)。流結(jié)構(gòu)允許輸入數(shù)據(jù)連續(xù)處理,并輸出連續(xù)的復數(shù)據(jù)流,這個過程不需要停止FFT函數(shù)數(shù)據(jù)流的進出。變量流結(jié)構(gòu)允許輸入數(shù)據(jù)連續(xù)處理,并產(chǎn)生一個與流結(jié)構(gòu)相似連續(xù)輸出數(shù)據(jù)流。緩沖突發(fā)數(shù)據(jù)流結(jié)構(gòu)的FFT需要的存儲器資源比流動I/O數(shù)據(jù)流結(jié)構(gòu)少,但平均模塊吞吐量減少。突發(fā)數(shù)據(jù)流結(jié)構(gòu)的執(zhí)行過程和緩沖突發(fā)結(jié)構(gòu)相同,不同的是,對于給定參數(shù)設(shè)置,突發(fā)結(jié)構(gòu)在降低平均吞吐量的前提下需要更少的存儲資源。

3 FFT處理器引擎結(jié)構(gòu)

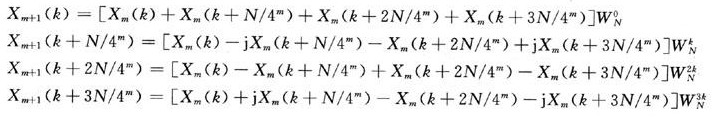

FFT兆核函數(shù)可以通過定制參數(shù)來使用兩種不同的引擎結(jié)構(gòu):四輸出(Quad-outlput)或單輸出(Signal-output)引擎結(jié)構(gòu)。為了增加FFT兆核函數(shù)的總吞吐量,也可以在一個FFT兆核函數(shù)變量中使用多個并行引擎。本文建立一個基于QuartusⅡ7.O計算24位512點FFT工程,采用四輸出FFT引擎結(jié)構(gòu),如圖1所示。

復取樣數(shù)據(jù)X[k,m]從內(nèi)部存儲器并行讀出并由變換開關(guān)(SW)重新排序,排序后的取樣數(shù)據(jù)由基4處理器處理并得到復數(shù)輸出G[k,m],由于基4按頻率抽選(DIF)分解方法固有的數(shù)字特點,在蝶形處理器輸出上僅需要3個復數(shù)乘法器完成3次乘旋轉(zhuǎn)因子(有一個因子為1,不需要乘)計算。這種實現(xiàn)結(jié)構(gòu)在一個單時鐘周期內(nèi)計算所有四個基4蝶形復數(shù)輸出。

同時,為了辨別取樣數(shù)據(jù)的最大動態(tài)范圍,四個輸出由塊浮點單元(BFPU)并行估計,丟棄適當?shù)淖畹臀?LSB),在寫入內(nèi)部存儲器之前對復數(shù)值進行四舍五入并行重新排序。對于要求轉(zhuǎn)換時間盡量小的應(yīng)用,四輸出引擎結(jié)構(gòu)是最佳的選擇;對于要求資源盡量少的應(yīng)用,單輸出引擎結(jié)構(gòu)比較合適。為了增加整個FFT吞吐量,可以采用多并行的結(jié)構(gòu)。

4 系統(tǒng)驗證

4.1 工程仿真

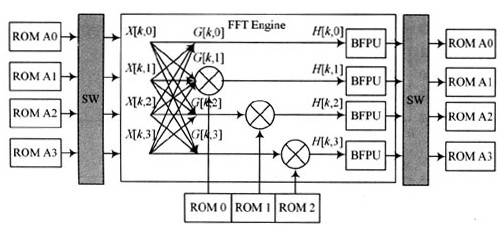

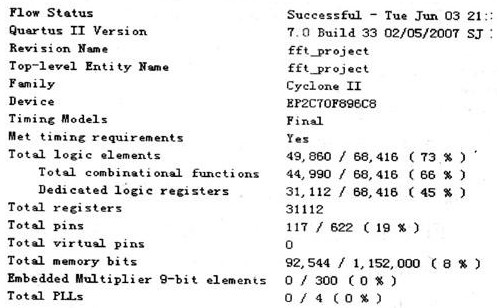

選擇CycloneⅡ系列的EP2C70F896C8芯片來實現(xiàn),先在QuartusⅡ軟件下進行綜合仿真,初始化參數(shù)設(shè)置FFT變換長度為512點,數(shù)據(jù)和旋轉(zhuǎn)因子精度為24 b,選擇緩沖突發(fā)的數(shù)據(jù)流結(jié)構(gòu),四輸出引擎并行FFT引擎?zhèn)€數(shù)為4個,復數(shù)乘法器結(jié)構(gòu)為“4/Mults/2Adders”。EP2C70F896C8芯片包括68 416個邏輯單元,31 112個寄存器單元,最大用戶輸入/輸出引腳622個,總RAM達1 152 000 b,其布線資源由密布的可編程開關(guān)來實現(xiàn)相互間的連接,這種結(jié)構(gòu)完全符合實現(xiàn)FFT電路的要求。

經(jīng)綜合和時序分析得知:其工作時鐘頻率

69.58 MHz(period=14.372 ns),進行一次蝶形運算只需約14 ns,全部512點數(shù)據(jù)處理完成則需14.372×4×512=29.3μs滿足時序要求。具體綜合結(jié)果如圖2所示,為Quartus軟件環(huán)境下仿真得到。

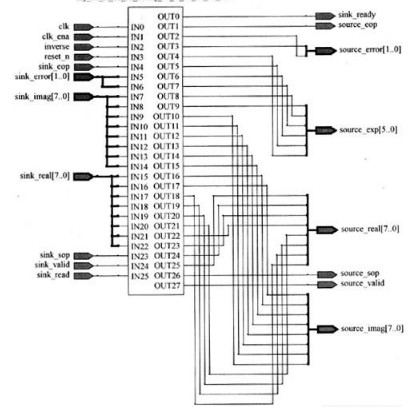

圖3則表明了FFT的綜合邏輯結(jié)果,為編譯成功后的RTL級電路描述。

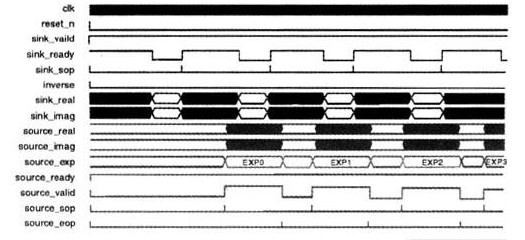

FFT處理器模塊采用緩沖突發(fā)數(shù)據(jù)流結(jié)構(gòu)的信號時序圖如圖4所示,在系統(tǒng)復位信號(reset_n)變?yōu)榈碗娖胶螅瑪?shù)據(jù)源將sink_ready信號置高電平,表明有能力接收輸入信號。數(shù)據(jù)源加載第一個復數(shù)數(shù)據(jù)樣點到FFT函數(shù)中,同時將sink_sop信號置高電平,表示輸入模塊的開始。在下一個時鐘周期,sink_sop信號被復位,并以自然順序加載后面的N-1個復輸人數(shù)據(jù)樣點。

當完全載入輸入模塊時,F(xiàn)FT函數(shù)復位sink_ena信號,表示FFT不再接收其他輸入數(shù)據(jù)并開始計算輸入數(shù)據(jù)模塊的變換結(jié)果。在FFT處理器內(nèi)部輸入緩沖區(qū)讀取樣點之后,F(xiàn)FT將sink_ena信號重新置高電平,準備讀取下一個輸入模塊。下一個輸入模塊的起點由sink_sop脈沖確定。當FFT完成了輸入模塊的變換,并且從設(shè)備匯端將source_ready信號(表示數(shù)據(jù)從設(shè)備接收器可以接收輸出數(shù)據(jù)模塊)置高電平,并且以自然順序輸出復數(shù)變換域數(shù)據(jù)模塊。

4.2 仿真結(jié)果分析

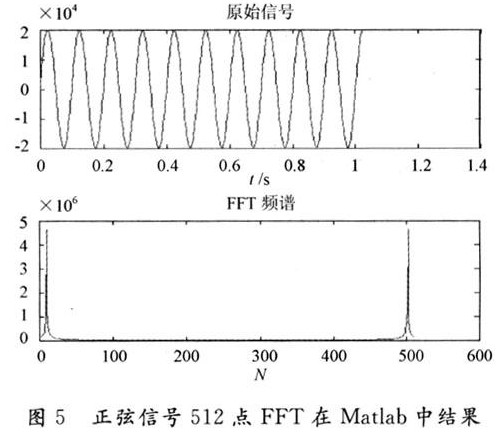

在編譯綜合后,工程當中含有基于FFT IP核生成的Matlab文件,這樣就可在Matlab下對工程結(jié)果進行進一步測試,構(gòu)建信號,并與Matlab計算的理論結(jié)果進行比較。設(shè)輸入函數(shù)為z(t)=20 000sin(20πt),點數(shù)N=512,采樣頻率為500 Hz,即采樣間隔為O.002 s,采樣的時間長度為O.002 x 512 s,該正弦信號通過512點FFT處理結(jié)果如圖5所示,正弦信號基于IP核Matlab文件仿真結(jié)果如圖6所示。

由圖5,圖6比較可以看出FFT、處理器處理后的結(jié)果和Matlab計算的理論結(jié)果基本一致。都在第11點和第503點取得最大FFT絕對值,兩者的誤差只是在FFT頻譜絕對值的幅度大小原因:一是Altera FFT兆核函數(shù)的塊浮點輸出與Matlab這種全精度FFT的輸出相比,存在最低位(LSB)被丟棄的影響;二是工程初始化IP核采用的數(shù)據(jù)精度取24位(V7.0 IP最大支持24位數(shù)據(jù)精度)。

5 結(jié) 語

在利用FFT IP核進行FFT算法實現(xiàn)的同時,對仿真結(jié)果做了全面分析,由于IP核的可塑性很強,增加了芯片的靈活性。使用Altera FFT的IP Core大大減少了產(chǎn)品的開發(fā)時間,Altera還可進一步實現(xiàn)加窗功能,甚至DDC部分(單端信號向I/Q轉(zhuǎn)換)整合到其FFT處理器模塊中,能進一層次簡化開發(fā)的流程,在今后實際工程應(yīng)用中高效利用。

-

處理器

+關(guān)注

關(guān)注

68文章

19799瀏覽量

233464 -

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613910 -

仿真

+關(guān)注

關(guān)注

51文章

4234瀏覽量

135286

發(fā)布評論請先 登錄

Quartus中FFT模塊中文說明

在做FFT IP核的仿真時遇到問題,居然不能生成FFT的仿真文件,求解答

xilinx FPGA的FFT IP核的調(diào)用

fft ip核 仿真問題

有關(guān)modelsim仿真fft核出現(xiàn)的錯誤

QUARTUS 13.1在生成FFT IP核時仿真文件生成不了?

基于FPGA的FFT和IFFT IP核應(yīng)用實例

利用FFT IP Core實現(xiàn)FFT算法

Quartus中fft ip core的使用

可配置FFT IP核的實現(xiàn)及基礎(chǔ)教程

基于Quartus II的綜合仿真實現(xiàn)FFT IP核的FFT算法

基于Quartus II的綜合仿真實現(xiàn)FFT IP核的FFT算法

評論