目前智能儀器已廣泛應用于科研和工業生產當中,但是許多儀器分散在不同的地理位置上, 不易操作和維護, 并且實時跟蹤性能差, 人為誤差大, 數據無法保存, 另外大量高檔儀表價格相當昂貴。為解決上述難題, 在計算機的提示下完成操作, 可以減少人為因素造成的損壞,并提高測試數據的準確度。由于智能儀器是RS 232 接口, 上位機用的是USB 接口, 所以還需由FPGA 實現RS232 與USB 之間的接口轉換。由于FPGA 可以并行處理, 集成度高, 可用資源豐富, 所以利用FPGA 進行數據處理, 可以減少上位機的工作量, 減少數據處理的時間,還可以縮短設計周期, 減小板卡體積, 以便于集成到其他板卡上。

1 控制系統及接口簡介

1. 1 系統功能

在整個系統中, 上位機可以實時對系統進行監控,并下發相應的命令。智能儀器傳出的數據通過RS 232接口傳送到FPGA, FPGA 根據上位機下發的命令對這些數據進行判決、處理, 然后經過USB 接口上傳給上位機, 再由上位機對FPGA 處理過的數據進行顯示、存儲等操作。

1. 2 U SB 接口芯片簡介

本設計采用的是CYPRESS 半導體公司的EZUSBFX2 系列芯片CY7C68013。CY7C68013 是一款高性能USB 2. 0 微控制器, 它提供了全面的USB 2. 0 外圍設備解決方案。工作模式有Port, Slave FIFO 和GPIFMaster 三種, 本方案采用Slave FIFO 模式。在該模式下, 外部控制器( 如FPGA) 可像對普通FIFO 一樣對FX2中端點為2, 4, 6, 8 的數據緩沖區進行讀/ 寫。FX2 內嵌的8051 固件的功能只是配置Slave FIFO 相關的寄存器,以及控制FX2 何時工作在Slave FIFO 模式下。一旦8051 固件將相關的寄存器配置完畢, 且使自身工作在Slave FIFO 模式下后, 外部邏輯( 如FPGA) 即可按照Slave FIFO 的傳輸時序, 高速地與主機進行通信, 而在通信過程中不需要8051 固件的參與。

1. 3 RS 232 接口簡介

RS232C 標準( 協議) 的全稱是EIARS232C 標準。EIARS232C 是用正負電壓來表示邏輯狀態的,與T TL 以高低電平表示邏輯狀態的規定不同。因此,為了能夠與計算機接口或終端的T T L 器件連接, 必須使EIARS232C 與T TL 電路之間進行電平和邏輯關系的變換。實現這種變換的方法可用分立元件, 也可用集成電路芯片。該設計用的是MAX3232 芯片。

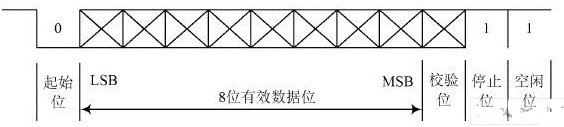

RS 232 的數據傳輸格式如圖1 所示。

圖1 RS 232 標準的數據傳輸格式

RS 232 傳輸格式包含起始位( 1 b) 、有效數據位( 8 b) 、奇偶校驗位( 0~ 2 b) 、停止位( 1 b) 。傳輸線在空閑時為高電平, 因此起始位為低電平, 停止位為高電平。

奇偶校驗位可設置為奇校驗、偶校驗或不校驗, 有效數據位是從低位開始傳送。

2 FPGA 設計

2. 1 USB 接口時序

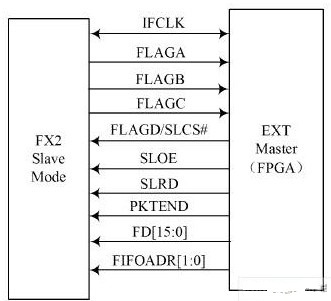

在Slav e FIFO 方式下, 外部邏輯與FX2 的連接信號如圖2 所示。

圖2 FX2 Slave 模式下接口管腳連接圖

在Slav e FIFO 模式下, CY7C68013 芯片為端口2,4, 6, 8 提供滿空標志位FLAGA, FLAGB, FLAGC,FLAGD。IFCLK 為FX2 輸出的時鐘, 可作通信的同步時鐘; SLCS 為FIFO 的片選信號; SLOE 為FIFO 輸出使能; SLRD 為FIFO 讀信號; SLWR 為FIFO 寫信號。對FPGA 來說, 4 個端口分別為4 個FIFO。

FPGA檢測4 個滿空標志位來分別對相應的FIFO 進行讀/ 寫。FPGA 可以選擇同步或異步讀/ 寫, 在該設計中采用異步讀/ 寫。在異步Slave FIFO 寫時, 時鐘由FPGA 提供。數據在SLWR 的每個有效-無效的跳變沿時被寫入, FIFO 寫指針遞增。異步Slave FIFO 讀時,FIFO 讀指針在SLRD 的每個有效-無效的跳變沿時遞增以改變數據。

2. 2 FPGA 程序設計

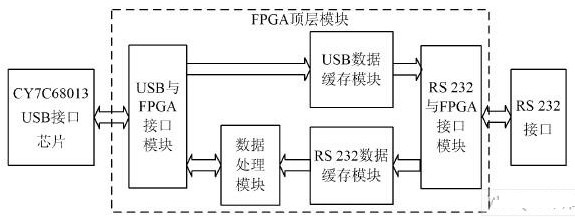

FPGA 設計是整個系統的核心部分, 由VHDL 語言實現。FPGA 實現了USB 與RS 232 接口的轉換、數據的處理、命令的傳輸等功能。有了上面的接口時序,便可以進行FPGA 設計。FPGA 部分的總體設計如圖3所示。模塊介紹:

USB 與FPGA 接口模塊: U SB 與FPGA 之間的接口轉換模塊, 主要功能為將USB 接口傳過來的信息緩存到FPGA 內部FIFO, 并將由數據處理模塊處理過的數據傳給U SB 芯片。即產生控制信號讀/ 寫U SB 芯片內部FIFO。可以由讀/ 寫FIFO 兩個有限狀態機實現。

以讀取CY7C68013 芯片內數據為例, 根據異步讀U SB內的FIFO 時序圖可分為4 個狀態: 空閑態、選擇地址態、準備讀數據態、讀數據態、讀取后狀態[ 6] 。在空閑態, 當讀事件發生時進入選擇地址態; 在選擇地址態, 使FIFOADR[ 1: 0] 指向OUT FIFO, 進入準備讀數據態;在準備讀數據態, 如FIFO 空, 在本狀態等待, 否則進入讀數據態; 在讀數據態, 使SLOE, SLRD 有效, 從數據線上讀數, 再使SLRD 無效, 以遞增FIFO 讀指針, 再使SLOE 無效, 進入讀取后狀態; 在讀取后狀態, 如需傳輸更多的數, 進入準備讀數據態, 否則進入空閑態。

圖3 FPGA 總體設計框圖

USB 數據緩存模塊: 用來緩存計算機發給智能儀器的指令等信息。是由FPGA 芯片的IP 核生成的先入先出存儲器FIFO。容量為8 b* 512 depth。占用1 個塊RAM 資源。

RS 232 數據緩存模塊: 用來緩存由智能儀器發出的數據。是由FPGA IP 核生成的先入先出存儲器FIFO。容量為8 b*512 depth, 占用1 個塊RAM資源。

RS 232 與FPGA 接口模塊: RS 232 與FPGA 之間的接口轉換模塊。主要功能為進行串/ 并和并/ 串轉換。

將USB 數據緩存模塊中緩存的內容以合適的速率通過串口發給智能儀器, 并將智能儀器發出的數據緩存到RS 232 數據緩存模塊中。此模塊也是由兩個狀態機實現。串口通信必須要設定波特率, 這里采用的波特率為9 600 Kb/ s, 采用的時鐘為50 MHz, 相當于傳送1 位數據需要約5 028 個時鐘周期, 這里采用減法計數器來控制, 即計數器計到5 028 個時鐘周期后, 就開始傳輸下一位數據。

數據處理模塊: 主要功能為根據上位機的指令對RS 232 數據緩存中的數據做出相應的處理。處理后再向上位機傳。主要的處理方式有定時取數、平滑處理等。實現方式由狀態機等實現。FPGA 頂層模塊: 主要負責各模塊間數據流的流向。以及與外部芯片相連的輸入輸出信號的定義。

系統在工作時, 在采集數據上傳上位機時, 數據通道為: 智能儀器發送的數據通過RS 232接口模塊存在RS232 數據緩存模塊中緩存。當緩存到一定的數據量后,再通過數據處理模塊連續的讀取FIFO 中的數據并根據上位機發送的命令進行相應的數據處理, 然后將處理的數據通過USB 與FPGA 接口模塊傳給USB 接口。在上位機下發控制命令時, 數據通道為: 上位機發送的命令通過USB 口傳給FPGA 的RS 232 與FPGA 接口模塊, 此模塊判斷是數據處理指令還是控制儀器指令。如果是數據處理指令, 則傳向數據處理模塊讓其按要求進行數據處理。如果是控制儀器指令, 則將其存入USB 數據緩存模塊中, 再由RS 232 與FPGA 接口模塊讀取, 轉成RS2322 格式后傳出。由于RS 232 接口速度比USB 接口慢, 用FPGA 內部的異步時鐘FIFO 解決速率匹配問題。

將通過RS 232傳過來的數據緩存在FIFO 中, 然后存到一定數據量后再全部連續的取出, 如此往復, 從而實現數據的連續采集及上位機的實時顯示。將通過USB 傳過來的數據放在另一個FIFO 中緩存 , 讓FPGA 按照RS232 的速率進行讀取。這樣可以防止RS 232 的速度跟不上USB 的速度而產生的數據丟失。

3 仿真結果

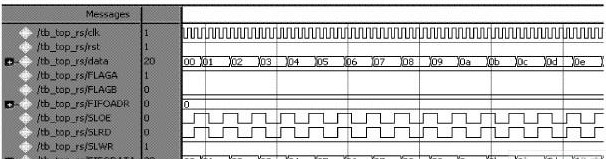

FPGA 采用的系統時鐘頻率為50 MHz, 仿真工具為Mo delsim SE 6. 5a, 仿真用數據為連續的8 b 數據。

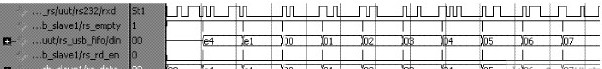

仿真結果如圖4 所示。

圖4 FPGA 讀USB 內部FIFO 仿真圖

圖4 為FPGA 讀USB 內部FIFO 的仿真結果,DATA 為模擬從USB 口接到的數據, 該數據已存在于USB 芯片的FIFO 中。FIFODAT A 為FPGA 接到的數據, 由上可以看出, FPGA 可以將U SB 接受到的數據解析出來。

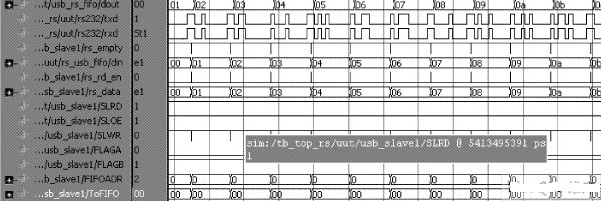

圖5 為RS 232 與FPGA 接口部分仿真結果。可以看出, 由RS 232 接收串行數據RXD 已經轉換為并行數據din。程序中是在一個有效字節結束后將其存入FIFO 中, 由圖可以驗證。圖6 頂層模塊仿真圖, 為了驗證由FPGA 發出的數據能正確的接受到, 先由FPGA 內部發數據, 然后通過RS 232 的T XD 端口發出,讓RXD 與TXD 相連再接收, 可以看出發出的數據可以被正確的接收回來并傳向U SB 接口, 說明時序正確。

同理可以驗證U SB 端的收發時序。

圖5 RS 232 接收端仿真圖

圖6 頂層模塊仿真圖

4 結 語

本文采用FPGA 實現了USB 與RS 232 間的接口轉換及數據處理的功能。設計中先入先出存儲器的運用解決了數據的緩存的和速率匹配問題, 有限狀態機的運用使得程序設計更加清晰可靠。該設計將復雜的信號運算集中在FPGA 中完成, 利用FPGA 獨特的并行處理能力,減小上位機工作量的同時, 提高了系統運行速度。

-

FPGA

+關注

關注

1645文章

22042瀏覽量

618244 -

芯片

+關注

關注

459文章

52487瀏覽量

440631 -

控制系統

+關注

關注

41文章

6780瀏覽量

112149

發布評論請先 登錄

基于ARM的智能家居遠程控制系統設計

【云智易申請】基于STM32智能家居遠程控制系統研究

論文-基于stm32的智能家居遠程控制系統

看智能工廠如何將遠程控制儀器系統應用于無人值守的測試間?

基于web的智能工業遠程控制系統的設計

智能電話遠程控制系統的設計與實現

電話遠程控制系統的實現

智能路燈遠程控制系統

智能電表是如何與遠程控制系統連接的?

采用FPGA與USB芯片實現智能儀器遠程控制系統的設計與仿真分析

采用FPGA與USB芯片實現智能儀器遠程控制系統的設計與仿真分析

評論