前面的文章中介紹過,MSI本質(zhì)上是一種Memory Write,和PCIe總線中的Message概念半毛錢關(guān)系都沒有。并且,MSI的Data Payload也是固定的,始終為1DW。

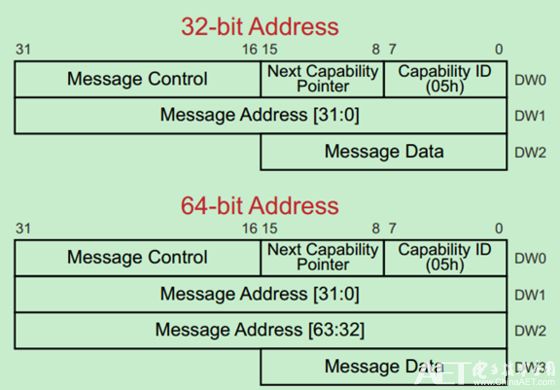

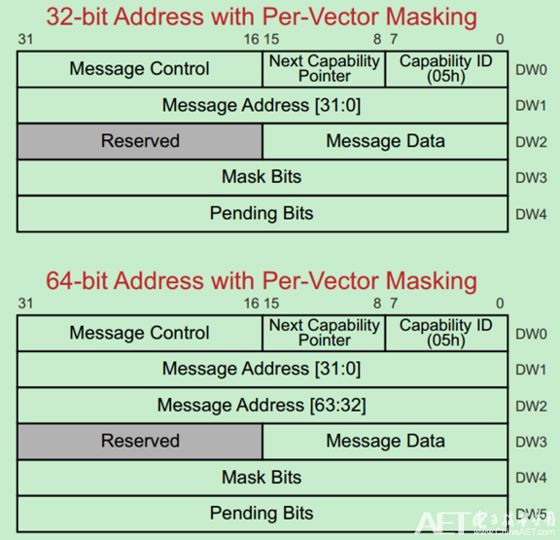

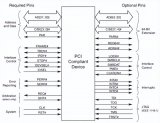

由于MSI也是從PCI總線繼承而來的,因此MSI相關(guān)的寄存器也存在于配置空間中的PCI兼容部分(前256個字節(jié))。如下圖所示,MSI有四種類型:

其中Capability ID的值是只讀的,05h表示支持MSI功能。

Next Capability Pointer也是只讀的,其用于查找下一個MSI的位置,00h則表示到達(dá)Linked List的最后了。

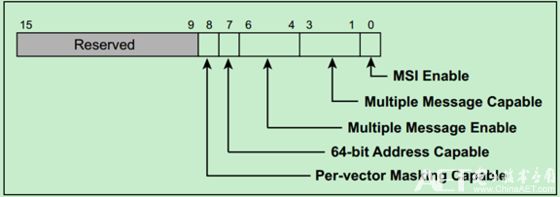

Message Control Register用于確定MSI的格式與支持的功能等信息,如下圖所示:

具體描述如下:

Message Address Register:32-bit最低兩位固定為0,使得該地址是DW對齊的。

當(dāng)Mask Bits將相關(guān)的中斷向量(Interrupt Vector)屏蔽后,該MSI將不會被發(fā)送。軟件可以通過這種方式來使能或者禁止某些MSI的發(fā)送。如果相關(guān)中斷向量沒有被屏蔽,則如果發(fā)生了相關(guān)中斷請求,這時Pending Bits中的相應(yīng)bit則會被置位。一旦中斷信息被發(fā)出,則該bit會立即被清零。

注:可能有的人會有疑惑了(無論是Mindshare的書,還是PCI的Spec都沒有明確解釋),因?yàn)镸ask Bits和Pending Bits都只有32位,而8位的中斷向量號最多可以表示256個!顯然,32位最多只能對應(yīng)32個中斷向量號,無法支持256個的。實(shí)際上,一般的系統(tǒng)不會支持256個中斷向量號的,32個就已經(jīng)足夠用了,所以并不用擔(dān)心這個問題。

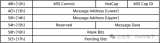

PCIe設(shè)備會根據(jù)配置空間中的MSI請求信息,來創(chuàng)建Memory Write TLP,來講MSI信息發(fā)送出去。作為一種特殊的TLP,傳遞MSI的TLP需要遵循以下規(guī)則:

· No Snoop和Relaxed Ordering bits的值必須為0

· TLP長度值必須為01h

· First BE必須為1111b

· Last BE必須為0000b

· 地址是直接從配置空間中的響應(yīng)位置復(fù)制過來的

如下圖所示:

-

寄存器

+關(guān)注

關(guān)注

31文章

5421瀏覽量

123288 -

PCIe

+關(guān)注

關(guān)注

16文章

1322瀏覽量

84656

原文標(biāo)題:【博文連載】PCIe掃盲——中斷機(jī)制介紹(MSI)

文章出處:【微信號:ChinaAET,微信公眾號:電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

將Hyperlink和pcie合在一起之后,Pcie無法響應(yīng)MSI中斷

PCIE MSI中斷的配置

xp支持PCIE中的MSI中斷方式么

DM8168 C6678 pcie msi 中斷不能觸發(fā),請問是什么原因?

PCIe設(shè)備發(fā)出MSI-X中斷請求的方法

PCIe掃盲—PCIe錯誤檢測機(jī)制的詳細(xì)資料概述

PCIe兩種中斷傳遞方式

克服MSI機(jī)制的三個主要的缺陷

簡述PCI總線的中斷機(jī)制

教大家如何處理x86處理器中MSI-X中斷請求

簡述MSI和MSI-X中斷機(jī)制

x86處理器如何處理MSI-X中斷請求

Linux內(nèi)核PCIE基礎(chǔ)知識整理

PCIe熱插拔機(jī)制介紹

PCIe中斷機(jī)制介紹(MSI)

PCIe中斷機(jī)制介紹(MSI)

評論