引言

NioslI嵌入式處理器是A1tera公司提出的SOPC解決方案,是一種用戶可隨意配置和構(gòu)建的32位嵌入式處理器,結(jié)合豐富的外設(shè)可快速、靈活地構(gòu)建功能強大的SOPC系統(tǒng)。Altera公司提供了一些通用的IP核,使得用戶可輕松集成屬于自己的專用功能;但對于一些特定的外設(shè),沒有現(xiàn)成可用的IP核,如液晶模塊CBGl28064等。

用戶可通過自定義邏輯的方法在SOPC設(shè)計中添加自定義IP核。在實際應(yīng)用中,LCD液晶顯示器憑借功耗低、體積小、輕薄及控制驅(qū)動簡單等特點,在智能儀器、儀表和低功耗電子產(chǎn)品中得到了廣泛應(yīng)用。本文以深圳秋田視佳實業(yè)有限公司的液晶顯示模塊CBGl28064為例,在基于NioslI的SOPC系統(tǒng)中設(shè)計了LCD顯示驅(qū)動IP核,并下載到Cyclone系列的FPGA中,實現(xiàn)了對LCD的顯示驅(qū)動。

1 CBGl28064液晶顯示模塊

CBG128064是一款以2片HD61202作為列驅(qū)動器,1片HD61203作為行驅(qū)動器的液晶模塊。HD61202是一種帶有驅(qū)動輸出的圖形液晶顯示控制器,可直接與8位微處理器相連;而HD61203只需提供電源,就能產(chǎn)生行驅(qū)動信號和各種同步信號。CBGl28064液晶顯示模塊內(nèi)置顯示存儲器RAM,顯示屏上各像素點的顯示狀態(tài)與顯示存儲器RAM中的各位數(shù)據(jù)一一對應(yīng)。顯示存儲器的數(shù)據(jù)直接作為圖形顯示的驅(qū)動信號。外部處理器只需要通過其8位數(shù)據(jù)線和6條控制線來設(shè)置所需要的顯示方式,其他功能均由模塊自動完成。HD61202提供7條簡單的指令:顯示開/關(guān)指令、顯示起始行(ROW)設(shè)置指令、頁(RAGE)設(shè)置指令、列地址(Y Address)設(shè)置指令、讀狀態(tài)指令、寫數(shù)據(jù)指令、讀數(shù)據(jù)指令。

2 方案選擇

通常有兩種方式可以實現(xiàn)NiosII嵌入式處理器對LCD的顯示驅(qū)動:

一種是利用現(xiàn)成的并行輸入/輸出(PIO)內(nèi)核。該內(nèi)核提供了Avalon總線從控制器端口到通用I/O口間的存儲器映射接口,將LCD模塊的接口與NiosII嵌入式處理器的并行端口相連接,NiosII嵌入式處理器通過對其端口的操作來完成對LCD模塊的控制。這種方式類似于單片機操作,時序簡單,易于實現(xiàn);但是在SOPC系統(tǒng)中硬件上需要設(shè)計與外設(shè)相連的I/O口,軟件上需要編寫接口程序進行讀寫控制,增加了處理器的時間開銷,F(xiàn)PGA的并行處理能力沒有得到發(fā)揮。

另一種是采用自定義IP核方式。把LCD模塊看成是外部存儲器或I/O設(shè)備,作為從設(shè)備掛接到NiosII嵌入式處理器的Avalon總線上,處理器以訪問I/O設(shè)備或讀寫存儲器的方式對其進行控制。這種方法需要寫HDL模塊,自己定義控制、狀態(tài)、數(shù)據(jù)寄存器和控制位,可較為靈活地實現(xiàn)復(fù)雜的時序控制。一旦完成了設(shè)計,即可封裝為SOPC BLdldel可用的獨立元件,用戶可以像使用Altera公司提供的其他外設(shè)一樣來使用,并且可以提供給其他設(shè)計者使用。本文選用該方式實現(xiàn)。

3 LCD顯示驅(qū)動設(shè)計

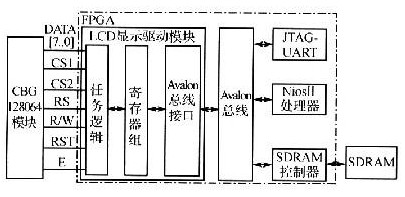

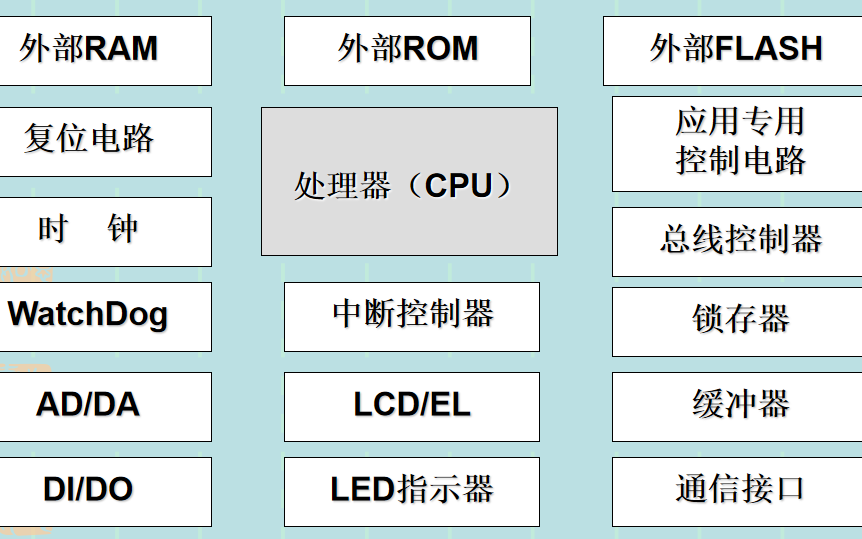

圖1為系統(tǒng)結(jié)構(gòu)圖。設(shè)計的重點在于LCD顯示驅(qū)動模塊的設(shè)計。按照模塊化、層次化的設(shè)計思想,顯示驅(qū)動可分為3部分實現(xiàn),即任務(wù)邏輯部分、寄存器組部分和Avalon總線接口部分。任務(wù)邏輯部分描述液晶模塊的讀寫邏輯功能;寄存器文件部分提供了內(nèi)部寄存器訪問的通道;Avalon總線接口部分通過頂層接口模塊對寄存器進行操作,從而實現(xiàn)對行為模塊的訪問和控制。其中,DATA[7..0]為8位數(shù)據(jù)線,CSl、CS2為片選信號,RS為指令/數(shù)據(jù)選擇信號,R/W為讀寫選擇信號,RST為復(fù)位信號,E為讀寫使能信號。

3.1 任務(wù)邏輯

任務(wù)邏輯是整個驅(qū)動的核心部分。要實現(xiàn)對LCD的顯示控制,就要按照CBG128064驅(qū)動控制器的規(guī)范及時序要求進行設(shè)計。在時序邏輯電路中,數(shù)據(jù)信號和控制信號的配合比較復(fù)雜,但又十分重要,使用有限狀態(tài)機可以較為容易地設(shè)計出復(fù)雜的數(shù)字電路系統(tǒng)。

本文采用有限狀態(tài)機實現(xiàn)顯示驅(qū)動的核心邏輯。根據(jù)驅(qū)動控制器的讀寫命令及讀寫時序要求,本文設(shè)計了3個狀態(tài)機,分別為讀寫控制狀態(tài)機、讀寫狀態(tài)機和讀寫時序狀態(tài)機。

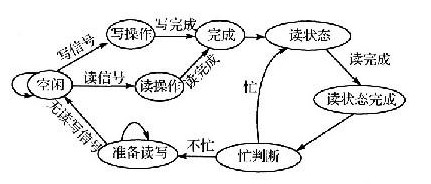

如圖2所示,讀寫控制狀態(tài)機用于當發(fā)生讀寫請求時進行忙狀態(tài)檢測及讀寫操作控制,并在每個狀態(tài)給出時序狀態(tài)機讀寫信號。

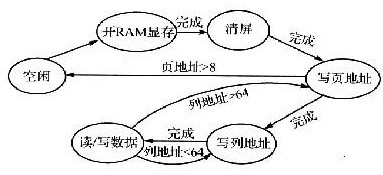

如圖3所示,讀寫狀態(tài)機給出讀或者寫信號,并在讀寫控制狀態(tài)機的控制下,完成寫命令、寫數(shù)據(jù)和讀數(shù)據(jù)之間的狀態(tài)轉(zhuǎn)移。在每一個狀態(tài)下給出LCD顯示數(shù)據(jù)及控制信號,如片選、所寫數(shù)據(jù)/指令等。

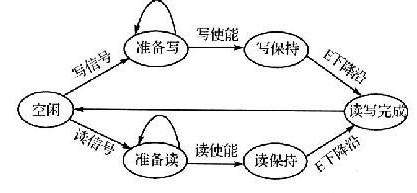

如圖4所示,讀寫時序狀態(tài)機用于控制讀或者寫外設(shè)的時刻,當讀寫完成時給出讀寫完成信號。其中,讀寫信號由圖2中的讀寫操作給出。根據(jù)CBGl28064讀寫時序要求,當R/W為高電平時,讀取顯示RAM中的數(shù)據(jù);當R/W為低電平且在E的下降沿時,向顯示RAM中寫入數(shù)據(jù)。讀寫時序狀態(tài)機的讀寫信號由讀寫控制狀態(tài)機給定,其中,E為模塊使能信號。

3.2 寄存器組

寄存器組由一系列寄存器組成,為軟件提供了訪問硬件的通道。寄存器組中的寄存器是根據(jù)任務(wù)邏輯中需要實現(xiàn)的特定邏輯功能來設(shè)定的,任務(wù)邏輯中的數(shù)據(jù)通過這些寄存器傳輸。本設(shè)計中,寄存器組設(shè)定了8位頁地址寄存器、8位列地址寄存器,以及32位數(shù)據(jù)寄存器等。

3.3 Ayalon總線接口

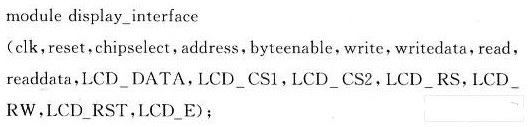

顯示驅(qū)動的Avalon總線接口需要一個簡單的Slave端口。該端口使用較少的Avalon信號來處理簡單的寄存器讀/寫傳輸。該模塊是與Avalon總線接口的一個頂層模塊,主要功能是對任務(wù)邏輯模塊和寄存器模塊進行例化和封裝,使其信號類型符合Avalon總線信號規(guī)范和外接模塊的信號規(guī)范。頂層接口定義如下:

3.4 顯示驅(qū)動封裝及軟件設(shè)計

直接在SOPC Builder中添加設(shè)計好的顯示驅(qū)動IP Core和Verilog HDL語言描述的文件,并根據(jù)Avalon總線傳輸規(guī)范設(shè)置好相關(guān)的信號線及傳輸參數(shù)。由于是在NiosII IDE環(huán)境下直接編寫用戶程序,可以不用編寫驅(qū)動程序。完成后,將顯示驅(qū)動IP Core添加至SOPC工程,并編譯、下載到FPGA器件中。

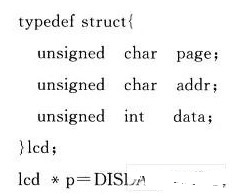

在NiosII IDE環(huán)境下,使用自己添加的模塊編寫程序,可直接調(diào)用甬數(shù)IOWR(BASE,OFFSET,DATA)和IORD(BASE,OFFSET)對內(nèi)部寄存器進行讀寫。本文使用結(jié)構(gòu)體定義了一個指向模塊的結(jié)構(gòu)體指針,對寄存器進行讀寫操作。

CBGl28064本身不帶字庫,可以通過2種方式添加字庫:一種是把所需字庫做到硬件ROM中,增加了硬件資源成本,且缺乏靈活性;另一種是在軟件中定義字庫,通過寫數(shù)據(jù)寄存器進行顯示。本設(shè)計采用第2種方式,在軟件中定義字庫,并編寫了簡單的顯示測試程序,在液晶屏上顯示“ZHONG GUO”字樣。測試結(jié)果表明,該設(shè)計是正確可行的。此外,利用字模軟件生成的圖形數(shù)據(jù),也可進行圖形顯示。

結(jié)語

本文采用有限狀態(tài)機設(shè)計了CBGl28064液晶模塊驅(qū)動硬件邏輯,并將顯示驅(qū)動IP核進行封裝構(gòu)成了一個模塊化的獨立元件,使其能夠在其他的工程中復(fù)用;在此基礎(chǔ)上,基于NiosII嵌入式處理器構(gòu)建了一個用戶定制的片上系統(tǒng)。經(jīng)過在Cyclone系列FPGA上測試,該驅(qū)動能夠在C-BGl28064液晶模塊上顯示字符、圖形。整個系統(tǒng)體現(xiàn)了SOPC嵌入式系統(tǒng)的靈活性和擴展性。

-

處理器

+關(guān)注

關(guān)注

68文章

19887瀏覽量

235090 -

嵌入式

+關(guān)注

關(guān)注

5150文章

19660瀏覽量

317405 -

液晶顯示器

+關(guān)注

關(guān)注

11文章

585瀏覽量

44366

發(fā)布評論請先 登錄

請問如何實現(xiàn)片上嵌入式Nios Ⅱ軟核六處理器系統(tǒng)的設(shè)計?

Nios II入門起步-創(chuàng)建一個嵌入式處理器系統(tǒng)

嵌入式處理器在片調(diào)試功能的設(shè)計

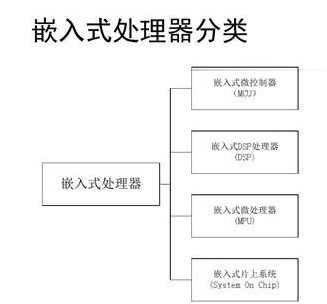

嵌入式系統(tǒng)教程之嵌入式處理器的詳細資料說明

基于NiosII嵌入式處理器的片上系統(tǒng)設(shè)計

基于NiosII嵌入式處理器的片上系統(tǒng)設(shè)計

評論