1 引言

EDSL技術(shù)是基于IP交換的新型寬帶接入技術(shù),它結(jié)合了以太網(wǎng)技術(shù)和xDSL技術(shù)的優(yōu)點,首次在接入網(wǎng)內(nèi)實現(xiàn)IP端到端的傳輸,中間無協(xié)議轉(zhuǎn)換,大大降低了信令處理的復(fù)雜性。EDSL獨特的智能頻譜管理技術(shù)和時分雙工模式,大大簡化了系統(tǒng)結(jié)構(gòu),同時也順應(yīng)了主干網(wǎng)IP化的趨勢。與傳統(tǒng) xDSL技術(shù)比較,它不僅克服了 xDSL技術(shù)的許多局限性(如對線路的挑、串?dāng)_等),并且增大了傳輸距離,提高了傳輸效率,EDSL系統(tǒng)結(jié)構(gòu)與ADSL類似,其核心部分是EDSL Modem.

在EDSL實現(xiàn)中,本文提出了可剝奪實時內(nèi)核的實時操作系統(tǒng)μC/OS-II和32位精簡指令集軟核處理器 Nios核相結(jié)合的方法,構(gòu)成一種基于可配置的軟核處理器的嵌入式開發(fā)平臺。該平臺軟、硬件均可按照用戶需求進行剪裁配置,最大程度地提供了系統(tǒng)設(shè)計的靈活性,具有重要的應(yīng)用價值。

2 EDSL系統(tǒng)結(jié)構(gòu)和協(xié)議棧

EDSL 的主要技術(shù)特點:(1)IP端到端網(wǎng)絡(luò);(2)采用時分復(fù)用技術(shù),雙向帶寬動態(tài)分配;(3)客戶服務(wù)器模式,I P 包無碰撞機制;(4)數(shù)據(jù)突發(fā)技術(shù)。正是由于以上技術(shù)的采用,使得EDSL技術(shù)不僅克服了xDSL技術(shù)的許多局限性,并且增大了傳輸距離,提高了傳輸效率。EDSL的系統(tǒng)結(jié)構(gòu)與ADSL類似,由位于用戶端的EDSL Modem 和 局端的高密度接入復(fù)用設(shè)備DSLAM(DSL Access Multiplexer)構(gòu)成,其結(jié)構(gòu)如圖1所示。

與基于ATM的ADSL技術(shù)相比,EDSL技術(shù)擁有更為簡單的協(xié)議結(jié)構(gòu),如圖所示2。

3硬件平臺的設(shè)計

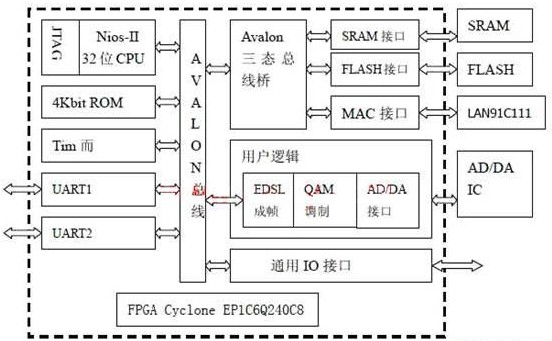

EDSL Modem硬件平臺的搭建主要使用了 Altera公司的 FPGA Cyclone EP1C6Q240C8芯片,它擁有充足的可編程邏輯資源內(nèi)嵌32位Nios-II軟核處理器來實現(xiàn)整個可編程嵌入式系統(tǒng)。系統(tǒng)的主要功能由FPGA實現(xiàn),硬件電路除 FPGA外只需加上存儲器件、以太網(wǎng)控制芯片和前端AD/DA轉(zhuǎn)換芯片即可。本系統(tǒng)主要使用了一片 8M Byte Flash,一片16M Byte SDRAM,以及以太網(wǎng)接口控制芯片等作為FPGA的外圍設(shè)備,硬件結(jié)構(gòu)簡單明了,極大提高了系統(tǒng)的可靠性。FPGA系統(tǒng)運行時鐘為50MHz,充分保證了系統(tǒng)的運行速度。

在硬件平臺的搭建中主要用到了Altera公司的Quartus-II與SOPC Builder軟件,其中 Quartus-II能進行系統(tǒng)及各邏輯部件的設(shè)計輸入、編譯、仿真、綜合、布局布線,并進行位流文件的下載和配置文件的燒錄,以及使用片內(nèi)邏輯分析儀進行分析和驗證。 在SOPC Builder 中選取系統(tǒng)所需部件,并自動生成每個部件的系統(tǒng)級HDL文件以及支持部件所需的軟件,如驅(qū)動程序、庫文件和一些實用的應(yīng)用程序等,以供軟件開發(fā) 原型用。

通過SOPC Builder軟件包可以定制32位 Nios-II軟核處理器和基本的Nios-II外設(shè)模塊,如 UART控制器,定時器,F(xiàn)LASH控制器, SDRAM制器等。本文設(shè)計的硬件平臺結(jié)構(gòu)如圖3所示。

圖 3所示虛線框內(nèi)硬件部分均是在 FPGA內(nèi)實現(xiàn)

該系統(tǒng)的嵌入式處理器 Nios-II是 Altera 公司推出的一個用戶可配置的16 位或32 位精簡指令集軟核處理器。Nios-II處理器可以配置成最多支持 64個中斷,包括外部硬件中斷、內(nèi)部中斷以及 TRAP(調(diào)試中斷)。Nios-II 處理器可以配置使用 32位內(nèi)部定時器,通過軟件控制寫入控制寄存器的內(nèi)容來獲得定時工作,與一般的定時器工作原理相同,可以產(chǎn)生定時中斷。

Nio-II嵌入式系統(tǒng)中采用 Avalon交換式總線在處理器、外圍設(shè)備和接口電路之間實現(xiàn)網(wǎng)絡(luò)連接,并提供高帶寬數(shù)據(jù)路徑、多路和實時處理能力。 Avalon交換式總線可以通過調(diào)用 SOPC Builder設(shè)計軟件自動生成 。

EDSL Modem的核心部分即主收發(fā)器利用 FPGA中的邏輯單元編寫自定義用戶模塊,并生成自定義 IP核,通過 Avalon總線接口與嵌入式處理器相連。該主收發(fā)器共包括了兩個部分:EDSL成幀模塊和 QAM調(diào)制模塊。

4軟件系統(tǒng)的設(shè)計

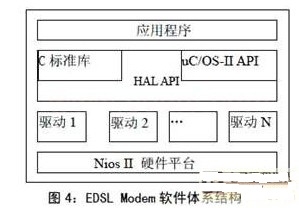

軟件平臺的開發(fā)是在 Altera公司為 Nios-II 系統(tǒng)定制的 Nios-II IDE系統(tǒng)上展開的, Nios-II IDE是基于 Eclipse IDE的集成開發(fā)環(huán)境,用戶可以在 Nios-II IDE中為 Nios II 系統(tǒng)開發(fā)模塊驅(qū)動程序、板級支持包( BSP),以及用戶應(yīng)用程序。考慮到 EDSL Modem 的系統(tǒng)控制和高速數(shù)據(jù)傳輸,在該嵌入式平臺中嵌入了實時嵌入式系統(tǒng) uC/OS-II,整個系統(tǒng)的軟件體系結(jié)構(gòu)如圖4:

其中位于 Nios-II硬件平臺之上的是 EDSL Modem各部件的驅(qū)動程序。其上是硬件抽象層(HAL),它是位于應(yīng)用程序和系統(tǒng)硬件之間的一個系統(tǒng)庫( System Library),在軟件開發(fā)時可以非常方便地使用這些系統(tǒng)庫來與底層硬件通信,而無須關(guān)心的底層硬件實現(xiàn)細節(jié)。HAL API(Application Program InteRFace,應(yīng)用程序接口)集成了 ANSIC 的標(biāo)準庫,它允許應(yīng)用程序使用類似 C庫函數(shù)的方式訪問硬件和文件。

實時嵌入式操作系統(tǒng) uC/OS-II 內(nèi)核工作在 HAL的頂部,有了 HAL這一層,基于 uC/OS-II的程序具有更好的可移植性,而且不受底層硬件改變的影響。

本文介紹了我國擁有自主知識產(chǎn)權(quán)的寬帶接入技術(shù)—— TDD-EDSL,并著重介紹了基于 SOPC的 EDSL Modem的軟硬件實現(xiàn)。在商用 ASIC并不完善的情況下,本文使用了軟硬件均可編程的 Nios-II嵌入式系統(tǒng),縮短了研發(fā)周期,降低了研發(fā)成本。同時 SOPC也代表了以后產(chǎn)品設(shè)計的發(fā)展方向,具有積極的借鑒意義。

-

嵌入式

+關(guān)注

關(guān)注

5138文章

19524瀏覽量

314665 -

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5582瀏覽量

174693 -

操作系統(tǒng)

+關(guān)注

關(guān)注

37文章

7077瀏覽量

124914

發(fā)布評論請先 登錄

基于μC/OS—II的μC/IP協(xié)議棧在ARM系統(tǒng)中的實現(xiàn)

μC/OS-II是什么?μC/OS-II有哪些應(yīng)用?

基于μC/OS-II的嵌入式音頻系統(tǒng)設(shè)計

μC/OS-II 在Nios上的移植

μC OS-II 在Nios 上的移植1

輕型PPP協(xié)議在μC/OS-II操作系統(tǒng)中的實現(xiàn)

基于μC/OS-II的無線調(diào)度策略分析與實現(xiàn)

μC/OS-II在PC機上移植的設(shè)計與實現(xiàn)

基于μC/OS-II的無線監(jiān)控終端設(shè)計與實現(xiàn)

μC/OS-II任務(wù)棧處理的改進設(shè)計

μC/OS-II實時性能測試與分析

μC/OS-II在EP7312上的移植

縮短實時操作系統(tǒng)μC/OS-II中斷關(guān)閉時間的方法

μC/OS-II中縮短中斷關(guān)閉時間方法

基于μC/OS-II和Nios核結(jié)合實現(xiàn)EDSL Modem的軟硬件設(shè)計

基于μC/OS-II和Nios核結(jié)合實現(xiàn)EDSL Modem的軟硬件設(shè)計

評論