單片機P0端口的結構及工作原理

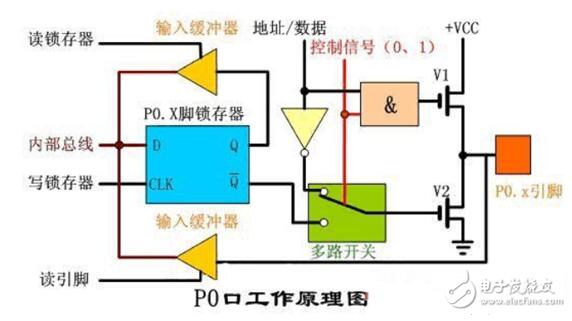

P0端口8位中的一位結構圖見下圖:

由上圖可見,P0端口由鎖存器、輸入緩沖器、切換開關、一個與非門、一個與門及場效應管驅動電路構成。再看圖的右邊,標號為P0.X引腳的圖標,也就是說P0.X引腳可以是P0.0到P0.7的任何一位,即在P0口有8個與上圖相同的電路組成。

單片機端口上拉電阻的作用

顧名思義,上拉就是把電平拉高(一般到電源),下拉就是拉低(一般到地)。上拉主要是為了提高灌電流驅動能力,相當于從電源借點兒功率到IO口,下拉主要是在IO口功率足夠的情況下,為了保護IO口,靜態時為0電平。

對于不同的單片機和端口,上拉電阻的作用不同,最常見的由于內部結構的問題,不能處于懸空狀態。我就以51單片機進行敘述,以其P0口為例,P0口是集電極開路輸出,也就是OC門,這種結構沒有輸出高電平的能力就相當于一個一端接地的開關, 按下去就輸出低電平0V,斷開就沒有電壓,是懸空狀態。至于用不用上拉電阻,取決于外部電路,如果要輸出高電平控制一個器件,而這個器件本身又沒有內置上拉,就必須自己接一個上拉電阻,如果要用低電平控制一個器件,則可以不用加上拉。一般來講,做板子時都會在P0口放一個排阻,10Kohm就可以了。

P0口作為I/O口輸出的時候時,輸出低電平為0 輸出高電平為高組態(并非5V,相當于懸空狀態,也就是說P0 口不能真正的輸出高電平)。給所接的負載提供電流,因此必須接上拉電阻(一電阻連接到VCC),由電源通過這個上拉電阻給負載提供電流。P0作輸入時不需要上拉電阻,但要先置1。因為P0口作一般I/O口時上拉場效應管一直截止,所以如果不置1,下拉場效應管會導通,永遠只能讀到0。因此在輸入前置1,使下拉場效應管截止,端口會處于高阻浮空狀態,才可以正確讀入數據。

單片機p0口為什么要加上拉電阻

P0口內部沒有上拉電阻,是開漏的,不管它的驅動能力多大,相當于它是沒有電源的,需要外部的電路提供,絕大多數情況下P0口是必需加上拉電阻的。

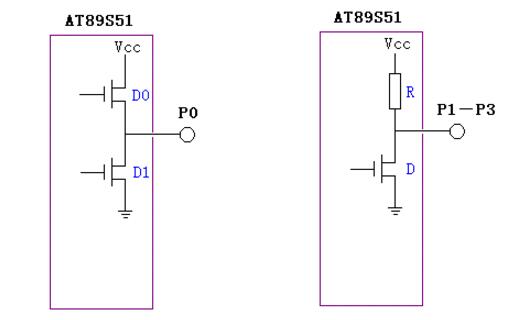

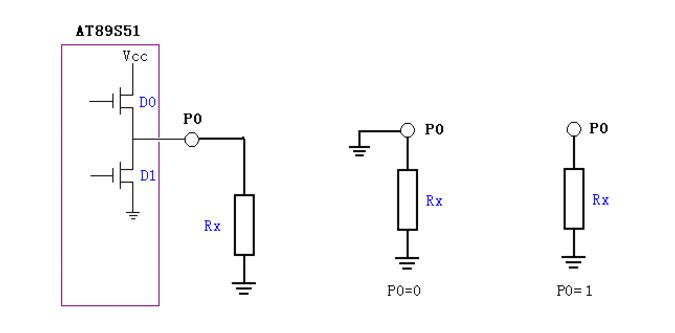

P0口和其它三個口的內部電路是不同的,如下圖:

P0口是接在兩個三極管D0和D1之間的,而P1-P3口的上部是接一個電阻的。P0口的上面那個三極管D0是在進擴展存儲器或擴展總線時使用MOVX指令時才會控制它的導通和截止,在不用此指令時都是截止的。在平常我們使用如:P0_1=0P0_1=1這些語句時控制的都是下面那個三極管D1。

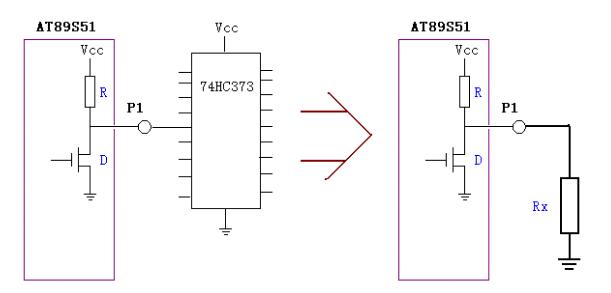

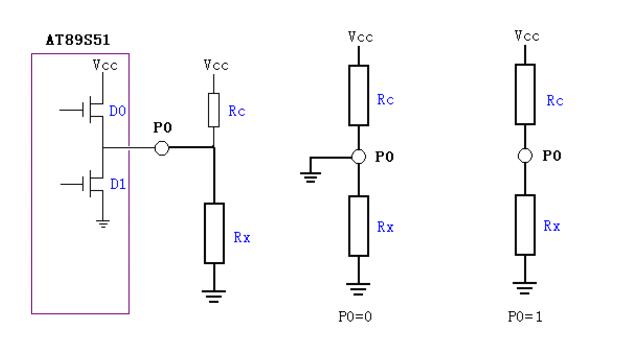

我們先假設P1口接一個74HC373,來看一看它的等效圖

當AT89S51的P1口上接了74HC373后就等于接了一個負載,如上圖右邊。一般來說這些數字電路的輸入阻抗都很大,都在幾百K到上兆歐姆,而P1口內的電阻R一般在幾十K以內。

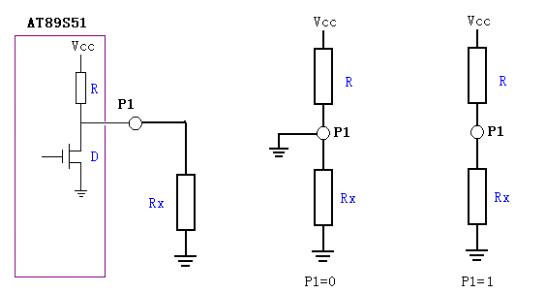

如上圖,當我們發出指令P1=0時,三極管D導通,見中間的等效圖,這時P1點的電位為0。

當發出P1=1的指令后,三極管D截止,見右邊等效圖,因為Rx的阻值要比R的阻值大得多,因此P1點的電位是接近電源電壓的。即高電平。

我們再來看看P0口接負載時的圖

當P0=0時,等效圖是中間的,三極管D1導通,P0點的電位為0。

而當P0=1時,等效圖是右邊的,三極管D1截止,而上面的三極管D0始終是截止的,這樣P0點就等效于懸空了,它處在不穩定狀態,P0點又是RX的高阻抗輸入點,很容易受到外界和周圍電路的干擾從而直接影響到74HC373的輸出狀態。因此就得加上個電阻。如下圖

加上電阻Rc后,電路的狀態就和P1口一樣了,這個電阻Rc就是上拉電阻。

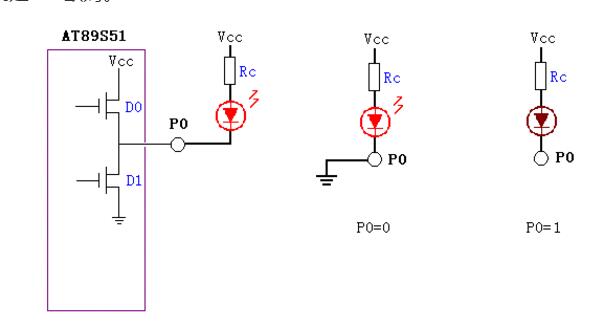

但你如果只是為了讓P0口驅動個發光管,那電路可以直接簡化成下圖那樣。S51內部的電流最好不超過15mA,如果發光管的電壓為2.2V那電阻就是(5-2.2)÷15=0.18K,也就是180歐姆。

當P0=0時P0點為低電位,發光管亮起,流過D1的電流約為15mA。

當P0=1時,P0點為懸空,但發光管和180歐電阻都是低阻抗元件,P點電位就為高電位,再說也無任何輸出影響,因此這樣電路是可以的

-

單片機

+關注

關注

6061文章

44875瀏覽量

646189 -

上拉電阻

+關注

關注

5文章

366瀏覽量

31034

發布評論請先 登錄

STM32F413ZGT6的NRST需要接上拉電阻嗎?

在tpl0102的使用過程中,如果SCL,SDA,沒有接上拉電阻,直接連接到了P1.6 P1.7上,會造成什么后果?

上拉電阻的工作原理詳解

納祥科技NX2069,國產I2C總線8位IO擴展器,遠程 I/O口擴展,替代PCF8574

上拉電阻阻值怎么選擇

I2C總線為什么要接上拉電阻

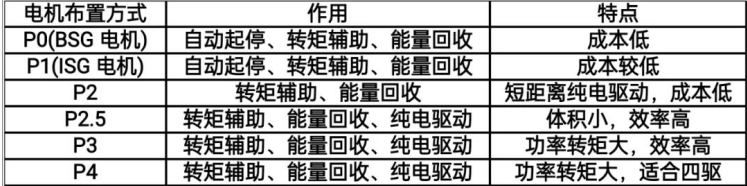

混合動力系統構型P0到P4介紹

p0口為什么接上拉電阻

p0口為什么接上拉電阻

評論