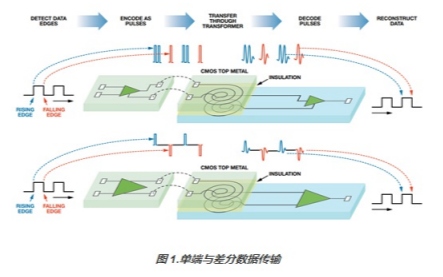

通常情況下,模擬輸入信號(hào)通過高速ADC的量化輸出的數(shù)字信號(hào)需要交給FPGA進(jìn)行處理。如果高速ADC采用LVDS輸出,那么經(jīng)量化處理過的數(shù)字信號(hào)將會(huì)有非常多的LVDS數(shù)據(jù)差分對(duì)。而LVDS數(shù)據(jù)接收端,接收到的LVDS差分?jǐn)?shù)據(jù)對(duì)相互之間可能會(huì)存在非常小的一個(gè)時(shí)間差異,該時(shí)間差異往往是皮秒級(jí)別的,而隨著高速ADC采樣率的提升,目前大多數(shù)的高速ADC采樣速率已經(jīng)達(dá)到GSPS級(jí)別。

因此皮秒級(jí)別的時(shí)間差異也會(huì)對(duì)采集到的數(shù)據(jù)產(chǎn)生影響。這種情況的發(fā)生,往往可能是由于LVDS數(shù)據(jù)差分對(duì)走線長(zhǎng)度的不匹配所造成的,這種數(shù)據(jù)傳輸中的時(shí)間差異對(duì)于高速數(shù)據(jù)傳輸來說,可能會(huì)造成某些數(shù)據(jù)位的值發(fā)生變化,這就相當(dāng)于向FPGA提供了錯(cuò)誤的ADC數(shù)據(jù)。

因此,無論是在高速ADC芯片的測(cè)試評(píng)估還是在其應(yīng)用當(dāng)中,對(duì)這些數(shù)據(jù)傳輸所造成的時(shí)間差異均要進(jìn)行預(yù)先的處理。

數(shù)據(jù)傳輸差異的處理

對(duì)于數(shù)據(jù)傳輸?shù)臅r(shí)間差異可以有兩種方式來解決,一種方法是通過ADC本身的LVDS特性來改變LVDS數(shù)據(jù)傳輸?shù)难舆t,這通常與LVDS的輸出時(shí)鐘有關(guān)。另外一種方法是使用FPGA內(nèi)部的延遲功能來實(shí)現(xiàn)。

ADC內(nèi)部延遲

對(duì)于ADC的LVDS數(shù)據(jù)輸出,可以通過ADC內(nèi)部集成的某些控制來改變輸出時(shí)鐘沿,從而達(dá)到傳輸延遲的目的。這種方式,不能做到有選擇的對(duì)特定的LVDS數(shù)據(jù)差分對(duì)進(jìn)行專門的延遲,但是,只是改變輸出時(shí)鐘沿是可行的。這將有助于改變所有LVDS數(shù)據(jù)差分對(duì)相互之間的傳輸時(shí)間關(guān)系。

FPGA內(nèi)部延遲

另一種解決數(shù)據(jù)傳輸時(shí)間差異的方式,是通過調(diào)節(jié)FPGA內(nèi)部的延遲特性,F(xiàn)PGA對(duì)于每個(gè)LVDS差分對(duì)都有一個(gè)延遲單元。FPGA中有稱之為IDELAY的一個(gè)延遲單元,它可以來用對(duì)每個(gè)LVDS數(shù)據(jù)差分對(duì)分別進(jìn)行延遲調(diào)節(jié)。FPGA的IDELAY非常靈活,可以在ADC輸出到FPGA之間的任何一對(duì)LVDS差分對(duì)之間進(jìn)行調(diào)節(jié)。同樣,由ADC本身所帶來的LVDS數(shù)據(jù)差分對(duì)的時(shí)間偏離,也可以通過FPGA的IDELAY延遲單元來進(jìn)行補(bǔ)償。

IDELAY延遲單元的使用并不是必須的,除非板卡設(shè)計(jì)和布局并沒有進(jìn)行數(shù)據(jù)對(duì)的長(zhǎng)度匹配。

Pattern功能檢查數(shù)據(jù)傳輸錯(cuò)位

為了進(jìn)行設(shè)置和保持時(shí)間的驗(yàn)證,系統(tǒng)設(shè)計(jì)人員可以采用測(cè)試模式來生成可以在FPGA中驗(yàn)證的特定Pattern。在測(cè)試模式下,可以使用用戶自定義的Pattern對(duì)每個(gè)上升沿和下降沿進(jìn)行位翻轉(zhuǎn)。這是用來測(cè)試FPGA和ADC的LVDS數(shù)據(jù)接口之間傳輸狀況的最好方法。

這種測(cè)試方法確定了ADC和FPGA之間傳輸?shù)暮脡摹H绻麥y(cè)試模式數(shù)據(jù)傳輸完美的匹配每個(gè)時(shí)鐘周期的測(cè)試pattern的位翻轉(zhuǎn),那么對(duì)于實(shí)際輸入的設(shè)置和保持時(shí)間即是可信的。如果測(cè)試模式通過,則可以認(rèn)為ADC的LVDS數(shù)據(jù)和FPGA之間的傳輸是合適的。

數(shù)據(jù)傳輸?shù)恼{(diào)整

在pattern測(cè)試模式下,生成的眼圖的連續(xù)的。因此,任何一個(gè)眼圖窗口都可以用來對(duì)數(shù)據(jù)傳輸進(jìn)行校準(zhǔn)。

FPGA內(nèi)部的IDELAY單元可以對(duì)輸出傳輸進(jìn)行微調(diào),以防止由于PCB的走線或FPGA本身代碼編譯時(shí)的時(shí)間約束,造成的數(shù)據(jù)線之間的傾斜。

對(duì)于大多數(shù)高速ADC來說,測(cè)試pattern和數(shù)字化輸入數(shù)據(jù)都來自同一個(gè)LVDS串行模塊,這個(gè)模塊可以維護(hù)輸出時(shí)鐘和輸出數(shù)據(jù)之間的時(shí)間關(guān)系,因此,測(cè)試pattern和正常輸入的數(shù)字化數(shù)據(jù)之間沒有什么差異。但是,如果由于板卡走線,造成輸出數(shù)據(jù)行之間有一定數(shù)量的耦合。那么,如果測(cè)試pattern和實(shí)際輸入信號(hào)量化的數(shù)據(jù)不同于輸出翻轉(zhuǎn)的pattern,時(shí)間可能會(huì)略有不同。

數(shù)據(jù)傳輸調(diào)整的基準(zhǔn)

通常情況下,每一個(gè)ADC的LVDS數(shù)據(jù)差分對(duì)都可以用來作為數(shù)據(jù)傳輸調(diào)整的基準(zhǔn),并以此作為其他LVDS數(shù)據(jù)差分對(duì)的參照來進(jìn)行微調(diào)。

由于數(shù)據(jù)傳輸?shù)牟町悾瑴y(cè)試pattern生成的眼圖并不一定會(huì)是從一個(gè)完整的眼圖起始。因此,如果采用第一個(gè)眼圖來進(jìn)行校準(zhǔn),可能會(huì)出現(xiàn)所有LVDS數(shù)據(jù)輸出差分對(duì)得窗口不相一致。所以,第二個(gè)眼圖窗口將會(huì)是建議的首選,該眼圖必然是完整的采樣窗口。

確定采樣窗口

通常情況下,每對(duì)LVDS差分?jǐn)?shù)據(jù)的傳輸延遲相差不會(huì)太大,因此,我們只需要對(duì)第一對(duì)LVDS差分?jǐn)?shù)據(jù)進(jìn)行分析。如前文所述,第一個(gè)眼圖有可能是不完整的眼圖,因此,我們選擇第二個(gè)眼圖作為參考。

確定調(diào)整起始值

將第一對(duì)LVDS差分輸出的第二個(gè)眼圖的開始時(shí)間值作為參考,當(dāng)作其他所有LVDS差分?jǐn)?shù)據(jù)采樣窗口掃描的起始值,對(duì)所有的LVDS差分?jǐn)?shù)據(jù)進(jìn)行掃描。并與該參考值進(jìn)行比對(duì),計(jì)算出每對(duì)LVDS差分?jǐn)?shù)據(jù)延遲值,并將該延遲通過IDELAY單元加在ADC的LVDS數(shù)據(jù)差分輸出和FPGA之間。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613983 -

數(shù)據(jù)傳輸

+關(guān)注

關(guān)注

9文章

2002瀏覽量

65663 -

adc

+關(guān)注

關(guān)注

99文章

6635瀏覽量

548223

原文標(biāo)題:高速AD中的LVDS和FPGA

文章出處:【微信號(hào):ALIFPGA,微信公眾號(hào):FPGA極客空間】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

無線數(shù)據(jù)傳輸模塊的實(shí)際應(yīng)用

DMA進(jìn)行數(shù)據(jù)傳輸和CPU進(jìn)行數(shù)據(jù)傳輸的疑問

數(shù)據(jù)傳輸介質(zhì)

基于FPDP的高速數(shù)據(jù)傳輸系統(tǒng)設(shè)計(jì)

IDE數(shù)據(jù)傳輸模式

Modem數(shù)據(jù)傳輸標(biāo)準(zhǔn)

RAID卡的數(shù)據(jù)傳輸速度

數(shù)據(jù)傳輸,數(shù)據(jù)傳輸的工作方式有哪些?

數(shù)據(jù)傳輸速率是什么意思

差異數(shù)據(jù)傳輸有什么區(qū)別?

單端與差異數(shù)據(jù)傳輸到底有什么區(qū)別

數(shù)據(jù)傳輸差異的處理

數(shù)據(jù)傳輸差異的處理

評(píng)論