當前的生活節奏越來越快,對計算處理器的要求也越來越高。即使是有摩爾定律的限制,人們仍然希望在單個芯片中塞入盡可能多的晶體管。盡管現在的MCU動不動就可以跑到幾十上百兆,比如NXP高能效的LPC54100系列已破100MHz大關,通用型的LPC54600系列飚到210MHz,i.MX RT1050跨界處理器甚至飛到了怪獸級的600MHz,可是在當下應付圖像處理和機器學習等計算大戶時,仍然免不了出現“卡”的窘境。這個時候,如果能清楚地知道最消耗性能的具體函數,就有機會制定優化性能的策略。這也是圈子里常說的“profiling”(性能分析)。

有些價格相當昂貴的專業軟硬件開發工具,都會提到它們有多么超強的profiling能力,這仿佛讓人覺得profiling是有錢人才能玩得起,難道作為廣大工程師我們就只能縮手縮腳嗎?其實不然,在軟件上想一點變通的辦法,使用最便宜的仿真器,就完全可以在極小的開銷下,做到好用夠用的強大profiling利器,丑小鴨秒變金鳳凰。

下面要介紹的方法的基本思想,就是密集地定期采集PC寄存器的值,從它的概率分布上估計最占CPU的函數。采集得越久,就越接近真實情況(大數定率)。其原理是,在Cortex-M系MCU進入中斷/異常時,會自動把被打斷的位置(PC)存儲在堆棧中。這樣我們可以用匯編寫一小段入口程序,讀取出入棧的PC數值,作為參數傳遞給處理程序的C程序主體,在主體中統計PC樣本的規律。只要采集了足夠久的樣本,在概率論的大數定理支持下,咱們就有信心估計程序中PC最常出現的位置,也就是最占CPU時間的函數。

為了貫徹這個思想,需要準備的只有:

1.工具鏈產生的 .map文件。無論是KEIL, IAR, GCC,在成功構建程序后,都會產生一個map文件來記錄各函數和變量的位置。從采集的PC位置,查map文件判定是什么函數。

2.系統中有一個定期產生中斷的時基。常見的就是SysTick定時器的周期中斷,別的timer也可以。這個中斷需要優先級比較高。

3.擴寫定時器中斷服務程序,按照前面的思路,加入這個屌絲神器。

這樣,我們就可以把占CPU最多的計算型函數請到VIP區,它們與CPU有綠色快速通道,加速它們的執行。其實這個VIP區也是分等級的,從小V到大V,特權待遇相差還是明顯的,小編今后再專開一文介紹不同VIP的特權。

要想讓這個思路能可靠工作,還有幾個關鍵的小坑不要踩:

1.PC最常在的位置并非一定就是最計算密集的位置。比如,程序中經常會出現等候外設寄存器的情況,CPU幾萬幾億遍地查看一個外設標志。這類IO忙等的代碼即使放在大V區,也無濟于事。

2.定時器中斷的優先級不夠高。如果有高優先級的中斷服務程序占用了大量CPU時間,定時器中斷就沒有機會采集到它們,反而是在這些中斷返回時定時器中斷才得到服務,結果反而冤枉了被高優先級中斷給打斷的位置。

3.某個函數的工作頻率與相位恰好和定時器中斷產生“共振”,經常有機會在進入定時器中斷的前夕在這個函數中,也會誤以為這個函數是最占CPU時間的。這個情況一般是罕見的。

4.CPU負載比較輕,結果大量PC都采集到idle函數中。可能有小伙伴要問了,CPU都這么咸(閑)了,還淡操什么心?這個其實要以發展的眼光來看。比如,有可能隨著功能集成的增加CPU終將有不堪重負的時候,或者系統負載不均勻而表現出明顯的峰谷性,又可能希望讓CPU盡管做完事好進低功耗模式。

-

芯片

+關注

關注

459文章

52145瀏覽量

435993 -

mcu

+關注

關注

146文章

17824瀏覽量

360236

原文標題:證明你的MCU夠強,有時不需要昂貴開發工具!

文章出處:【微信號:mcuworld,微信公眾號:嵌入式資訊精選】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

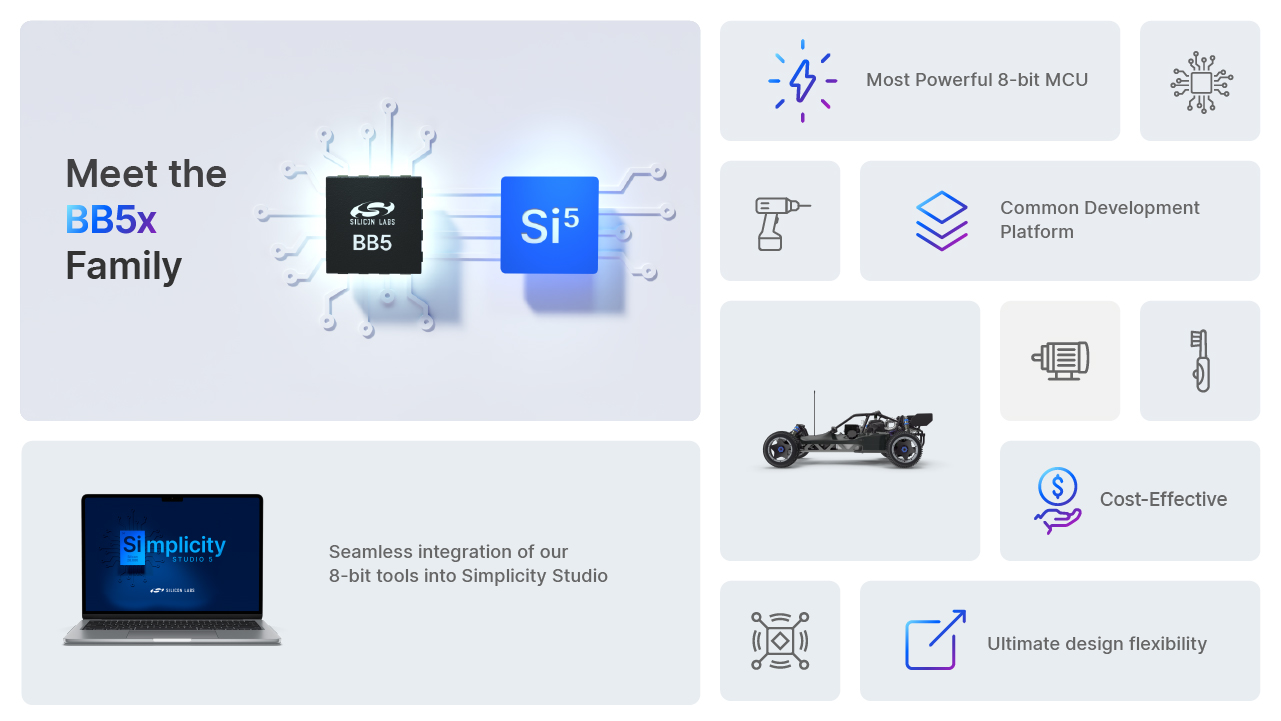

芯科科技推出新的8位MCU系列產品,擴展其強大的MCU平臺

請問用算力強大的SOC來控制汽車是不是能夠大幅減少MCU的使用數量?

莫名被戳中的“不只是”體

莫名被戳中的“不只是”體

復旦微MCU強大的串口功能

為什么你的MCU不支持SDRAM呢

用了這么多年的MCU,你知道哪些MCU原廠最牛?

用了這么多年的MCU,你知道哪些MCU原廠最牛?

你的MCU不只這么強大

你的MCU不只這么強大

評論