聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

鎖相環(huán)

+關(guān)注

關(guān)注

35文章

592瀏覽量

88423 -

Altera

+關(guān)注

關(guān)注

37文章

799瀏覽量

155381

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

什么是鎖相環(huán) 鎖相環(huán)的組成 鎖相環(huán)選型原則有哪些呢?

大家都知道鎖相環(huán)很重要,它是基石,鎖相環(huán)決定了收發(fā)系統(tǒng)的基礎(chǔ)指標(biāo),那么如此重要的鎖相環(huán)選型原則有哪些呢?

鎖相環(huán)在電力系統(tǒng)中的應(yīng)用

鎖相環(huán),而他們都是屬于軟件鎖環(huán)的范疇。在電力仿真軟件中,一般都有PLL模塊,只需要將該模塊應(yīng)用一下即可實(shí)現(xiàn)

發(fā)表于 01-04 22:57

Cyclone IV 動(dòng)態(tài)重配置

和 ALTPLL_RECONFIG 控制器實(shí)例來(lái)對(duì)物理介質(zhì)附加子層(PMA) 控制、物理代碼子層 (PCS)、 多用鎖相環(huán) (PLL) 以及通用鎖相環(huán) (PLL) 進(jìn)行重配置。

發(fā)表于 11-14 10:53

基于TRAC器件的鎖相環(huán)設(shè)計(jì)研究

以TRAC020LH 完全可重配置模擬器件和TRAC 開(kāi)發(fā)軟件為基礎(chǔ),設(shè)計(jì)模擬鎖相環(huán);給出仿真結(jié)果和利用PIC 單片機(jī)對(duì)器件進(jìn)行配置的應(yīng)用電路。該鎖相環(huán)成功應(yīng)用于逆變器的頻率跟蹤,性能

發(fā)表于 04-15 11:42

?11次下載

基于TRAC 器件的鎖相環(huán)設(shè)計(jì)研究

以TRAC020LH 完全可重配置模擬器件和TRAC 開(kāi)發(fā)軟件為基礎(chǔ),設(shè)計(jì)模擬鎖相環(huán);給出仿真結(jié)果和利用PIC 單片機(jī)對(duì)器件進(jìn)行配置的應(yīng)用電路。該鎖相環(huán)成功應(yīng)用于逆變器的頻率跟蹤,性能

發(fā)表于 05-15 15:38

?6次下載

鎖相環(huán)技術(shù)在頻率跟蹤中的應(yīng)用研究

本文介紹鎖相環(huán)及其頻率跟蹤的基本原理,給出二階鎖相環(huán)和四階鎖相環(huán)的設(shè)計(jì)依據(jù)。在此基礎(chǔ)上,對(duì)四階鎖相環(huán)實(shí)現(xiàn)頻率跟蹤的轉(zhuǎn)換時(shí)間進(jìn)行了仿真,就如何

發(fā)表于 07-29 16:28

?44次下載

基于TRAC器件的鎖相環(huán)設(shè)計(jì)研究

摘要: 以TRAC020LH完全可重配置模擬器件和TRAC開(kāi)發(fā)軟件為基礎(chǔ),設(shè)計(jì)模擬鎖相環(huán);給出仿真結(jié)果和利用PIC單片機(jī)對(duì)器件進(jìn)行配置的應(yīng)用電路。該鎖相環(huán)成功應(yīng)用于逆變

發(fā)表于 06-20 11:48

?1164次閱讀

鎖相環(huán)

鎖相環(huán)英文為PLL,即PLL鎖相環(huán)。可以分為模擬鎖相環(huán)和數(shù)字鎖相環(huán)。兩種分類的鎖相環(huán)原理有較大區(qū)別,通過(guò)不同的

發(fā)表于 10-26 12:40

詳解FPGA數(shù)字鎖相環(huán)平臺(tái)

一、設(shè)計(jì)目標(biāo) 基于鎖相環(huán)的理論,以載波恢復(fù)環(huán)為依托搭建數(shù)字鎖相環(huán)平臺(tái),并在FPGA中實(shí)現(xiàn)鎖相環(huán)的

發(fā)表于 10-16 11:36

?19次下載

在 Arria 10 中實(shí)現(xiàn) I/O 鎖相環(huán)動(dòng)態(tài)相移的方法

如何在 Arria 10 中實(shí)現(xiàn) I/O 鎖相環(huán) (

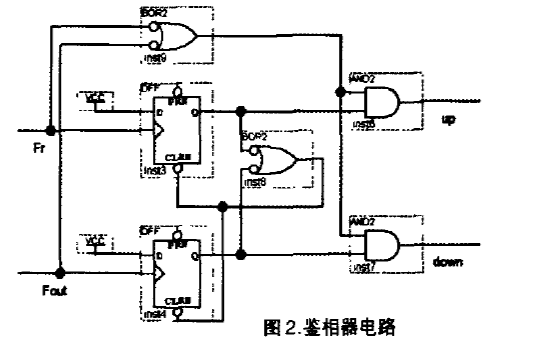

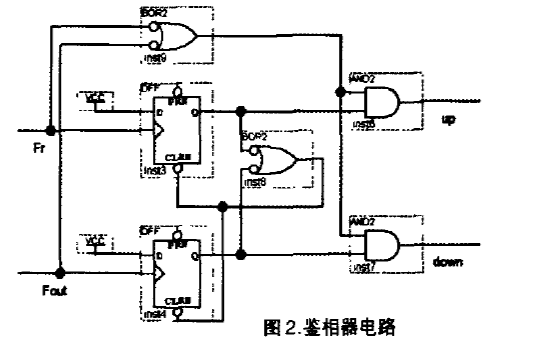

如何使用FPGA實(shí)現(xiàn)高性能全數(shù)字鎖相環(huán)的設(shè)計(jì)

本文提出了一種適用范圍廣泛的全數(shù)字鎖相環(huán)(ADPLL)實(shí)現(xiàn)方法.在鎖相環(huán)輸入頻率未知的情況下,實(shí)現(xiàn)

發(fā)表于 01-26 15:03

?65次下載

如何使用FPGA實(shí)現(xiàn)高性能全數(shù)字鎖相環(huán)的設(shè)計(jì)

本文提出了一種適用范圍廣泛的全數(shù)字鎖相環(huán)(ADPLL)實(shí)現(xiàn)方法.在鎖相環(huán)輸入頻率未知的情況下,實(shí)現(xiàn)

發(fā)表于 01-26 15:03

?20次下載

鎖相環(huán)是如何實(shí)現(xiàn)倍頻的?

信號(hào)倍頻。在本文中,我們將詳細(xì)探討鎖相環(huán)如何實(shí)現(xiàn)倍頻。 鎖相環(huán)的基本原理 在介紹鎖相環(huán)如何

pll鎖相環(huán)的作用 pll鎖相環(huán)的三種配置模式

pll鎖相環(huán)的作用 pll鎖相環(huán)的三種配置模式? PLL鎖相環(huán)是現(xiàn)代電子技術(shù)中廣泛應(yīng)用的一種電路,它的作用是將一個(gè)特定頻率的輸入信號(hào)轉(zhuǎn)換為固定頻率的輸出信號(hào)。PLL

鎖相環(huán)在相位檢測(cè)中的應(yīng)用

鎖相環(huán)在相位檢測(cè)中的應(yīng)用? 鎖相環(huán)(PLL)是一種電子技術(shù)中廣泛應(yīng)用的電路,用于調(diào)整一個(gè)輸出信號(hào)的相位來(lái)精確匹配一個(gè)參考信號(hào)。鎖相環(huán)

在 Arria 10 中實(shí)現(xiàn) I/O 鎖相環(huán)重配置的方法

在 Arria 10 中實(shí)現(xiàn) I/O 鎖相環(huán)重配置的方法

評(píng)論