在當今世界,互聯網數據流量不斷上升,移動設備的使用也呈爆炸式的增長,對于處理快速增長的數據和視頻數據流量的電信基礎設施的需求變得越來與具有挑戰性。根據思科可視網絡互聯指數全球IP流量預測,2014-2019,到2018年,全球將有40億互聯網用戶(超過世界人口的51%),以及210億個聯網設備和連接數量。

25千兆以太網 (25GbE) 正在快速發展,并且很多分析人士預計它將在未來4年中呈現指數性的迅速增長。想象一下設計有線網絡設備來支持過多標準,以及用最小數據包損失和延遲來快速提升數據速率時的復雜程度!

隨著數據速率的增加,鏈路抖動允許量變得越來越嚴格。硬件工程師將主要精力放在如何使他們的整個線路卡能夠支持最大吞吐量,而為基準時鐘產生的隨機抖動分配盡可能小的允許量。針對基準時鐘,對于一條25GbE的鏈路(集成范圍在12kHz至20MHz之間)來說,可以實現的最大可能均方根 (RMS) 抖動的范圍在100fs至300fs之間。這個12kHz-20MHz的標準相位噪聲集成范圍包括鎖相環 (PLL) 頻帶內和頻帶外 (VCO) 噪聲的影響。基準時鐘發生器的相位噪聲性能需要在PLL環路帶寬內和帶寬外都表現得很出色,以符合更加嚴格的抖動技術規格要求。

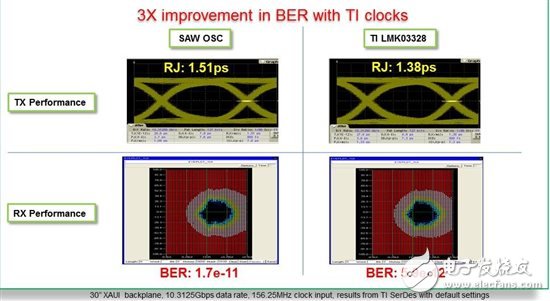

例如,LMK03328在多個集成帶寬內提供業內最低相位噪底,一致的RMS抖動。超低相位噪聲和抖動轉化為串行鏈路內更好地比特誤差率 (BER)。考慮一下對傳統高端基于表面聲波的示波器的改進。圖1顯示的是,在一條具有156.25MHz基準時鐘的10G鏈路上,相對于一個SAW示波器,在使用LMK03328時,BER性能提高了3倍。隨著進一步的優化,你可以實現更高的性能—最多比傳統SAW示波器高9倍。

圖1:SAW示波器和TI LMK03328的10G鏈路性能

一個低相位噪聲基準時鐘轉化為串行鏈路中其它關鍵塊的更高抖動允許量分配。隨著數據速率快速爬升到25GbE,并且允許的BER在1e-18時變為標準值,高質量、低抖動基準時鐘在保護信號完整性方面的重要性變得不可小覷。

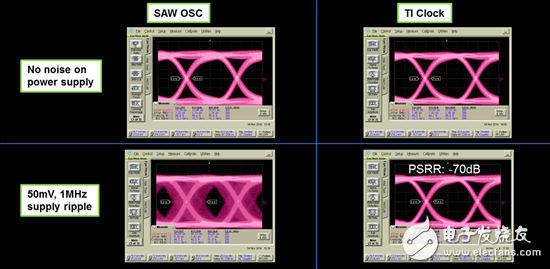

在用一個眼圖來解決鏈路無法正常運行的問題后,你現在需要確保你的設計是穩健耐用的,并且在應力下可以正常運行。使信號完整性變得更加糟糕的常見問題就是電源抖動。將低壓降穩壓器 (LDO) 集成在內可以極大地幫助克服對電源噪聲的敏感度。具有內置LDO的時鐘發生器通過提供穩健耐用的電源噪聲抑制和出色的電源抑制比 (PSRR) 來幫助改進無錯數據傳輸。圖2顯示的是使用LMK03328時對PSRR和TX眼圖性能的改進,其原因就在于LMK03328集成了一個LDO。

圖2:SAW示波器和TI LMK03328時鐘發生器的PSRR

-

示波器

+關注

關注

113文章

6527瀏覽量

188134 -

以太網

+關注

關注

40文章

5582瀏覽量

174686

發布評論請先 登錄

請問通過ADC32RF42 EVM GUI能直接配置出lmk04828的14路時鐘嗎?

LMK1D1208低附加抖動、八路LVDS輸出時鐘緩沖器評估板

用PLLatinum設計LMK03328環路濾波器遇到的疑問求解

請問用ADC32RFXX EVM GUI界面能直接調出LMK04828輸出的4路時鐘嗎?

LMK04828SNKDTEPEP和LMK04828BISQ的區別是什么?

LMK00725是否支持LVDS或者LVPECL的差分交流耦合輸入呢?

怎樣才能讀取LMK03328的工作狀態,例如PLL2是否失鎖?

LMK04828-EP為什么沒有時鐘信號輸出?

LMK03328使用Code Loader 4,輸入25M晶振請問如何配置輸出HCSL電平?

適用于LMK6D、LMK6P和LMK6H BAW振蕩器的通用焊盤圖案

LMK03002/LMK03002C精密時鐘調節器數據表

具有兩個獨立PLL、八路輸出、集成EEPROM的LMK03328超低抖動時鐘發生器數據表

LMK5B33414 4路輸入、14 路輸出 3 DPLL、3 APLL網絡同步器數據表

LMK5B33216 3 DPLL、3 APLL、2路輸入、16路輸出網絡同步器數據表

SAW示波器和LMK03328的鏈路設計

SAW示波器和LMK03328的鏈路設計

評論