本文翻譯轉(zhuǎn)載于:Cadence Blog

作者:Vishnu Teja S

大家是否想過,我們的智能手機(jī)為何能夠拍攝出令人驚嘆的照片、播放清晰悅耳的音樂或是準(zhǔn)確測量心率?

答案就藏在模擬集成電路(IC)設(shè)計(jì)領(lǐng)域。模擬電路在電子技術(shù)中發(fā)揮著至關(guān)重要的作用,負(fù)責(zé)處理連續(xù)信號(hào),而這些連續(xù)信號(hào)構(gòu)成了現(xiàn)代世界的支柱。此外,模擬 IC 設(shè)計(jì)將藝術(shù)與科學(xué)完美融合,工程師通過精心設(shè)計(jì)電子電路來處理連續(xù)信號(hào)。在設(shè)計(jì)過程中,他們需要綜合考量各種因素,包括進(jìn)行大量的調(diào)整、優(yōu)化以及一些迭代任務(wù)。

在本文中,我們將探討模擬 IC 設(shè)計(jì)流程的各個(gè)階段,并重點(diǎn)介紹每個(gè)步驟中使用的 Cadence 工具。

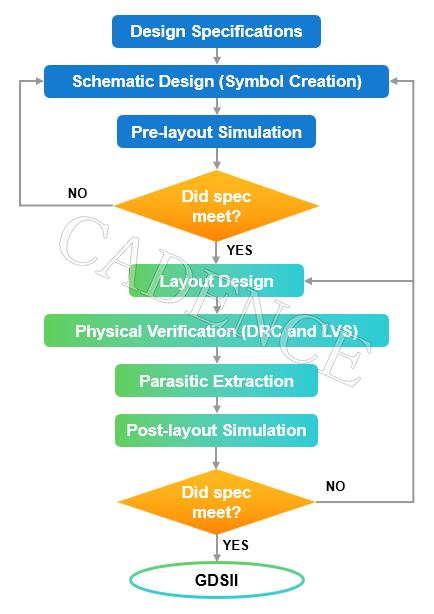

模擬 IC 設(shè)計(jì)流程

模擬 IC 設(shè)計(jì)是一個(gè)將概念轉(zhuǎn)化為高性能物理芯片的迭代過程。以下是其中涉及的每個(gè)階段。

模擬 IC 設(shè)計(jì)流程

設(shè)計(jì)規(guī)范:奠定基礎(chǔ)

模擬 IC 設(shè)計(jì)流程的第一步是定義規(guī)范,包括性能指標(biāo)、功耗和面積限制。明確了解這些要求是順利開展后續(xù)設(shè)計(jì)階段的關(guān)鍵。

原理圖設(shè)計(jì)和符號(hào)創(chuàng)建:賦予設(shè)計(jì)生命

下一階段是使用Virtuoso Schematic Editor創(chuàng)建原理圖設(shè)計(jì)和符號(hào),借助這一工具,可以輕松、準(zhǔn)確地創(chuàng)建和編輯原理圖。

布線前仿真:驗(yàn)證功能和性能

版圖前仿真對于驗(yàn)證電路的功能和性能至關(guān)重要。Cadence Spectre Circuit Simulator用于進(jìn)行電路仿真,而Virtuoso ADE Explorer 和 Virtuoso ADE Assembler提供用戶友好的界面。這些工具可幫助設(shè)計(jì)師在版圖階段之前發(fā)現(xiàn)和修復(fù)潛在問題。

版圖設(shè)計(jì):將原理圖轉(zhuǎn)化為現(xiàn)實(shí)

在此階段,原理圖被轉(zhuǎn)換為物理版圖。每個(gè)晶體管都經(jīng)過精心排布,以優(yōu)化布線和面積。Virtuoso Layout Suite具有創(chuàng)新的自動(dòng)布局布線功能,大大加快了版圖設(shè)計(jì)過程。

物理驗(yàn)證:確保設(shè)計(jì)完整性

物理驗(yàn)證是一個(gè)關(guān)鍵步驟,包括使用Pegasus Verification System執(zhí)行 DRC(設(shè)計(jì)規(guī)則檢查)和 LVS(實(shí)體與邏輯)檢查。借助適用于Virtuoso Studio的全新iPegasus Verification System,設(shè)計(jì)人員能夠在Virtuoso Layout Suite中無縫運(yùn)行物理驗(yàn)證檢查。

寄生參數(shù)提取:精確建模以實(shí)現(xiàn)最佳性能

寄生參數(shù)提取涉及從版圖中識(shí)別寄生元件并為其建模,以確保最佳性能。Cadence Quantus Extraction Solution可高精度地完成這一任務(wù),幫助設(shè)計(jì)人員優(yōu)化設(shè)計(jì),進(jìn)而獲得良好的成果。

版圖后仿真:功能和性能的最終檢查

在提取的版圖視圖上進(jìn)行版圖后仿真,對功能和性能進(jìn)行最終檢查。設(shè)計(jì)人員可以重復(fù)使用版圖前仿真中的相同設(shè)置,確保設(shè)計(jì)流程順暢且高效。

流片:準(zhǔn)備投產(chǎn)

最后階段是生成用于制造的 GDSII 文件。芯片完成制造并經(jīng)過質(zhì)量檢驗(yàn)后,即可投入市場。

通過遵循這一全面的模擬 IC 設(shè)計(jì)流程,設(shè)計(jì)人員可以利用 Cadence 工具的強(qiáng)大功能,創(chuàng)建高性能、可靠且高效的模擬 IC。無論您是經(jīng)驗(yàn)豐富的設(shè)計(jì)師還是剛?cè)腴T的初學(xué)者,該流程均可為您提供清晰的路線圖,助您在復(fù)雜的模擬 IC 設(shè)計(jì)領(lǐng)域取得成功。

-

模擬IC

+關(guān)注

關(guān)注

8文章

174瀏覽量

29923 -

IC設(shè)計(jì)

+關(guān)注

關(guān)注

38文章

1354瀏覽量

105466 -

Cadence

+關(guān)注

關(guān)注

67文章

968瀏覽量

144082

原文標(biāo)題:模擬 IC 技術(shù)志|從概念到現(xiàn)實(shí):了解 Cadence 模擬 IC 設(shè)計(jì)流程

文章出處:【微信號(hào):gh_fca7f1c2678a,微信公眾號(hào):Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Giantec采用Cadence技術(shù)統(tǒng)一數(shù)字流程生產(chǎn)其混合信號(hào)芯片

基于Cadence的IC設(shè)計(jì)

Cadence助力Denso大幅提升IC設(shè)計(jì)效率

TSMC 和 Cadence 合作開發(fā)3D-IC參考流程以實(shí)現(xiàn)真正的3D堆疊

Cadence數(shù)字和定制/模擬設(shè)計(jì)流程獲得TSMC最新N3E和N2工藝技術(shù)認(rèn)證

Cadence 數(shù)字和定制/模擬設(shè)計(jì)流程獲得 Samsung Foundry SF2 和 SF3 工藝技術(shù)認(rèn)證

Cadence數(shù)字和定制/模擬流程通過Samsung Foundry的SF2、SF3工藝技術(shù)認(rèn)證

Cadence 數(shù)字、定制/模擬設(shè)計(jì)流程通過認(rèn)證,Design IP 現(xiàn)已支持 Intel 16 FinFET 制程

淺談Cadence模擬IC設(shè)計(jì)流程

淺談Cadence模擬IC設(shè)計(jì)流程

評論